鈮酸鋰薄膜調制器的研究進展

劉海鋒,郭宏杰,2,譚滿清,2 ,李智勇

(1. 中國科學院半導體研究所 集成光電子學國家重點實驗室,北京 100083;2. 中國科學院大學 材料科學與光電技術學院,北京 100049)

1 引 言

在不斷增長的物聯網業務和大數據交互需求的共同推動下,要求光調制器具備大帶寬、小體積、低光學損耗、低能耗、高集成度的特點。鈮酸鋰[1](Lithium Niobate,LN)材料制作的調制器與硅[2-3](Silicon,Si)、磷 化 銦[4](Indium Phosphide,InP)、聚合物[5](Polymers)、等離子體[6](Plasmonics)等材料制作的調制器相比,除了具有體積小、帶寬高和損耗低的優點,還有良好的線性度以及較高的消光比[7-8]。

目前商用的LN調制器為使用質子交換(Proton Exchange,PE)工藝或者Ti擴散(Titanium-indiffusion)工藝制作的體波導器件,PE和Ti擴散工藝制備的波導折射率差Δn≈0.02,由于波導對光的限制能力較弱,故體波導器件往往體積大并且調制電壓較高。國內外商用LN調制器的帶寬在35 GHz以下,同時半波電壓大于4 V,調制器長度大于5 cm[9-11]。近些年,隨著波導加工工藝不斷成熟,LN薄膜(Thin Film LN,TFLN)實現波導折射率差Δn>0.7,增強了波導對的光的限制能力,在減小調制器的體積的同時降低了調制電壓。在最近的報道中,利用LN薄膜結構制備了調制帶寬>100 GHz,半波電壓與長度乘積VπL<2 V?cm[12-13]的調制器,其性能在大多數方面優于目前商用鈮酸鋰調制器。LN薄膜調制器成為實現小型化、高帶寬、低損耗、高集成度調制器的熱門方案。

LN薄膜調制器由波導結構、耦合結構、電極結構3部分構成。波導結構影響調制器帶寬、調制電壓、調制長度、消光比、傳輸損耗等性能,耦合結構影響調制器的耦合損耗,電極結構影響調制器的調制帶寬。根據應用場景不同,LN薄膜調制器分為強度調制器和相位調制器。強度調制器主要應用于長距離光纖通信領域,對調制器的帶寬、體積、功耗要求較高,因此LN薄膜波導結構和電極結構在強度調制設計中較為關鍵。相位調制器主要應用于光纖傳感和短距通信領域,調制器需要實現低調制電壓、小體積、高消光比,因此需要重點關注LN薄膜調制器的波導結構和波導制作工藝。

本文對LN薄膜調制器的耦合結構、波導結構、電極結構的研究進展進行了詳細梳理,對波導制作工藝進行了總結,并分析了不同結構調制器的性能,最后對LN薄膜調制器的發展趨勢和應用前景進行了展望。

2 LN薄膜調制器結構研究進展

2.1 波導結構研究進展

2.1.1 薄膜平臺結構

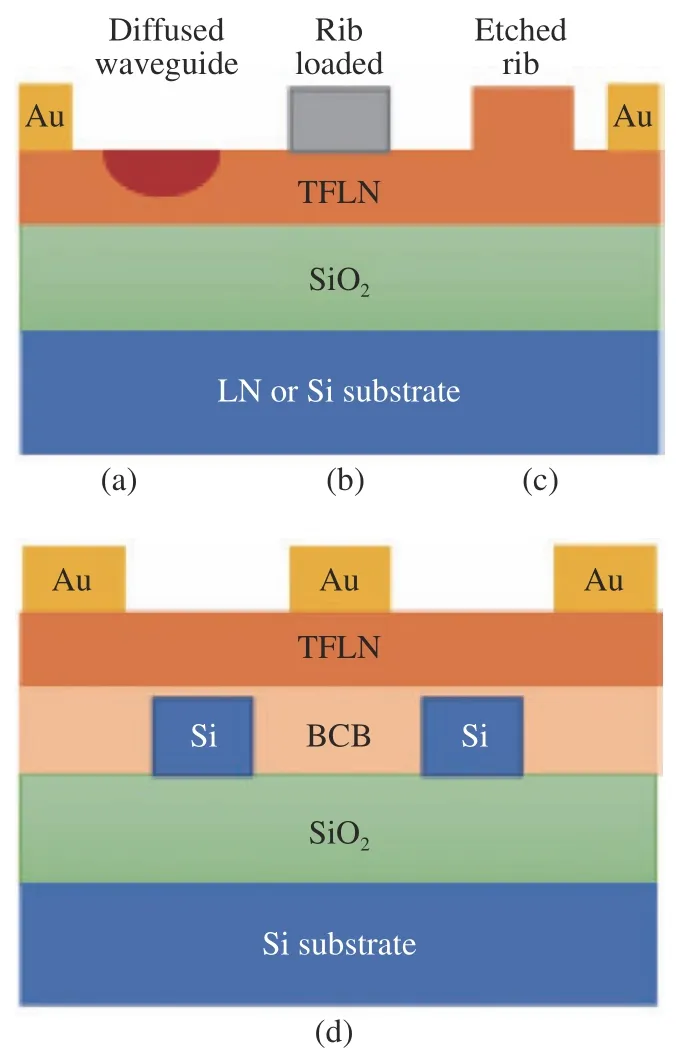

LN薄膜波導根據薄膜平臺主要分為兩大類:一類為絕緣體上鈮酸鋰薄膜(Lithium Niobate on Insulator,LNOI),另一類為絕緣體上硅(Silicon on insulator,SOI)。LNOI波導根據波導層工藝不同分為置換波導、加載波導和脊形波導,波導結構如圖1所示。

圖1 (a)~(c)LNOI結構:(a)置換波導;(b)加載波導;(c)脊形波導。(d)SOI結構Fig. 1 (a)~(c) LNOI structure: (a) diffused waveguide;(b) loaded waveguide; (c) ridge waveguide. (d) SOI structure

2.1.2 光學結構

LN薄膜波導使用的光學結構主要有相位型、干涉型和諧振腔型,其中干涉型和諧振腔型為強度調制。干涉型有馬赫-曾德爾干涉(Mach-Zehnder Interferometer,MZI)結構和邁克耳孫干涉(Michelson Interferometer,MI)結構。MI相比于MZI增加了光干涉長度,進而縮小了調制器的體積,其結構如圖2所示。諧振腔型有微環(Micro-Ring Resonator,MRR)結構和光子晶體(Photonic Crystal,PHC)結構,光子晶體的Q值可以大于105,相比微環提高了1~2個數量級[14-15],其結構模型如圖3(彩圖見期刊電子版)所示[16]。

圖2 (a) MZI結構示意圖;(b) MI結構示意圖Fig. 2 Schematic diagrams of (a) MZI structure and (b) MI structure

圖3 兩種諧振腔輸出端口光強分布圖[16]。(a)微環結構;(b)光子晶體結構。藍線為施加電場后波導的光學特性變化曲線Fig. 3 Light intensity distribution diagram of the output port of the resonant cavity structure waveguide[16]. (a) Microring structure; (b) photonic crystal structure. The blue line is the optical characteristic change curve of the waveguide after an electric field is applied

2.2 耦合結構研究進展

為了匹配光纖與波導之間的光模式,需要相匹配的耦合技術降低損耗[17-18]。傳統的耦合技術有邊緣耦合(Edge coupling),光柵耦合(Gratecoupling)和消逝耦合(Evanscent coupling)3種,其模型結構如圖4所示[19]。

圖4 (a)錐形耦合模型[19];(b)反錐形耦合模型[19];(c)光柵耦合模型[19];(d)消逝耦合模型[19]Fig. 4 (a) Tapered coupling model[19]; (b) inverse tapered coupling model[19]; (c) grating coupling model[19]; (d) evanescent coupling model[19]

邊緣耦合方案有錐形波導(Tapered waveguides) (如圖4(a))和反錐形波導(Inversely tapered waveguides) (如圖4(b))兩種結構。錐形結構可以實現1.5 dB/facet (TE)和 1.75 dB/facet (TM)的耦合損耗,但是制作難度大[20]。反錐形結構降低了制作難度,但帶來了較大的耦合損耗[21]。為了提升耦合效率,反錐形結構和棱鏡光纖配合使用,耦合損耗減小到(2.5±0.5) dB/face (TE)和6 dB/facet(TM)[22]。此外,研究者們還提出了一種新的反錐形耦合方案(雙錐形結構)[23-24]。在脊形結構減小時,傳統的單錐形結構會使得光向薄膜層轉移,從而導致耦合效率變差,而雙錐形結構可以使得光的模式很好地接近圓形,耦合損耗減小到0.5 dB/facet[25]。

光柵耦合模型如圖4(c)所示,相較于邊緣耦合,光柵耦合的優勢在于制造工藝成熟,但制作過程中需要考慮光在襯底中的傳播損耗,故耦合效率較低(3.5 dB/facet)[26-27]。

消逝耦合模型如圖4(d)所示,其理論耦合效率可以達到100%。Yao[28]提出的基于LNOI的漸逝耦合方案實現了1.32 dB/facet (TE)和1.88 dB/facet (TM)的耦合損耗。

此外,Wang[29]提出將光纖集成到調制器中的新型耦合方案,其結構如圖5(彩圖見期刊電子版)所示[29],通過對比表1可得,該新型的結構實現了較小的耦合損耗,為集成光電子提供了新穎的思路。

圖5 光纖與調制器集成方案[29]。(a)調制器結構;(b)光在光纖中傳播時的波導結構;(c)光在波導中傳播時的波導結構Fig. 5 Optical fiber and modulator integration scheme[29].(a) Modulator structure; (b) waveguide structure when light propagates in an optical fiber; (c) waveguide structure when light propagates in a waveguide

表1 不同耦合方案總結Tab. 1 Summary of different coupling schemes

2.3 電極結構研究進展

在鈮酸鋰調制器中,電極有如圖6所示兩種基礎結構,圖6(a)中波導置于兩個電極之間,該結構適用X切Y傳或Y切X傳晶體傳輸TE單模光,圖6(b)中波導置于電極之下,該結構適用X切晶體傳輸TM單模光。當波導置于電極下時,為了避免光在電極中產生損耗,需要在波導和電極之間增加緩沖層。

圖6 鈮酸鋰調制器中的電極基礎結構。 (a)電場方向平行波導芯層;(b)電場方向垂直波導芯層Fig. 6 Electrode basic structure of LN modulators. (a) The electric field direction is parallel to the waveguide core; (b) the electric field direction is perpendicular to the waveguide core

根據傳輸信號方向的不同,電極分為集總電極和行波電極,其結構如圖7所示。集總電極中微波信號的傳輸方向垂直于光波的傳輸方向,而行波電極的微波信號與光波傳輸方向相同,行波電極結構可以實現高帶寬調制器,廣泛應用在高速調制器中。

圖7 (a)集總電極結構;(b)行波電極結構Fig. 7 (a) Lumped electrode structure; (b) traveling wave electrode structure

集總電極在設計時需要考慮電極寬度W和間隙G。電極間隙和寬度的比值(G/W)與帶寬正相關,同時電極間隙與調制器電壓也正相關。如果要同時實現高帶寬和低調制電壓,則需要電極寬度足夠小,但是電極寬度變小會帶來兩個問題。第一,電極寬度不能小于波導寬度,否則會影響電光積分參數,進而使得調制電壓變大。第二,電極寬度變小會增大靜電電阻,進而限制帶寬[30]。

使用行波電極結構可以制造上百GHz帶寬的調制器,其在設計中需要注意3點:第一,減小電極間隙G可以減小調制電壓,但會增加電極損耗。第二,行波電極設計需要考慮阻抗匹配,行波電極的阻抗與單位長度電容有關,通過優化電極寬度W和電極間隙G可以獲得50 Ω阻抗。第三,行波設計需要考慮速度匹配,行波電極調制器的調制帶寬上限取決于微波在電極中速度和光波在波導中速度的匹配程度,如果微波在電極中的速度等于光波在波導中的速度,則理論上可以達到無限大的帶寬,通過優化電極厚度和傾斜角度、增加 SiO2覆蓋層的方法可以提高微波和光波的速度匹配率[31-32]。

金屬電極一般用剝離技術制備,在最初,熱剝離受限于光刻技術發展,制備的電極間隙和電極厚度在1 μm附近,最近,隨著光刻技術和納米壓印技術的提升,可以實現nm級的電極間隙[33-34]。此外,金屬電極也可以用刻蝕技術制備,雖然刻蝕工藝可以實現較大的電極厚度(>3 μm),但會增加電極寬度(>6 μm)[35]。

3 LN薄膜調制器波導工藝研究進展

3.1 LN薄膜平臺工藝

LNOI通過將鈮酸鋰薄膜(Thin-Film Lithium Niobate,TFLN)與 SiO2鍵合制備而成。TFLN用晶體離子切片技術(Crystal Ion Slicing ,CIS)和熱剝離(Thermal Exfoliation,TE)技術制備。CIS工藝適用于制備10 μm厚的薄膜[36],TE工藝適用于制備亞微米(100~1 000 nm)薄膜[37]。LNOI的鍵合方案有兩類:一類為使用TE工藝的直接鍵合方案,直接鍵合可以實現LNOI晶圓制備[38];另一類為利用苯并環丁烯(Benzocyclobutene,BCB)的間接鍵合方案,由于退火后處于低溫環境(300 ℃),間接鍵合會造成離子損傷并影響晶體的電光特性[39]。LNOI的襯底根據材料不同分為LN襯底和硅襯底,LN襯底雖然工藝成熟,但會引起熱電荷效應,影響器件性能。硅襯底可以避免這一影響,但是由于硅和LN的熱膨脹系數不同,故鍵合需要在在室溫下進行[40-41]

SOI鍵合TFLN將LN晶體優秀的光學性能與成熟的CMOS工藝相結合,極大地推動了集成光電子的發展。其制造過程分為兩步[42],第一步通過CIS和TE技術獲得1 μm厚的TFLN,第二步將硅的微環結構在500 ℃下與TFLN直接鍵合到一起。

3.2 波導層工藝

3.2.1 置換工藝

置換方案有Ti擴散和質子交換(Proton Exchange,PE)兩種。Ti擴散工藝制備的波導的折射率改變量為Δne=0.03, Δno=0.01,擴散深度可以達到4 μm[43],適用于X、Y、Z切波導制作,但光折射和偏振會造成波導損傷[44]。PE工藝折射率改變量可以達到Δne=0.1, Δno=?0.04,但是制作的Y切面波導質量較差,在使用中通常利用X切面和Z切面。對于PE工藝,由于散射損耗會降低波導的光電性能,通過熱退火(Annealing Proton exchange,APE)可以減少這些不良影響[45]。

基于LNOI的PE和APE工藝制作的LN薄膜波導器件雖然折射率改變量有所提升,但是該方案制備的波導對光的限制能力還是較弱,器件半波電壓Vπ>10 V[46-47]。

3.2.2 脊形刻蝕工藝

傳統的脊形刻蝕工藝有濕法刻蝕和干法刻蝕兩種,近些年隨著波導加工工藝的成熟,金剛石加工工藝和化學機械拋光也可制備LN脊形波導。刻蝕中的光刻掩膜板用鉻[48]、無定形硅[49]、金屬[50]或者光刻膠[51]等材料制作,電子束光刻技術(EBL)或UV光刻技術用于對掩模板定形。近幾年,飛秒激光(Femtosecond laseretch)技術也用于光刻[52-53]。飛秒激光光刻的優點是脈沖持續時間短,從而減少了激光脈沖與材料之間的熱相互作用,可實現清晰的刻蝕。

濕法刻蝕由于化學各向同性,刻蝕的波導有一定的傾斜度,嚴重影響波導對光的限制能力[54]。而干法刻蝕為物理刻蝕,具有各項異性,能夠刻蝕理想的脊形結構。隨著工藝的進一步成熟,干法刻蝕的反應離子刻蝕技術(Reactive Ion Etching,RIE)和電感耦合刻蝕技術(Inductive Coupled Plasma RIE,ICP-RIE)[55-56]可以實現小體積、低損耗的波導制備,成為刻蝕脊形波導最具前景的方案[57]。

化學機械拋光(Chemical Mechanical Polish,CMP)制作波導過程如圖8(彩圖見期刊電子版)所示[58],在LNOI上沉積鉻做掩膜層,飛秒激光光刻后,使用兩次CMP對波導進行處理,第一次用于刻蝕LN,第二次用于平滑波導表面。該工藝的優點是不需要離子刻蝕,提高了波導表面的光滑度,降低了波導損耗。

圖8 (a)~(d)CMP工藝流程圖和(e)CMP系統結構圖[58]Fig. 8 (a)~(d) CMP process flow chart and (e) CMP system structure diagram[58]

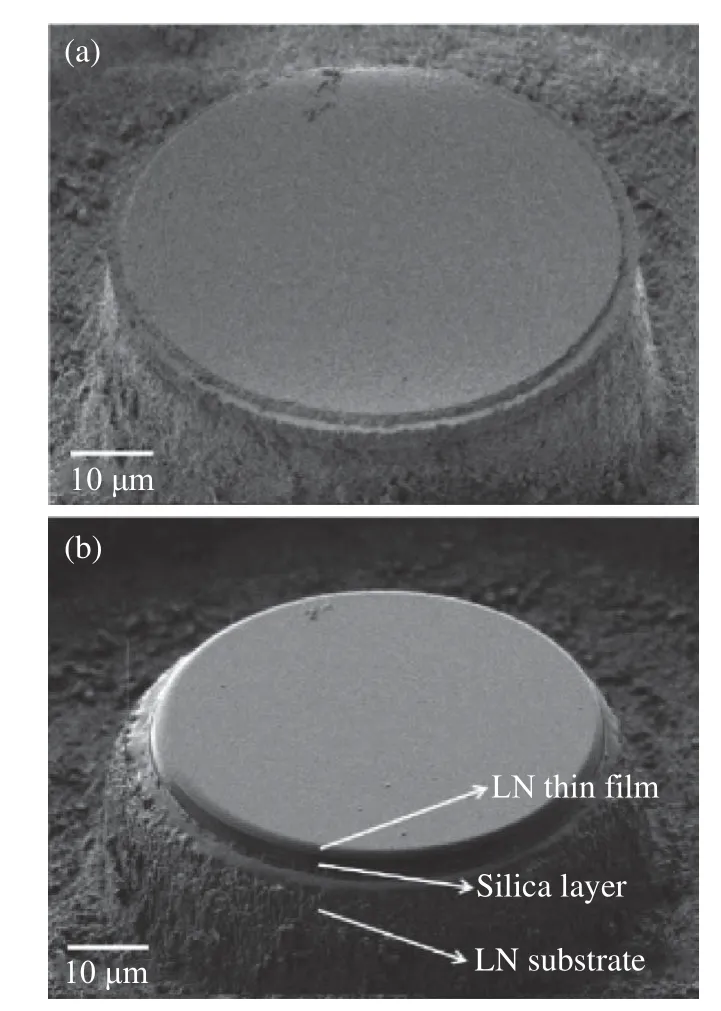

聚焦離子束銑削(Focused Ion Beam milling,FIBm)用于平滑波導圓柱側壁,如圖9所示[59],圖9(a)和圖9(b)分別為FIB銑削之前和之后的圖片。在FIB處理過程中,會引起LN晶格缺陷(空位),但由于調制過程中不涉及自由載流子的運動,因此該缺陷在波導制作中可以忽略。

圖9 (a) FIBm前及(b) FIBm后波導圖像[59]Fig. 9 Waveguide image (a) before and (b) after FIBm[59]

金剛石切割(Diamond blade dicing)可以獲得2~12 μm寬度的脊形結構[60],結合CMP有利于降低傳播損耗(1.4 dB/cm,TE)。金剛石切割工藝過程中會使用兩次切割,如圖10所示[61],第一次在(b)步驟中,在離子注入的薄膜上切出50 μm的凹槽是為了防止在后面與SiO2鍵合時產生氣泡,第二次切割將獲得理想的脊形結構。這種方法可以獲得很好的側壁傾斜度(>65°),但是波導容易斷裂,并且端面會出現傾斜。

圖10 金剛石切割制造波導過程[61]Fig. 10 Diamond cutting process for manufacturing waveguides[61]

上述制造工藝特點如表2所示,在實際制造過程中,為了降低損耗,通常將幾種工藝混合使用,以達到理想的波導性能。

表2 不同刻蝕工藝對比Tab. 2 Comparison of different etching processes

3.2.3 脊形加載工藝

加載型脊形波導不需要刻蝕LN,成為了一種比較熱門的方案。加載型工藝在LNOI上沉積的材料有Si3N4[62-65]、TiO2[66]、Ta2O5[67]、硫化物玻璃材料[68]。材料的損耗參考表3,其中Si3N4材料的折射率最接近LN,在加載型波導中有較廣的應用。

表3 不同加載材料損耗比較Tab. 3 Comparison of loss of different loaded materials

4 LN薄膜調制器性能分析

由2.1.1節得,根據波導薄膜平臺結構不同,LN薄膜調制器分為PE&APEonLNOI(基于LNOI的置換波導調制器)、RibloadLNOI(基于LNOI的加載型波導調制器)、RibEtchonLONI(基于LNOI的脊形波導結構調制器)、TFLNonSOI(基于SOI的薄膜結構調制器)。由2.1.2節得,根據波導光學結構不同,LN薄膜調制器分為PM(相位調制器)、MZM(馬赫曾德干涉調制器)、MIM(邁克耳孫干涉調制器)、MRM(微環調制器)、PHCM(光子晶體諧振腔調制器)。不同調制器施加電壓后輸出光場變化如圖11所示,本節對不同結構的LN薄膜調制器性能進行分析。

圖11 調制器輸出端口光場圖。(a) PM;(b) MZM;(c)MIM;(d) MRM;(e) PHCMFig. 11 The light field change diagram of the output port of the modulator. (a) PM; (b) MZM; (c) MIM; (d)MRM; (e) PHCM

4.1 半波電壓長度積和可調諧性(Half-wave Voltage and Tunability)

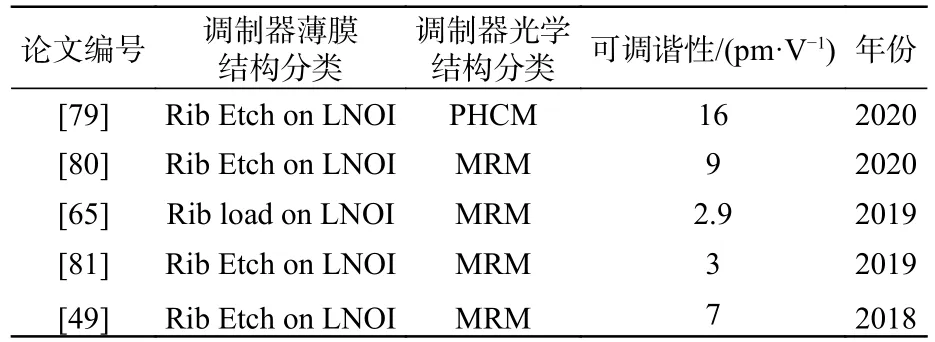

對于相位調制器,半波電壓(Vπ)是在器件在調制長度L上累計π相移所需的電壓。對于干涉型調制器,半波電壓也被叫做開關電壓,是MZM或者MIM導通和關斷所需的電壓。半波電壓長度積(VπL)是一個品質因數,用于衡量干涉調制器功耗性能和器件體積。以pm/V為單位的可調諧性是諧振腔類調制器的Vπ模擬,它表示調制器施加到電極的電壓引起光共振的光譜儀偏移程度,VπL和可調諧性的近期研究進展如表4和表5示。

表4 V πL總結Tab. 4 V πL summary

表5 可調諧性總結Tab. 5 Tunability summary

如表4所示,與MZM相比,MIM可以實現更小的VπL,這是因為在相同長度的器件結構下,MIM有更長的光干涉路程,進而可以獲得更小的VπL。在干涉型調制器中,Rib load on LNOI、Rib Etch on LNOI、TFLN on SOI均可實現較小的VπL(<2 V·cm),Rib load on LNOI優勢在于不需要刻蝕LN,降低了制作難度,TFLN on SOI的優勢在于可以兼容CMOS工藝,該方案將極大促進光子集成的發展。而對于相位調制器,PE&APE on LNOI調制器VπL=6.5 V·cm,優于目前商用調制器VπL=20 V·cm,可以預見LN薄膜結構將極有可能成為新的商用方案。

另外,如表5所示,與微環結構相比,光子晶體結構可以獲得更大的可調諧性,同時光子晶體結構具有更小的體積,在調制器的應用方面具有一定的優勢。

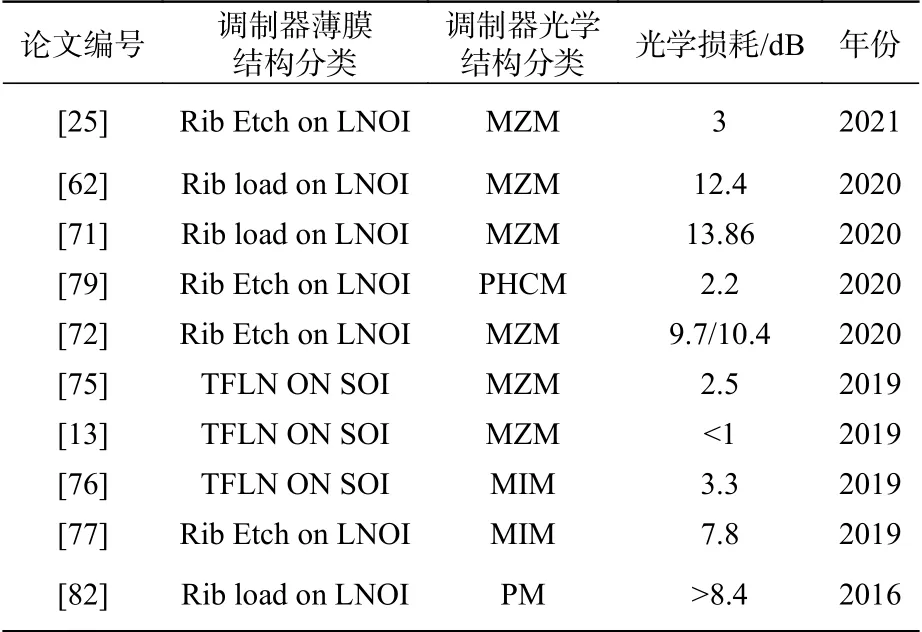

4.2 光學損耗(Optical Loss)

調制器總的光學損耗分為耦合損耗和傳播損耗,耦合損耗取決于輸入光和波導模式之間的模式重疊大小,分析參考2.2節,傳播損耗與波導制作工藝相關,分析參考2.2節。此外,MIM和MZM波導的不對稱也會帶來傳播損耗,這會降低調制器的消光比,并影響線性調頻性能。諧振腔調制器中的傳播損耗與Q值相關,通常Q值越大,損耗越低。調制器光學損耗近期研究進展如表6所示。

表6 光學損耗總結Tab. 6 Summary of optical loss

由表6可得,基于LNOI結構干涉類調制器的光學損耗在2021年取得巨大進步,得益于耦合工藝的提升,新的雙錐形耦合工藝將整體光學損耗由7 dB減小到3 dB[25]。得益于成熟的工藝,SOI結構調制器可以極大降低耦合損耗,進而降低整體的損耗(<1 dB)。而受限于耦合方案的損耗,相位調制器有較大損耗(>8.4 dB),采用雙錐形耦合工藝有望降低整體損耗。

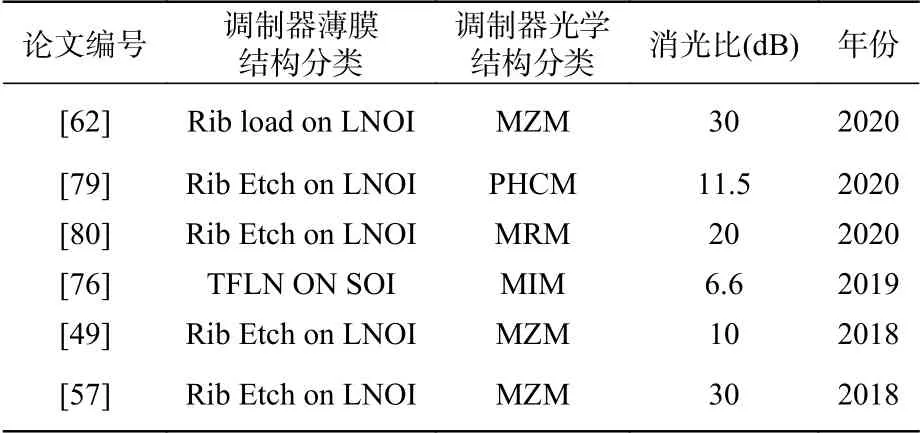

4.3 消光比(Optical Extinction Ratio,OER)

理想MZM和MIM的OER無限大,但是制造的不完美 (兩臂分光不匹配,損耗失衡)導致OER有限。諧振腔調制器的OER由諧振腔的無源光譜響應決定,而該響應又與諧振腔的耦合系數、傳輸損耗有關。調制器的具體應用確定了可接受的OER范圍,比如長距離通信需要OER>20 dB,而在某些交換應用中需要OER>30 dB, 短距離較低的OER也可以傳輸信號。消光比近期研究進展如表7所示。

由表7可得,MZM雖然未實現理想的對稱結構,但仍具有大消光比的優勢(30 dB)。而與微環結構相比,雖然光子晶體結構實現了更高的Q值,但OER不占優勢(11.5 dB),這將限制其在特定場景中的應用。

表7 消光比總結Tab. 7 Summary of OER

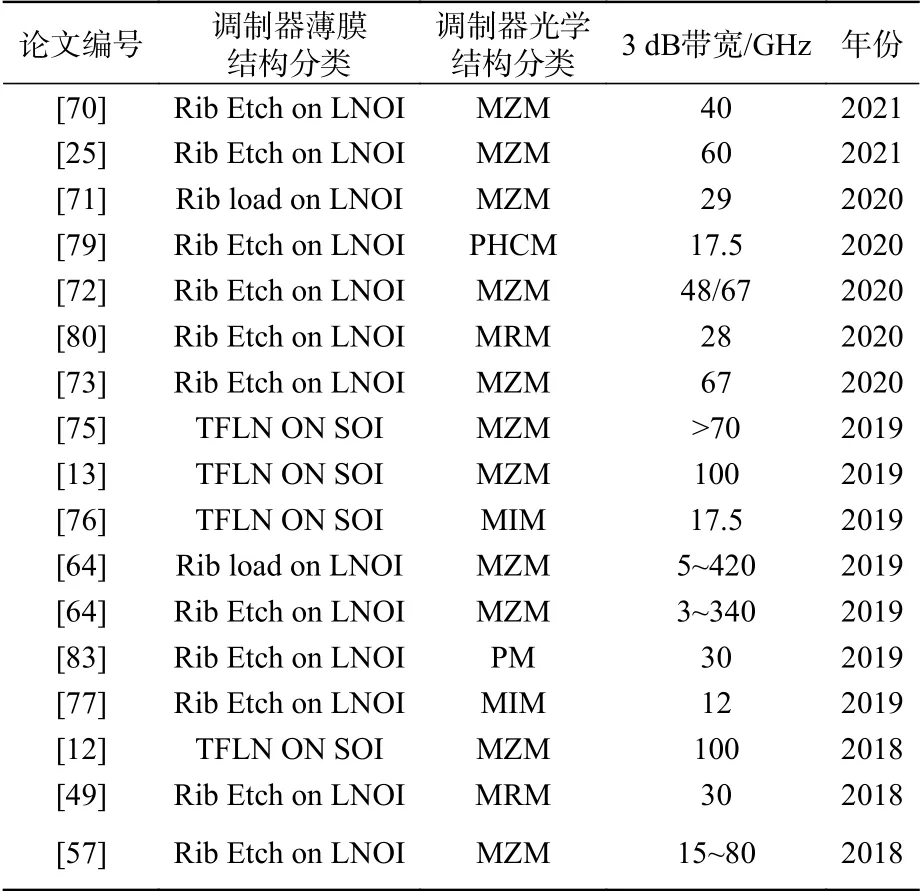

4.4 調制帶寬(Modulation Bandwidth)

調制帶寬是衡量載波攜帶信息量的重要參數,調制器帶寬近幾年研究進展如表8所示。由表8可知,MZM結構是實現高帶寬(>100 GHz)的理想結構,在已有報道中,SOI襯底和LNOI結構都可以實現高帶寬,LNOI結構有更大的帶寬發展空間,但是如果考慮光子集成,SOI襯底具有更大的優勢。

表8 3 dB帶寬總結Tab. 8 Summary of 3 dB bandwidth

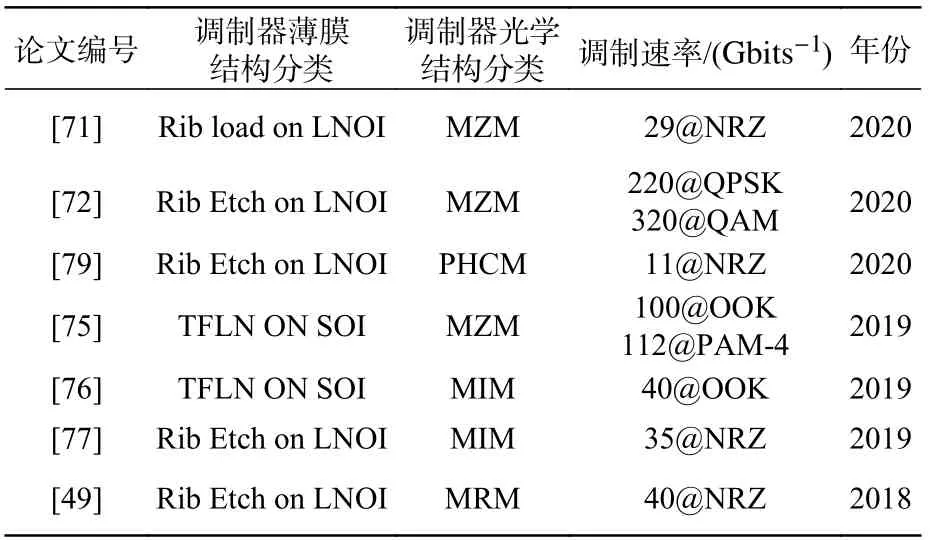

4.5 調制速率(Modulation Rate)

調制速率指單位時間內載波參數變化的次數,其一方面與器件結構有關,另一方面與調制方案有關,常見的光調制方案有開關鍵控 (OOK)、不歸零 (NRZ)、正交調幅 (QAM)、正交相移鍵控(QPSK)和四級脈沖幅度調制 (PAM-4)。調制速率近期研究進展如表9所示,從表中可以看出,在所有干涉類調制器中,MZM結構是實現高調制速率(>100 Gbit/s)的理想結構,同時如果要實現更高速率調制器,需要使用QPSK和QAM調制方案,其由多個MZM級聯而成,對器件設計有較高的要求。

表9 調制速率總結Tab. 9 Summary of modulation rate

5 結 論

綜上所述,LNOI結構有實現更高帶寬的潛在能力,而SOI結構有較低光學損耗和方便光子集成的優勢。基于LNOI結構的調制器光學損耗大于SOI結構調制器的原因在于耦合損耗較大,雖然漸逝耦合方案和集成耦合方案可以實現較低的損耗,但是制作工藝難度大。雙錐形耦合方案可以在降低損耗的同時降低工藝難度,其將是未來LNOI結構調制器的理想耦合方案。在LNOI 3種不同的波導層工藝中,置換波導結構對光場的限制能力小于加載型結構和脊形結構,并且隨著刻蝕工藝的成熟,脊形結構的光傳播損耗小于加載型結構,因此未來將會出現更多基于LNOI的脊形結構的高帶寬調制器研究。

在相位調制器應用中,將面臨消光比和傳輸損耗的問題,解決途徑主要是優化波導的加工工藝以及對芯片和耦合光纖進行鍍膜加工。而強度調制器主要應用于長距離光纖通訊,對帶寬要求較高。基于TFLN on SOI結構的MZM可以實現小型化、高帶寬、低損耗、低功耗的調制器,并且多個實驗室已經成功實現制備,其性能遠超目前的商用調制器,該結構極有可能是未來強度調制器的主流設計,其難點在于波導制備工藝復雜,在商業化應用上還需要一定的時間。因此,如何優化制備封裝等工藝,將是下一步研究的重點。

- 中國光學的其它文章

- 《中國光學》約稿信

- 院士訪談

- Enhancing the fluorescence emission by flexible metal-dielectric-metal structures

- 《發光學報》

——EI核心期刊(物理學類;無線電電子學、電信技術類) - Illustrating the Helmholtz-Kohlrausch effect of quantum dots enhanced LCD through a comparative study

- Fabrication of an ultra-narrow band-pass filter with 60 pm bandwidth in green light band