一種報文離散性可控的標準數字功率源

李愷,雷浩楠,卜文彬,譚海波,黃紅橋,李紅斌

(1. 國網湖南省電力有限公司供電服務中心(計量中心)智能電氣量測與應用技術湖南省重點實驗室,長沙 410001;2. 華中科技大學 電氣與電子工程學院, 武漢 430074)

0 引 言

隨著數字化電能計量的快速發展,對數字化電能計量設備的要求也越來越高。數字化電能表作為數字化計量中貿易結算的關鍵設備,其準確性、可靠性直接關系到電能計量的公平性[1-7]。為保證數字化電能表的性能,必須對其進行嚴格的校驗。

標準數字功率源是校驗數字化電能表的關鍵設備,按照GB/T 17215.303-2013 《交流電測量設備 特殊要求 第三部分:數字化電能表》、DL/T 1955-2018 《計量用合并單元測試儀通用技術條件》等標準,標準數字功率源除了需要滿足電壓電流等基本影響量校驗功能之外,還需要滿足采樣頻率、采樣值數據丟失等特殊影響量要求[8-9],特別是標準數字功率源需要能夠模擬現場特殊工況下的各種采樣值數據丟失,即應滿足能夠產生隨機性報文數據丟失(以下簡稱“丟包”)的要求[10]。

現在許多企業和高校對標準數字功率源進行了研究,并研制出了能夠定量模擬功率波動功能的數字功率源,其報文發布時間離散度降低至500 ns以內,但在丟包的隨機性上仍存在不足[11-13]。

針對上述問題,根據相關國家及行業標準提出了一種報文離散性可控的數字功率源方案,通過基于混沌映射的隨機序列生成算法和高性能光口以太網芯片相結合,既保證了報文數據丟失的隨機性的要求,也滿足了報文發布時間離散值可控的要求。測試結果表明,所研制的數字功率源生成的隨機序列信息熵較大,丟包概率可控;報文發布時間離散值最低降至20 ns,最大離散值不超過200 ns。

1 隨機性報文數據丟失的實現原理

1.1 傳統硬件隨機數生成方法

標準GB/T 17215.303-2013《交流電測量設備 特殊要求 第三部分:數字化電能表》中明確規定數字化電能表的校驗項目涉及丟包試驗以及異常事件通信試驗,這要求數字功率源必須能夠產生隨機報文數據丟失,且丟包概率可控。

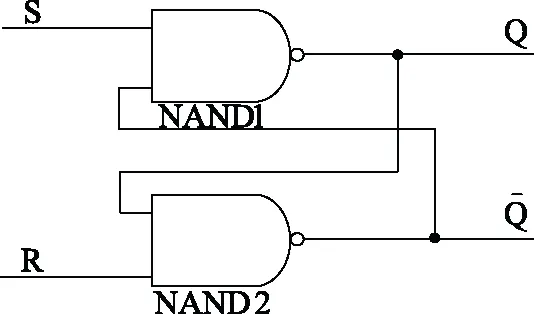

傳統數字功率源隨機性報文數據丟失的生成方法基于FPGA本身所擁有的特性,通過人為的邏輯編程使得FPGA內部產生競爭冒險,根據該現象的不確定性生成相應的隨機序列,以此控制報文數據隨機丟失,RS觸發器為硬件隨機數產生的基本元(見圖1)。

圖1 RS觸發器Fig.1 RS trigger

當S、R同時為0,RS觸發器輸出穩定為(Q, ˉQ)=(1,1),當S與R同時置1時,觸發器進入亞穩態,輸出量Q具有隨機性,取決于與非門的瞬時電平及其內部的噪聲。故而每當系統需要隨機數時,先把S、R同時置0,再將S、R同時置1產生隨機數。由于內部電路相互關聯,使用競爭冒險等不利條件產生隨機數可能會使FPGA的狀態機跑飛,且同時利用多個與非門電路增加了FPGA的功耗。此外,FPGA內部的布局布線通過編譯已經確定,這種依靠邏輯競爭產生的隨機數在時間上的概率分布不均(相關系數大于0.3),統計上無法認定其具有良好的隨機性。

1.2 基于混沌映射的偽隨機序列產生算法

混沌映射所構成的信源是等概率無記憶信源, 滿足隨機數產生器條件,由于混沌映射體現出隨機性的實質是由初始值的精度有限性所提供的,所以可以構建基于隨機種子方式實現隨機數產生器[14-15]。

具體方案如下:首先FPGA上電時即在內部生成內部循環計時器,由0計數至255,當接收到關于隨機數控制指令時,循環計數器停止,取此時記錄的數值作為隨機序列生成的種子(FPGA的主控時鐘頻率為50 MHz,循環計數一個周期所用的時間為167 ms,而接收隨機數控制命令的時間遠超167 ms,可以認為種子在0~255的范圍內服從隨機分布),再根據選取的種子,通過常用的混沌映射生成混沌隨機序列。

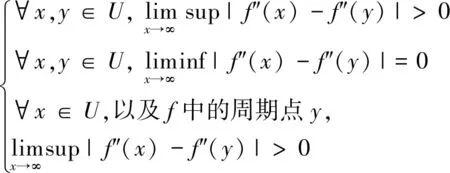

一般來說,當系統滿足式(1)所示的條件時,生成的系統為混沌系統:

(1)

式中f(x)為U上的連續函數;U為任意閉合區間,且不包含周期點。

常見的混沌序列映射方式有以下四種[16-18]:

(1)Logistic映射

xn+1=kxn(1-xn)

(2)

當3.5996≤k≤4時,Logistic映射滿足混沌映射條件。

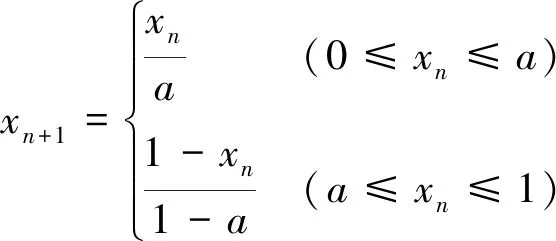

(2)Tent映射

(3)

當初始值x0∈[0,1]時,該序列映射出的xn∈[0,1],此時若xn經過有限次數據迭代,就會進入混沌狀態。

(3)Chebyshev映射

xn+1=cos(k×arcos(xn))

(4)

當k≥2時,Chebyshev映射進入混沌狀態。

(4)改進型Logistic映射

xn+1=1-k×xn×xn

(5)

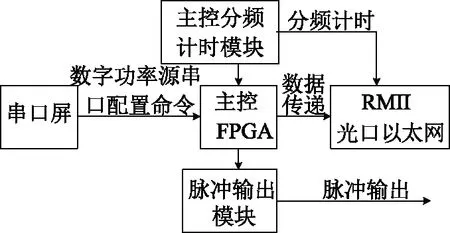

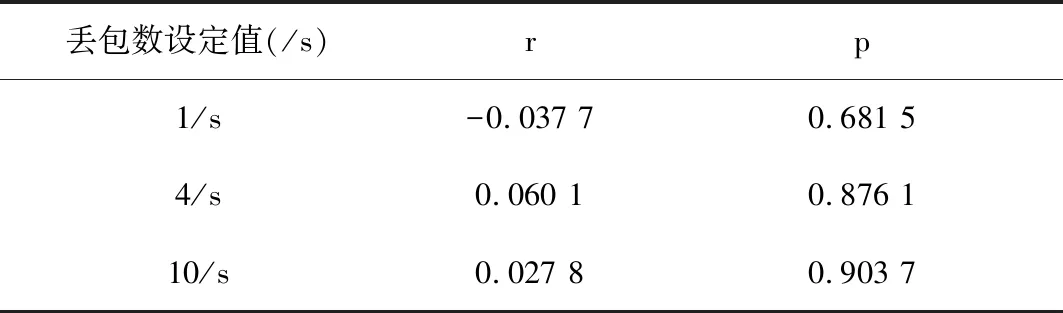

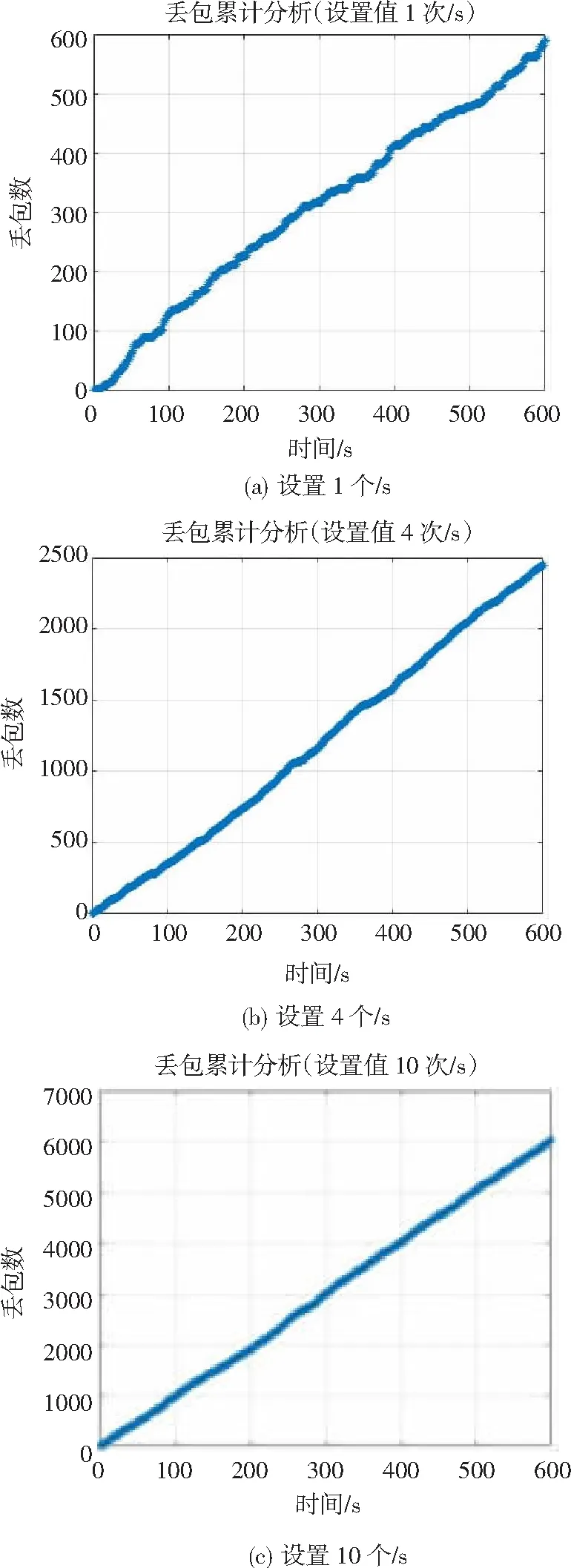

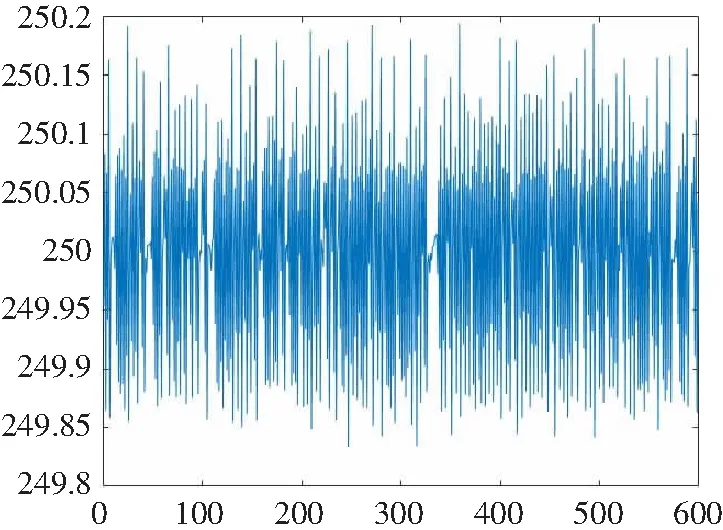

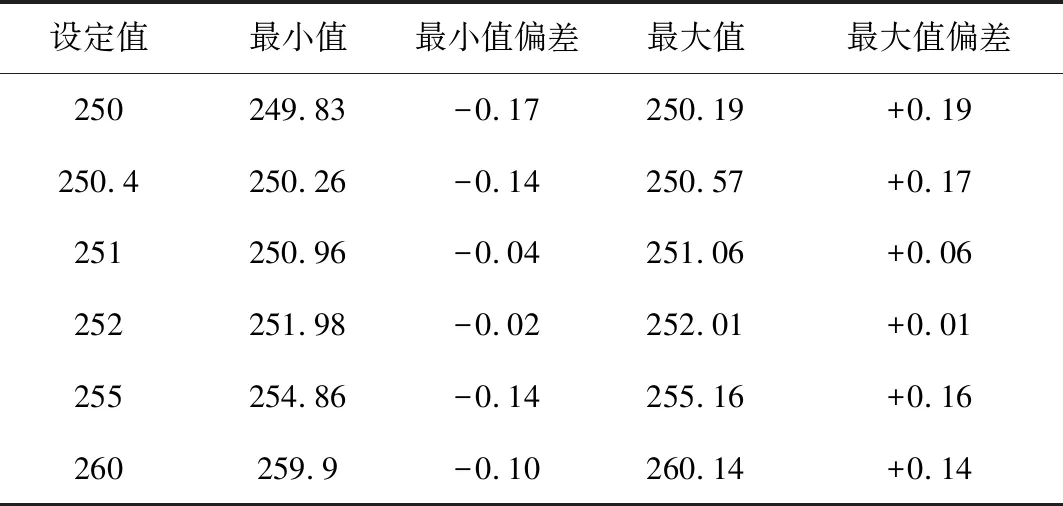

當1.4 其中Tent映射的映射函數本身需要分段,且涉及除法,對于FPGA硬件計算能力要求較高,需要較多的計算資源,不利于計算實時性。 當輸出序列的長度N=10 000時,改進Logistic映射、Logistic映射以及Chebyshev映射的信息熵分別為12.165 5、12.141 6、12.150 5,因此采用改進Logistic映射作為混沌序列產生的映射算法。quartus中有專門針對乘法的ip核,只需循環調用即可生成混沌序列,根據浮點數的計算法則,丟包的概率為: (6) 式中k為概率線。系統概率可控,此外,每次配置丟包概率時,由于種子會發生變化,整個混沌序列也會隨之改變。 基于FPGA自身特性以及quartus計算資源設計的隨機數產生算法,不會產生競爭與冒險等不利因素,且不會因為誤碼而進入循環態,在隨機概率可控的情況下,生成的偽隨機序列熵值較大。 通過FPGA配置光口以太網芯片輸出IEC 61850-9-2序列,同時將芯片配置為時間離散度最小的RMII接口輸出,保證報文發布時間離散度可控。數字功率源主要結構如圖2所示。 圖2 標準數字功率源主要結構Fig.2 Main structure of standard digital power source 標準數字功率源主控通信部分通過串口屏配置功率源生成相應的輸出波形,采用某公司生產的EP4CE15F17C8作為主控FPGA芯片,采用RS232作為主控芯片與控制界面的通信媒介,并通過50 MHz溫補晶振配置計時模塊實時測量光口以太網的包離散度,采用兼容IEEE.802.3以太網協議的物理層芯片DP83848IFVS作為光口以太網的控制芯片,將FPGA溫補晶振的輸出接入芯片的時鐘控制管腳,并通過50 MHz的RMII接口傳輸IEC 61850-9-2數據,速率可達100 Mbps,進一步減小報文發布時間離散度誤差。 光口以太網DP83848IFVS芯片通過RMII的接口實現芯片的上電初始化,同時實現主控與PHY之間的數據通信,RMII接口的基本通信方式如圖3所示。 圖3 通信接口Fig.3 Communication interface RMII數據傳輸通信線為RXD[1:0],TXD[1:0],2路信號并行傳輸,數據控制時鐘為CLK_REF,數據上升沿有效,時鐘頻率為50 MHz,因此RMII接口的通信速率為100 Mbps,數據以低位在后,高位在前的方式傳輸,與FPGA剛好相反,FPGA讀取波表數據后需先經過倒位賦值再輸入RMII接口中。TX_EN,RX_ER為發送接收使能信號,發送數據時需先主動拉低TX_EN,再將數據傳到TXD[1:0]上,數據發送完畢需上拉TX_EN,RX_ER與TX_EN相似。MDC/MDIO屬于MDIO接口的2根數據線,FPGA通過該接口實現對芯片的初始化,從而使芯片能夠正常地發送接收數據。 目前國內外關于數字量溯源的標準較少,無法滿足相關功能的驗證,文中以數字化電能表的檢測項目為準,參考標準中對應的參數指標,設計了準確度較高的數字量驗證平臺,對標準數字功率源的隨機性報文數據丟失以及報文發布時間離散度可控等基本功能進行驗證。 參考GB/T17215.303-2013《交流電測量設備 特殊要求 第三部分:數字化電能表》、DL/T《1955-2018 計量用合并單元測試儀通用技術條件》等標準規定,設計了圖4所示的數字量驗證平臺。 圖4 數字量驗證平臺Fig.4 Verification platform for digital quantity 將標準數字功率源的光口以太網報文輸入硬件解碼裝置,通過以太網芯片DM9000A的接收中斷信號判斷采樣頻率以及丟包數,并將結果傳輸至上位機。通過高頻時鐘記錄相鄰片選信號的下降沿確定報文發布時間離散值。其中硬件解碼裝置含有標準的光口以太網接收模塊,采用RMII接口接收光口數據,該接口時間不確定度為20 ns,遠小于3 μs的誤差線。 分別將丟包率設置為1個/s,4個/s,10個/s,各測10 min數據,統計每秒的丟包數以及丟包總數,設置為1個/s時的丟包數據如圖5所示。 圖5 1個/s丟包實驗結果Fig.5 Results in package losing test (1/s) 根據解得的丟包結果,計算每秒丟包數與時間的相關系數r及顯著性水平p,結果如表1所示。 表1 相關系數及顯著性水平Tab.1 Correlation coefficient and significance level 從表1可見,置信水平(1-p)均小于50%,可認定其分布與時間變量相關性極不顯著,隨機性較強,與實際情況相符。根據上述結果得到丟包累積曲線,如圖6所示。 圖6 累積丟包Fig.6 Cumulative package loss 10 min測得丟包累積量與時間變量的相關系數分別為:0.996 4(1個/1 s),0.999 4(4個/1 s), 0.999 8(10個/1 s),可認為丟包累計與時間呈線性相關。由于在初始時刻丟包數為零,故丟包累計值可視作時間的正比例函數,使用y=kx模型對個點進行擬合,則直線斜率即為每秒丟包數。擬合直線斜率即分別為:0.991 5(1個/1 s),3.999 1(4個/1 s),10.000 2(10個/1 s),與設置值相符,滿足丟包概率可控。 Q/GDW 11111-2013《數字化電能表校準規范》以及Q/GDW 11015-2013《模擬量輸入式合并單元檢檢測規范》均規定輸入數字表的合并單元光口數據時間離散值不得超過10 μs,而標準DL/T 1955-2018 《計量用合并單元測試儀通用技術條件》在此基礎上明確地提出了采樣值發布離散值的檢測標準。 為校驗這一功能,分別設置數字功率源報文發布時間離散值為250±0 μs、0.4 μs、1 μs、2 μs、5 μs和10 μs, 每次測試10 min,同時要求標準源的檢測誤差不得大于3 μs。報文發布時間離散值為250±0 μs的實驗數據如圖7所示。 圖7 報文發布時間離散值測量系統Fig.7 Measurement system for discrete value of message release time 由圖7可知,在報文發布時間離散值設定為250±0 μs的情況下,功率源的報文發布時間離散值誤差最大不超過200 ns。 功率源具備報文發布時間離散值可調功能,設置離散值在250+0.4 μs、250+1 μs、250+2 μs、250+5 μs和250+10 μs, 進行實驗,每次測試10 min,由于篇幅所限,其余各測試點的實驗數據不在單獨列出,將離散值誤差記錄在表2中。 從表2實驗數據可以看出,功率源的報文發布時間離散值誤差不超過200 ns,在離散值為250+2 μs時,離散值誤差最大不超過20 ns,小于3 μs的誤差要求,滿足標準數字源的設計需求。 表2 實驗結果(單位:μs)Tab.2 Experimental results (μs) 設計了一種報文發布時間離散性可控的數字功率源方案。通過基于混沌映射的隨機序列生成算法和高性能光口以太網芯片相結合,解決了傳統數字功率源報文數據丟失隨機性不足的問題,并控制報文發布時間離散值誤差至200 ns。所研制的標準數字功率源滿足標準GB/T 17215.303-2013 《交流電測量設備 特殊要求 第三部分:數字化電能表》中提出的關于數字化電能表的異常通信影響試驗,以及DL/T 1955-2018 《計量用合并單元測試儀通用技術條件》規定的采樣值發布離散值的測試要求。可以用作數字化電能表的檢定工作,已地南方電網公司數字電能表校驗項目中推廣應用。2 基于高性能光口以太網芯片的系統設計

2.1 標準數字功率源主要結構

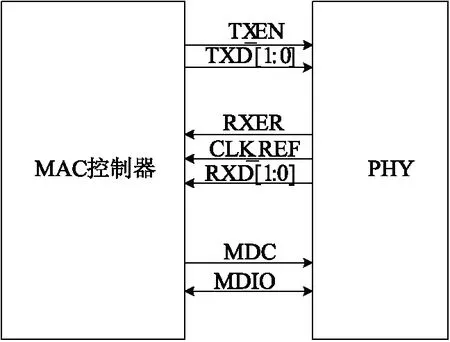

2.2 高性能光口以太網接口設計

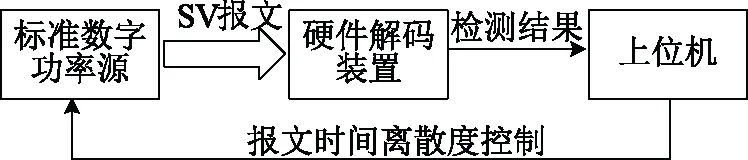

3 數字輸出影響量和報文發布時間離散度功能驗證

3.1 數字量驗證平臺設計

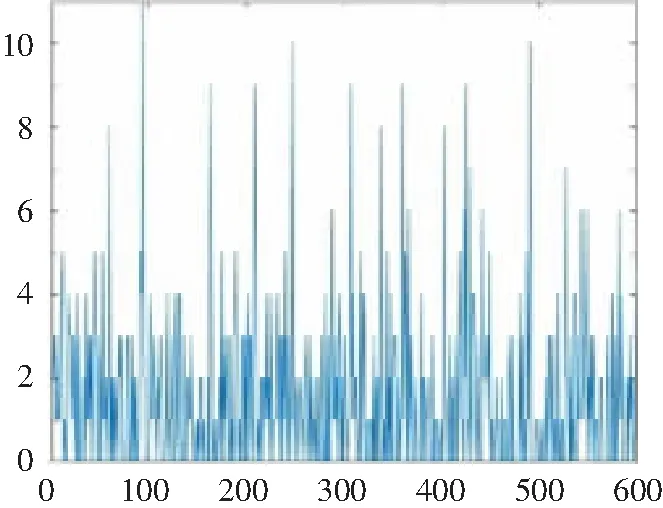

3.2 報文數據丟失測試

3.3 報文發布時間離散值可控功能測試

4 結束語