基于FPGA的空調顯示設定器程序升級方案設計

田地,李康樂,楊春宇

(西安中車永電捷通電氣有限公司,陜西西安,710016)

0 前言

2016年7月,國家發展改革委、交通運輸部、中國國家鐵路集團有限公司聯合發布了《中長期鐵路網規劃》,勾畫了新時期“八縱八橫”高速鐵路網的宏大藍圖,即以沿海、京滬等“八縱”通道和陸橋、沿江等“八橫”通道為主干,城際鐵路為補充的高速鐵路網。“八縱八橫”可實現相鄰大中城市間1-4小時交通圈、城市群內0.5-2小時交通圈。隨著“八縱八橫”鐵路網絡建設有序推進、逐步完善,使我國高速鐵路網絡四通八達。加之高速動車組有載客量大、速度快、到點準時、乘坐舒適、行駛平穩、受雷雨等惡劣天氣影響較小等特點,成為越來越多的人出行交通工具的首選。高速動車組優異的舒適性不僅體現在行駛平穩性上,其精確的車廂溫度控制與通風控制也是重要的原因之一。

空調顯示設定器作為動車組列車空調運行控制的核心部件,廣泛應用于我國CRH2系列、CRH380系列等動車組上,其主要功能為接收列車網絡(TCMS)下發或自身按鍵手動設置的空調運轉模式、控制溫度等指令信息,進一步傳輸至空調微機室實現車廂空調系統溫度、風量等控制。同時將空調運行狀態、溫度信息、故障狀態上傳至列車網絡,并且同步在空調顯示設定器面板進行顯示。以上功能邏輯是由控制器通過軟件實現的,我國幅員遼闊、高速動車組線路長、自然環境復雜多變,為適應不同的線路環境,對于空調系統控制邏輯的優化更改在所難免。當前在運營動車組空調顯示設定器均由國外進口,更改軟件依賴于國外廠家,存在更改費用高、響應周期長的弊端。在進行升級作業時,需拆開顯示設定器面板,升級完畢后需進行面板安裝恢復,做緊固標記,作業時間較長。本文基于FPGA芯片的國產化空調顯示設定器,創新性的提出了通過串口升級FPGA程序的方案,使升級作業效率大幅提高,節省了人力成本,縮短作業時間。

1 系統方案

由于空調顯示設定器需同時與列車網絡、兩組空調微機室實時通信,并及時響應空調控制指令,還需響應面板與按鍵操作,同步執行復雜的控制邏輯,因此控制器性能成為方案設計重要因素之一。FPGA以并行執行,可重復、靈活配置等優勢,成為國產化顯示設定器主控芯片的首選。按照設計要求,空調顯示設定器外部需預留串口作為數據下載接口,故本方案不再額外增加接口,設計數據下載與程序升級公用同一串口。根據功能評估結果,本文選取Xilinx公司Spartan6 系FPGA作為主控芯片。因為FPGA基于SRAM結構,配置文件掉電會丟失,需要在外部配置存儲介質進行配置文件存儲或通過額外的處理器進行配置文件寫入。Spartan6系列FPGA程序配置方式可分為主模式(Master Modes)、從模式(Slave Modes)、JTAG模式。根據存儲介質接口的不同又可細分為主串、主并、從串、從并等模式。

1.1 主模式

主模式即FPGA作為主設備,存儲介質作為從設備, FPGA的CCLK引腳給存儲介質提供工作時鐘,上電后FPGA將主動從存儲介質中讀取程序配置文件,典型的模式可分為PROM模式和SPI-Flash模式,具體介紹如下。

①主串模式-PROM

FPGA作為主設備,Xilinx PROM作為從設備。此方案需要通過JTAG將配置文件燒寫至PROM中,FPGA上電后將主動從PROM中讀取配置文件。DIN與CCLK管腳在程序配置完成后可作為用戶IO使用, PROM成本相對較高。

②主串模式-SPI Flash

此模式下需FPGA外部配置SPI Flash,FPGA作為主設備,SPI Flash作為從設備。配置模式選擇后, FPGA上電時主動從SPI Flash中讀取程序文件,MOSI、DIN、CSO_B、CCLK等信號在FPGA配置完成后可作為用戶IO使用,串行Flash的特點是占用引腳比較少,器件封裝小,容量大,不但可以節約電路板空間,還能降低功耗核噪聲。存儲程序文件的同時也可用作用戶數據存儲。

③主并模式-NOR flash

此模式下FPGA外部需配置并行NOR Flash, FCS_B等接口信號,在程序引導完成后,也可以作為用戶IO使用,并行NOR Flash占用FPGA管腳數量較多。

④主并模式-并行PROM

并行PROM模式下FPGA作為主設備,并行PROM作為從設備,配置文件可通過JTAG寫入PROM中,FPGA上電時,主動從并行Flash中引導配置文件,引導完成后,配置管腳可作為用戶IO使用,此方案特點是占用FPGA管腳資源較多成本較高。

1.2 從模式

從模式根據外部處理器接口分為從并模式和從串模式。

①從串模式

即FPGA作為從設備,需要外部處理器通過串行接口將配置文件寫入FPGA。

②從并模式

即FPGA作為從設備,需外部處理器通過并行接口將配置文件寫入FPGA,雖然從模式不需要額外的存儲介質,但需要外部額外配置處理器進行配置文件寫入,成本較高,增加了開發難度。

根據項目應用場景要求,控制板卡安裝在顯示設定器箱體內,顯示設定器整體安裝于動車組車廂電氣柜中,在實際運營、程序升級作業時,一般禁止打開顯示設定器面板,故通過JTAG升級配置文件方案不能滿足要求,若使用從模式配置程序文件,需額外增加處理器,增加了成本和開發工作量。主模式里,PROM成本高于SPI Flash,串行SPI Flash接口比并行FLASH簡單,節約FPGA管腳資源。綜合考慮,本項目使用主串配置模式,選擇SPI Flash作為存儲介質,通過FPGA數據手冊可知,SPI接口MOSI、DIN、CSO_B、CCLK在程序配置完成后可以做用戶IO使用,則當程序引導完成后,FPGA可以操作上述接口操作SPI Flash。那么通過顯示設定器外部DB9接口,就可以使用PC把程序配置文件下發至FPGA,FPGA將配置文件緩存后,再寫入SPI flash,從而實現配置文件自升級功能。

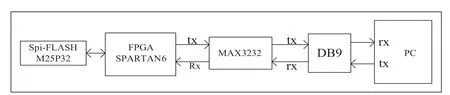

1.3 硬件方案

結合研發成本與工作量本項目總體方案設計如圖1所示,系統主控芯片采用Spartan6系列FPGA,SPI Flash選用成本較低的M25P32,需要進行配置文件更新時,通過PC上位機將BIN文件下發至FPGA,FPGA完成SPI FLASH擦除后,邊緩存配置文件,邊通過SPI驅動將數據寫入Flash,從而完成程序文件更新,文件寫入完成后,只需空調顯示設定器重新上電,新程序即可完成配置。

圖1 系統硬件方案

2 軟件實現

本方案軟件部分包括上位機軟件和FPGA軟件兩部分。

2.1 FPGA軟件

FPGA實現與上位機通信,接收上位機升級指令及程序文件數據并進行數據緩存、實現SPI Flash 驅動管理、程序文件的flash寫入等功能,軟件模塊架構簡圖如圖2所示。

圖2 軟件結構模塊

波特率生成模塊:根據系統時鐘生成目標波特率,提供數據發送接收模塊使用,作為異步串行通信的協議基準。

數據接收模塊:對串行RX信號的起始位、數據位、停止位進行識別與判斷、完成奇偶校驗并進行數據串并轉換。

數據發送模塊:對并行字節數據進行并串轉換、補充起始位、校驗位、停止位數據,配合波特率模塊完成TX串行數據發送。

指令數據解析模塊:對接收到的數據幀進行解析判斷及校驗,如果是升級指令,將指令轉發至FLASH控制邏輯模塊,完成FLASH擦除等程序升級準備工作。如果是程序數據,將數據寫入文件接收雙口RAM中進行緩存。

雙口RAM:因為接收數據速率與寫FLASH速率不一致,使用雙口RAM對程序文件的緩存,起到Flash和上位機數據間橋梁和數據緩沖的作用,本項目使用IP核利用BRAM生成FPGA內部雙口RAM。

FLASH控制邏輯模塊:根據指令完成SPI-Flash讀、寫、擦除命令生成,包括各寄存器指令、讀寫擦除流程控制,讀、寫、擦除、程序文件寫入完畢的判斷,是整個升級流程的“指揮官”。

SPI驅動模塊:按照M25P32數據手冊中對于讀寫時序要求,完成SPI控制協議時序實現。

(1)串行通信協議

本項目與PC的串行通信波特率為57600bps,數據位8位,起始位1位,偶校驗。

(2)FLASH 驅動實現

M25P32具有32Mb容量,時鐘頻率最高支持75MHz,支持256bytes頁編程,整個空間由64個扇區組成,每個扇區包含256頁,每頁包含256bytes數據,M25P32支持扇區擦除和整片擦除。SO8封裝的M25P32共有8個引腳,驅動的實現主要是跟據數據手冊相關要求,操作相應管腳高低電平,各電平必須符合讀時序、寫時序要求。本項目SPI Flash在完成配置后,時鐘信號作為用戶IO由FPGA提供,頻率選用5MHz,占空比50%,所有接口信號執行均有較大裕量,滿足時序要求。

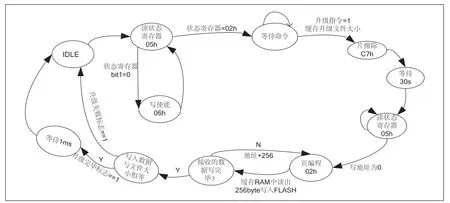

(3)升級軟件處理邏輯

軟件處理邏輯如圖3所示,FPGA內部使用狀態機編碼實現,狀態機包含有上電讀狀態寄存器、等待命令、執行片擦除、頁編程等。當接收到程序升級命令后,先對SPI Flash執行整片擦除操作,因擦除時間較長,內部BRAM容量有限,需完成擦除后再開始接收配置文件數據,一邊接收數據寫入內部雙口RAM中,一邊進行SPI Flash頁編程操作,直到全部配置文件數據寫入完畢。并對上位機下發的文件大小與接收的文件大小進行對比,若文件大小比照正確后,向上位機返回升級完畢指令,若對比失敗,則向上位機返回升級失敗提示,重新進行上述升級流程即可。

圖3 升級軟件處理邏輯

2.2 上位機軟件

本項目上位機軟件使用NI公司Labview軟件進行開發,界面分可為數據下載、軟件升級、時鐘設定等功能,進入界面后會首先會選擇波特率等串行通信協議參數。

數據下載:可下載空調機組運行數據,并生成EXCEL格式文檔,方便對空調機組運行情況進行查看,便于故障定位分析,此功能非本文重點,不再贅述。

軟件升級:用于選擇FPGA配置文件所在位置、下發FLASH擦除指令、對BIN文件進行大小計算并分包下發、判斷是否升級成功。

時鐘設定:可重置空調顯示設定器內部時鐘芯片。

3 驗證

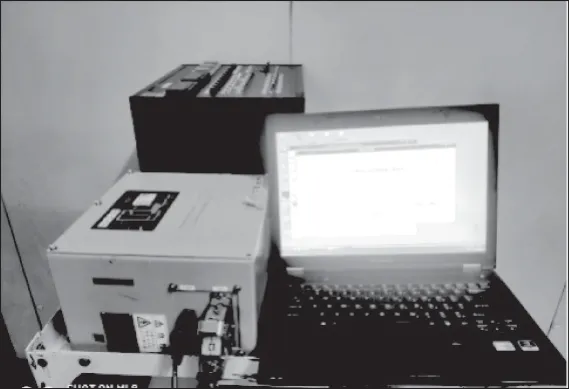

(1)整體實物圖

圖4為空調顯示設定器實物與上位機界面圖,可以看出顯示設定器與上位機通過USB轉RS232串口線進行連接,通過操作上位機軟件,選擇正確的異步串行通信協議,操作簡單的菜單即可完成FPGA程序升級。

圖4 空調顯示設定器實物圖

(2)驅動實現

圖5所示為SPI驅動時序實測圖,讀寫數據的時鐘頻率5MHz,占空比50%,時序滿足要求,相較于數據手冊時序要求,均有較大裕量,對于Flash的讀寫擦除均可穩定執行。

圖5

(3)上位機

圖6為程序升級完成后上位機提示框,表示程序升級完成并且升級成功,此時需對顯示設定器進行重新上電,新的配置文件即可加載。若提示框顯示升級失敗,則重新選擇文件,再次執行升級步驟,直至提示升級結束。

圖6 上位機升級完成界面

4 結語

本文設計了基于FPGA的空調顯示設定器程序自升級方案,通過與數據下載功能共用串口進行程序文件升級,使升級流程極大簡化,升級作業不需要打開空調顯示設定器機箱蓋板,只需通過串口線連接電腦即可升級,方便快捷,提升了售后服務效率,單人即可完成操作,縮短了升級作業時間,節省了人力成本,目前本方案設計空調顯示設定器已在380AL車型載客運營2年,性能穩定。