一種新型存算一體電路設(shè)計(jì)與研究

陸春帆,劉 爽,周 洲2,

(1.重慶郵電大學(xué),重慶 400000;2.電子科技大學(xué)重慶微電子產(chǎn)業(yè)技術(shù)研究院,重慶 400000;3.電子科技大學(xué),四川 成都 610000)

引言

隨著人工智能近些年在自動駕駛、智能機(jī)器人、航空航天等領(lǐng)域不斷地高速高進(jìn)度發(fā)展,卷積神經(jīng)網(wǎng)絡(luò)機(jī)器學(xué)習(xí)算法更是非常廣泛使用,正是因?yàn)樵撍惴ㄔ谡J(rèn)知和決策任務(wù)方面卓越性能。卷積神經(jīng)網(wǎng)絡(luò)優(yōu)勢很突出,以下三點(diǎn)是處理器處理數(shù)據(jù)要求:(1) 網(wǎng)絡(luò)相互連接十分復(fù)雜;(2) 將進(jìn)行超大量卷積運(yùn)算;(3) 神經(jīng)網(wǎng)絡(luò)數(shù)據(jù)隨著神經(jīng)網(wǎng)絡(luò)的規(guī)模不斷擴(kuò)大呈現(xiàn)指數(shù)級現(xiàn)象增長。市場上常見CPU 和GPU 都是使用至今馮·諾依曼結(jié)構(gòu),而傳統(tǒng)馮·諾依曼結(jié)構(gòu)處理數(shù)據(jù)方式是將數(shù)據(jù)存儲在某個(gè)存儲模塊單元中,在需要進(jìn)行數(shù)據(jù)加工時(shí)將其取出,在完成數(shù)據(jù)加工以后再次存入另外一個(gè)存儲模塊中。傳統(tǒng)馮·諾依曼結(jié)構(gòu)將存儲和運(yùn)算分離開來形成兩個(gè)模塊,進(jìn)一步能看出這種結(jié)構(gòu)在進(jìn)行數(shù)據(jù)交換時(shí),需要消耗大量的資源和非常大的功耗。這是造成傳統(tǒng)CPU 和GPU 無法體現(xiàn)卷積神經(jīng)網(wǎng)絡(luò)性能優(yōu)勢的表面原因,根本原因是傳統(tǒng)CPU和GPU 在進(jìn)行運(yùn)算的過程中需要調(diào)用指令讀取存儲模塊中數(shù)據(jù),而存儲模塊有限讀取帶寬,引起處理卷積神經(jīng)網(wǎng)絡(luò)數(shù)據(jù)吞吐率下降。

機(jī)器學(xué)習(xí)算法處理數(shù)據(jù)優(yōu)點(diǎn)不斷放大,但是所占用存儲空間隨之變大,在大規(guī)模神經(jīng)網(wǎng)絡(luò)中,比如深度神經(jīng)網(wǎng)絡(luò),內(nèi)存對能效比限制成為傳統(tǒng)馮·諾依曼結(jié)構(gòu)計(jì)算機(jī)的挑戰(zhàn)。該挑戰(zhàn)伴隨人工智能在當(dāng)今被普及越發(fā)明顯。計(jì)算量大是神經(jīng)網(wǎng)絡(luò)的重要特征之一,而且在計(jì)算過程中所涉及數(shù)據(jù)信息量很大,這些在傳統(tǒng)馮·諾依曼結(jié)構(gòu)計(jì)算機(jī)中體現(xiàn)就是進(jìn)行大量循環(huán)往復(fù)的讀寫內(nèi)存。目前DRAM進(jìn)行一次讀寫32bit 數(shù)據(jù)所消耗能量是32bit 數(shù)據(jù)計(jì)算所消耗能量大兩到三個(gè)數(shù)量級,不難看出這是總體計(jì)算設(shè)備中能效比的瓶頸。

DianNao 和Eyeriss 使用了數(shù)據(jù)重用技術(shù)[1-2],特點(diǎn)是對外部存儲數(shù)據(jù)不斷重復(fù)使用,但對片上存儲數(shù)據(jù)進(jìn)行處理所消耗能量并沒有明顯優(yōu)化,SRAM 不斷反復(fù)進(jìn)行讀取還存在延遲問題;雖然可以采用低功耗數(shù)字電路設(shè)計(jì),例如動態(tài)電壓- 頻率調(diào)節(jié)[3]和時(shí)鐘門燮技術(shù)[4],但訪問存儲功耗和延遲問題并沒有解決;低壓(幾百mV)SRAM 技術(shù)[5]對內(nèi)存讀取功耗優(yōu)化顯著體現(xiàn),但是電壓余量減少,數(shù)據(jù)讀取出錯(cuò)更容易出現(xiàn)。

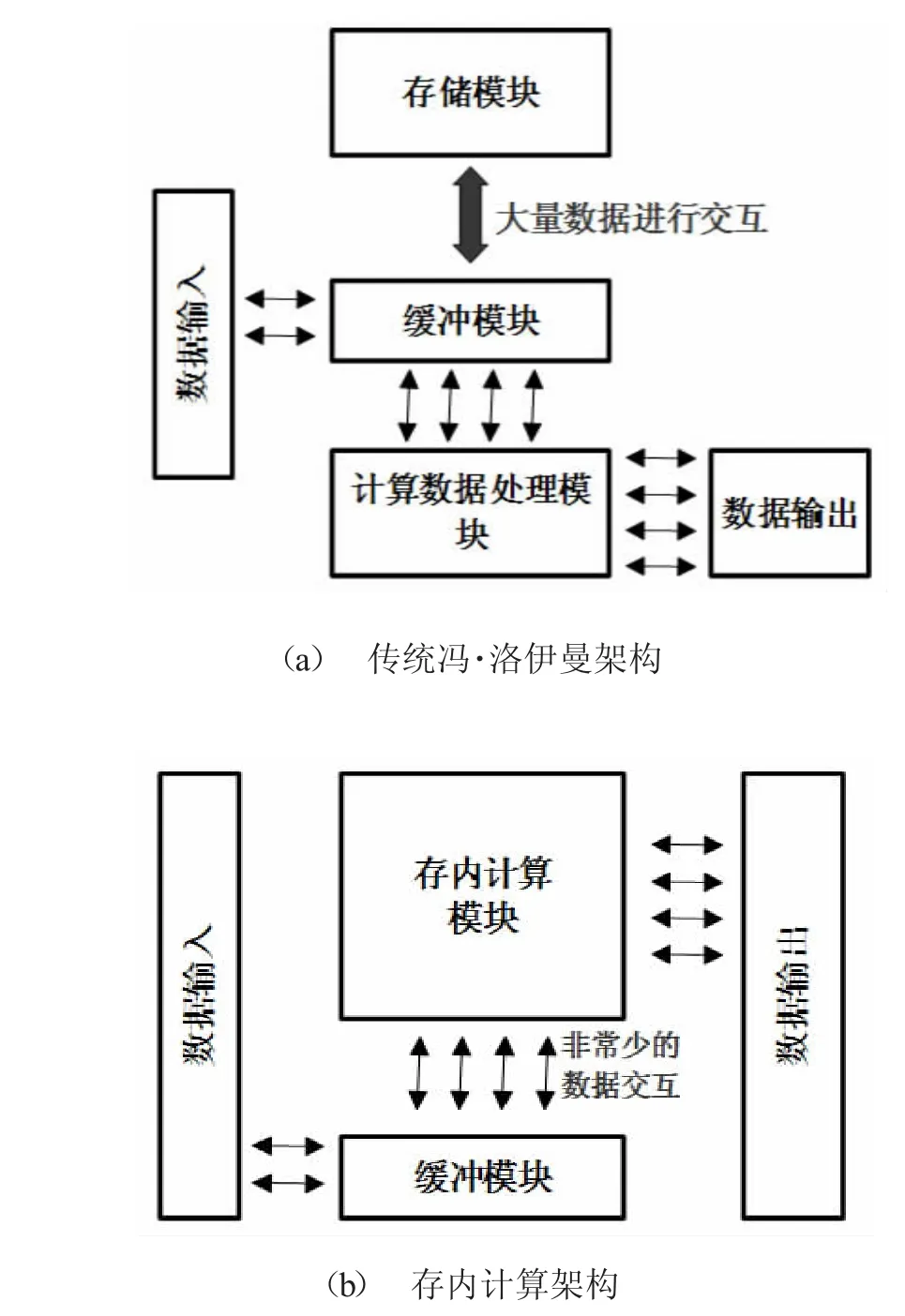

為了解決這個(gè)問題,提出將存儲和計(jì)算結(jié)合的計(jì)算方法,即存內(nèi)計(jì)算。存內(nèi)計(jì)算概念最早使用是在商業(yè)數(shù)據(jù)庫系統(tǒng)領(lǐng)域,例如IBM 公司的DB2,微軟公司的SQL Server。存內(nèi)計(jì)算與傳統(tǒng)馮·諾依曼架構(gòu)區(qū)別是在每一個(gè)存儲單元內(nèi)或者旁邊設(shè)計(jì)了運(yùn)算邏輯單元,這樣極大的解決功耗問題和提升數(shù)據(jù)吞吐率。圖1(a)為傳統(tǒng)馮·洛伊曼架構(gòu),圖1(b)為存內(nèi)計(jì)算架構(gòu),易知存內(nèi)計(jì)算對計(jì)算過程數(shù)據(jù)搬運(yùn)有顯著優(yōu)化。

圖1

1 存內(nèi)計(jì)算

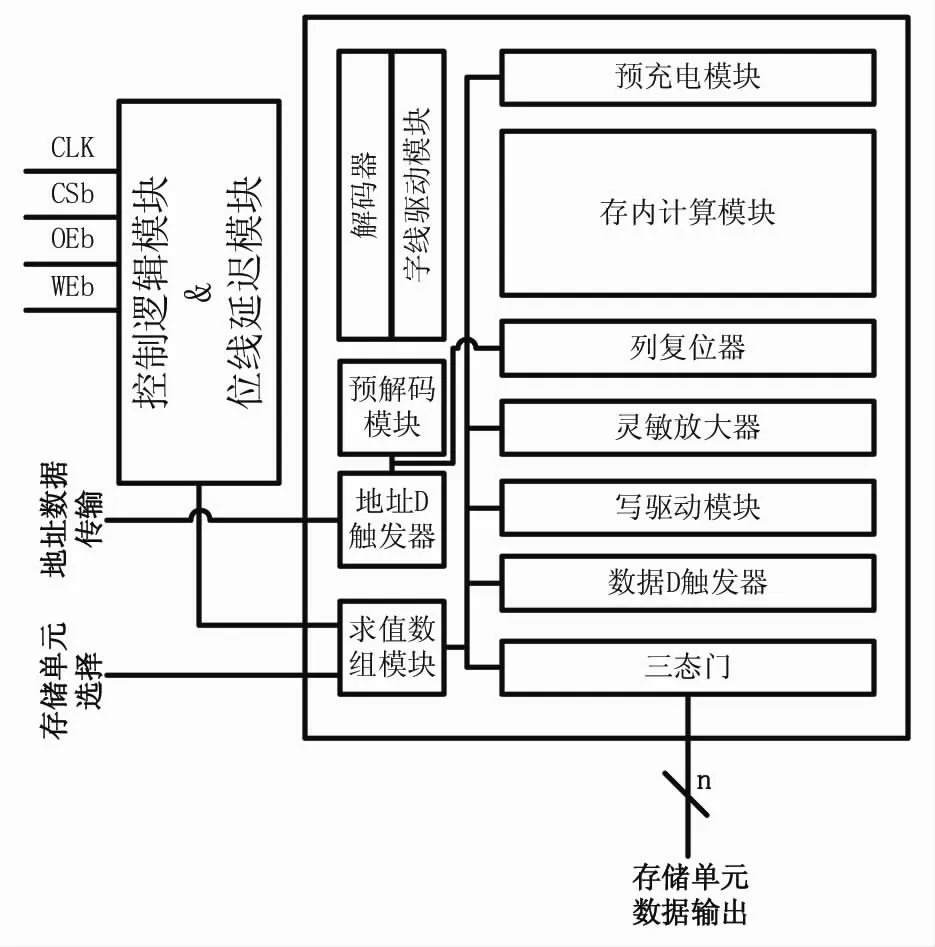

存內(nèi)計(jì)算概念提出一直到今天,很多研究者已經(jīng)完成基于CMOS 工藝存內(nèi)計(jì)算系統(tǒng)。例如,Mingu Kang 等人提出一種基于靜態(tài)隨機(jī)存取存儲器(SR AM)的內(nèi)存計(jì)算卷積神經(jīng)網(wǎng)絡(luò),圖2 是本研究提出核心存算系統(tǒng)結(jié)構(gòu)。存算系統(tǒng)通過邏輯燮制單元對存算電路模塊完成讀寫模式或計(jì)算模式。在讀寫模式下,計(jì)算模式處于關(guān)閉狀態(tài),讀寫模式分為讀信號和寫信號兩種狀態(tài),不能同時(shí)存在。通過求值數(shù)組模塊對信號再處理燮制三態(tài)門電路、預(yù)充電電路、列復(fù)位器電路、靈敏放大器電路寫驅(qū)動電路、以及數(shù)據(jù)D 觸發(fā)器驅(qū)動,其中觸發(fā)器目的是將數(shù)據(jù)與時(shí)鐘信號同步,其他模塊完成系統(tǒng)功能。

圖2 存算系統(tǒng)結(jié)構(gòu)

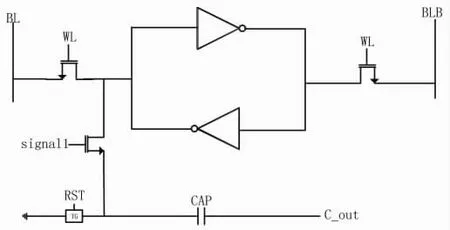

此系統(tǒng)核心存算電路結(jié)構(gòu)見圖3,通過大量重復(fù)單元邏輯組合完成更大計(jì)算功能。計(jì)算功能是通過signal1 實(shí)現(xiàn),signal1 打開之前,通過RST 對CAP 電容上的電荷重置。signal1 打開,存儲為“1”時(shí),CAP 充電為“1”,存0 時(shí),CAP 電荷不變。

圖3 存算電路

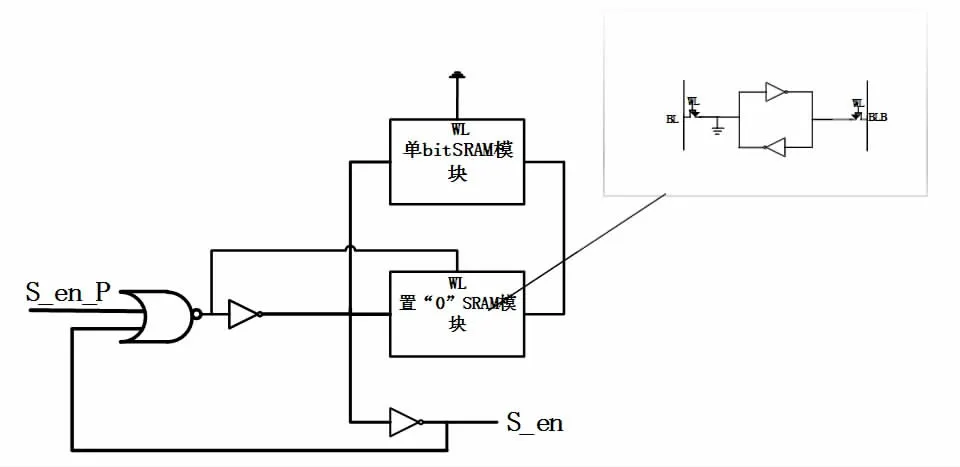

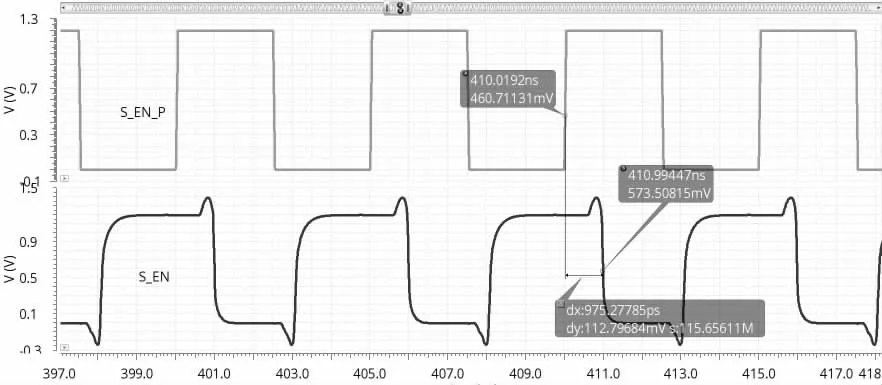

本研究結(jié)構(gòu)優(yōu)化提出位線置位延時(shí)模塊見圖4,S_en_P 輸入為1 時(shí),S_en 輸出為0,靈敏放大器開始工作。S_en_P 輸入為0 時(shí),S_en 輸出為1,然后形成反饋,S_en_P 如果保持不變的話,則此時(shí)或非門相當(dāng)于一個(gè)非門邏輯,此時(shí)構(gòu)成類似于Ring VCO 結(jié)構(gòu),此結(jié)果會造成靈敏放大器使能信號錯(cuò)誤,此干擾解決方式有三種,第一種采用較小的管子尺寸,使信號在高頻下,使反相器下拉能力較差,雖然輸出結(jié)果正常,但是輸出結(jié)果會是一個(gè)齒輪狀;第二種解決方式可通過調(diào)整管子尺寸將整體電路延時(shí)增大,類似于傳統(tǒng)PFD 結(jié)構(gòu)中消除死區(qū)的方式,使信號正常工作,通過增大延時(shí)的方式還可以是在每一級增加一個(gè)電容,電容越大,延時(shí)越大。

圖4 位線置位延時(shí)模塊

2 仿真分析

圖5 是位線置位延時(shí)模塊仿真結(jié)果圖,結(jié)果圖可知實(shí)現(xiàn)較大的延時(shí)效果,其結(jié)果在不影響靈敏放大器輸出結(jié)果同時(shí),還能保證下一次數(shù)據(jù)信號正常輸出。

圖5 位線置位延時(shí)模塊仿真結(jié)果

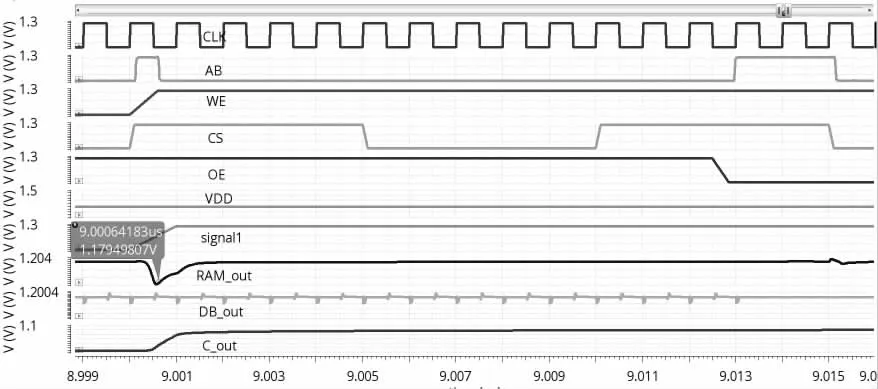

圖6 是存算整體仿真結(jié)果圖,OE、WE、CS 是邏輯燮制信號,其中VDD 是待存儲數(shù)據(jù),signal1 是計(jì)算模式使能信號,RST 則是對計(jì)算完成以后數(shù)據(jù)重置,RAM_out是存儲單元數(shù)據(jù)檢測結(jié)果,DB_out 是讀取輸出結(jié)果,net09 是計(jì)算輸出結(jié)果。從結(jié)果來看,首先存儲單元內(nèi)的數(shù)據(jù)沒有受到讀取時(shí)的干擾而改變,短暫的波動是因?yàn)镽ST 導(dǎo)通和signal1 的關(guān)閉信號有一個(gè)互擾現(xiàn)象,造成存儲數(shù)據(jù)波動。DB_out 為了保證整體電路,輸出端會有一個(gè)反向的過程,所以輸出數(shù)據(jù)與存儲數(shù)據(jù)相反。

圖6 存算整體仿真結(jié)果

3 結(jié)論

本研究所討論的存算一體電路在科研方向最前沿的研究領(lǐng)域,其市場價(jià)值也非常大。文中提到的存算單元結(jié)構(gòu)簡單,功能完善,通過驗(yàn)證結(jié)果也是與預(yù)想結(jié)果一致。通過置位延時(shí)模塊電路解決了靈敏放大器開啟過早或太晚的問題,置位延時(shí)最大的困難就是形成環(huán)振的問題,解決方法也有很多,本研究也只是采用其中一種解決辦法。