星地高速數傳系統低復雜度可重構LDPC編碼器設計

康 婧 安軍社 王冰冰②

①(中國科學院國家空間科學中心 北京 100190)

②(中國科學院大學 北京 100049)

1 引言

空間探測任務中,近地軌道(Low Earth Orbit,LEO)衛星因具有發射成本低、通信時延小和覆蓋范圍廣等優勢而被廣泛應用。隨著空間探測任務需求愈加復雜、衛星有效載荷傳感器精度不斷提高,星地鏈路傳輸數據量大大增加[1],如何在星上硬件資源、帶寬和功率受限的情況下實現高速數據傳輸已成為我國目前航天器發展需要解決的核心難題。良好的信道糾錯編碼對于提高數傳的抗干擾性、傳輸可靠性和傳輸功率受限情況下的數據傳輸容量十分重要,與高階數字調制技術相結合還可以解決帶寬受限問題[2],因此探索一種合適的信道編碼方案對當前空間通信的發展具有重要意義。

低密度奇偶校驗(Low Density Parity Check,LDPC)碼由Gallager[3]于1962年在其博士論文中提出,是一種糾錯性能逼近Shannon極限的信道編碼技術,具有譯碼復雜度低、誤碼平層低等優勢,已廣泛應用于多種通信標準,如DVB-S2, CCSDS,IEEE 802.11n等。針對航天通信應用,國際空間數據系統咨詢委員會(Consultative Committee for Space Data Systems, CCSDS)制定了《131.0-B-2遙測同步及信道編碼》標準[4],規定了近地衛星通信應用和深空通信應用的兩套LDPC碼字,其中近地衛星通信部分采用了碼率為7/8的準循環(8176,7154) LDPC碼。

CCSDS標準規定的(8176, 7154)LDPC碼是一種準循環LDPC(Quasi-Cyclic, QC-LDPC)碼,可利用循環移位寄存器實現線性復雜度的編碼[5,6]。文獻[7]實現了滿足航天應用需求的串行編碼電路,其實現復雜度低,但所需編碼時鐘周期數和信息比特位數成正比,碼長較長時編碼數據吞吐率不能滿足高速數傳需求。文獻[8]提出了一種高效低功耗低并行度的編碼方案,文獻[9-12]實現了并行度更高的編碼器。并行編碼電路可以滿足高編碼數據吞吐率要求,但其硬件資源消耗大,功耗高。文獻[13-15]提出了可重構設計思想,以改善系統性能。本文面向LEO衛星星地高速數傳系統,針對CCSDS近地衛星通信標準提出了一種低復雜度可重構LDPC編碼器設計方案,并進行了硬件實現驗證。

2 LDPC編碼算法

2.1 CCSDS標準LDPC編碼算法

LDPC 碼的編碼算法可以分為兩類:基于生成矩陣的編碼算法和基于校驗矩陣的編碼算法[16]。基于生成矩陣的編碼算法直接將生成矩陣與信息比特進行矩陣運算,這種編碼算法簡單且易于實現,但編碼復雜度高,正比于碼長的平方。而CCSDS近地衛星通信標準采用的是碼率為7/8的(8176,7154)LDPC碼,該碼是一種QC-LDPC碼,可以利用移位寄存器實現線性復雜度的編碼,其生成矩陣G是大小為7154× 8176的矩陣

基于生成矩陣的編碼算法為

2.2 并行編碼算法

為縮短編碼周期,提高編碼數據吞吐率,在CCSDS標準LDPC編碼算法基礎上,通過對輸入信息比特進行插0處理和拆分循環矩陣,可以實現并行編碼算法。具體步驟如下:

(1)以循環矩陣Bi,j的階數511為一段,將輸入信息比特u分割為14個長度為511 bit的子向量

3 低復雜度可重構LDPC編碼器

3.1 整體結構

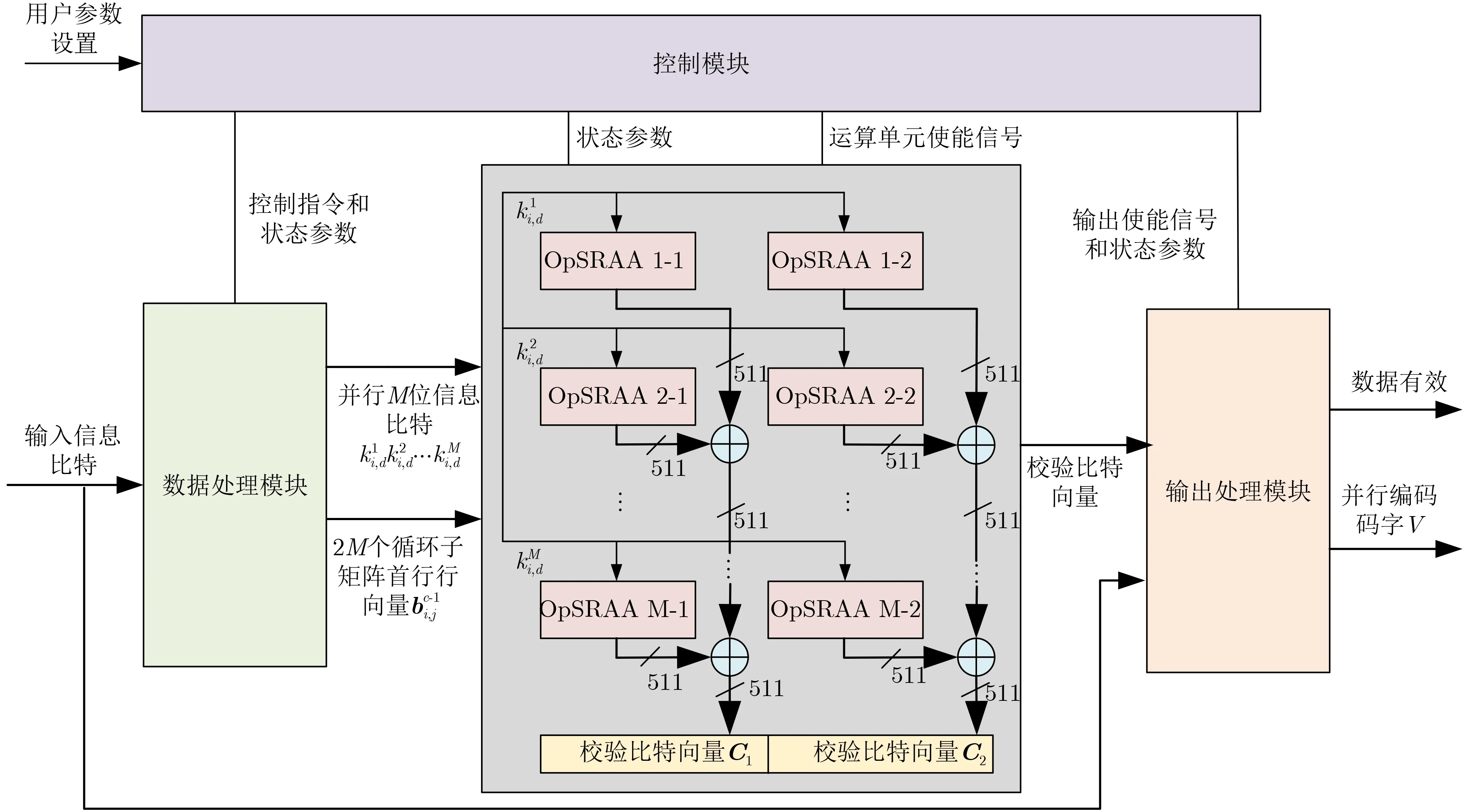

在對資源、編碼數據吞吐率要求苛刻的星地數傳系統中,應根據實際應用需求選擇合適的編碼并行度M,并行度過高,會占用大量硬件資源,并行度太低,則不能滿足編碼數據吞吐率要求,大多數文獻中的編碼器僅支持單一的編碼并行度,靈活性較差。另一方面,當今飛行器和地面系統通常只能處理32 bit倍數結構的數據,(8176, 7154)碼并不滿足這個條件,為在實際空間通信系統中獲得應用,需將(8176, 7154)碼縮短和調整為(8160, 7136)碼并在編碼時進行添加32 bit幀頭、加擾等操作[4]。針對上述需求,設計了如圖1所示的低復雜度可重構LDPC編碼器。包括控制模塊、數據處理模塊、并行編碼模塊和輸出處理模塊。

圖1 低復雜度可重構LDPC編碼器

3.2 低復雜度設計

圖2 低復雜度可重構LDPC編碼器工作流程

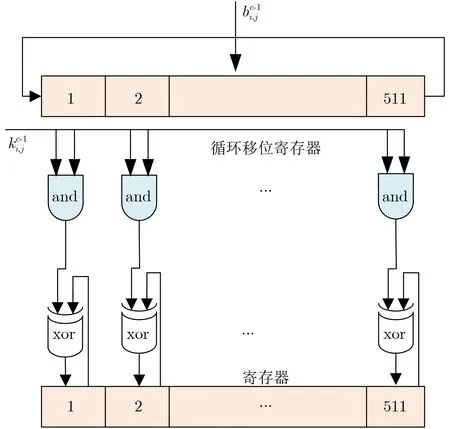

圖3 SRAA單元

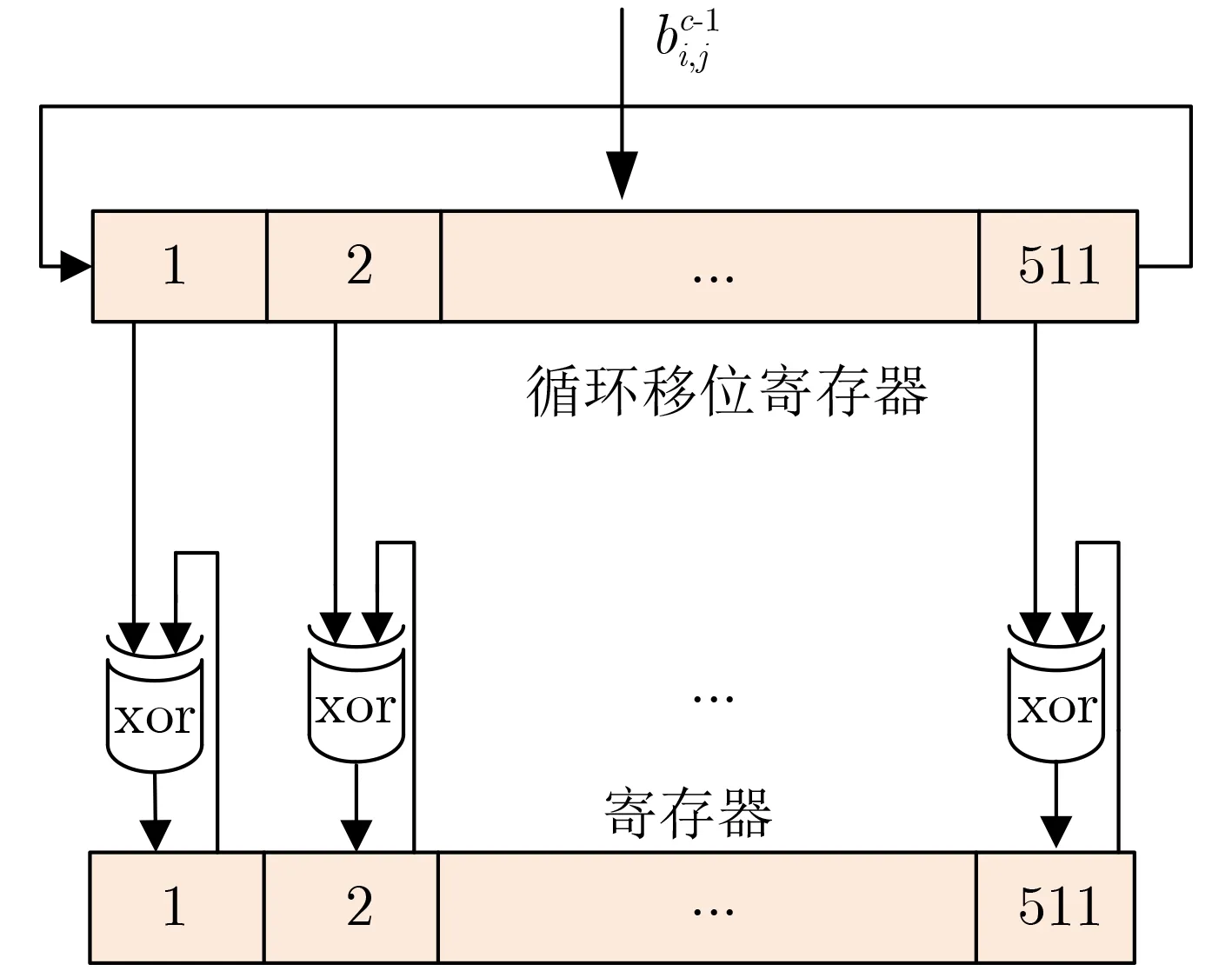

由于信息比特在二元域取值,當輸入信息比特為0時,經過與門運算的結果為0,與寄存器中的值進行異或時,不會改變寄存器中的值,因此可將SRAA進行優化,只在輸入信息比特為1時,將循環移位寄存器中的值和寄存器中的值進行異或并存儲于寄存器中。圖4為優化的移位寄存器累加單元(Optimized Shift Register Adder Accumulator,OpSRAA),該單元包括:一個位寬511 bit用于存儲異或運算結果的寄存器,一個位寬511 bit用于產生和存儲循環子矩陣行向量(d,:)的循環移位寄存器以及511個用于累加運算的二輸入異或門。

圖4 OpSRAA單元

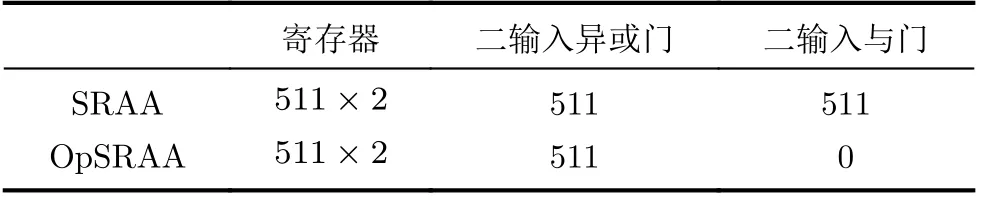

SRAA單元和OpSRAA單元所需硬件資源對比如表1所示。

表1 SRAA和OpSRAA資源對比

由以上分析知,利用2M個OpSRAA單元,經過14×N個時鐘周期即可計算得到C,可節省2×511×M個二輸入與門,降低了硬件實現復雜度。而且本文設計的OpSRAA對于具有準循環結構的編碼具有普適性,實際應用時,只需要根據生成矩陣循環矩陣階數改變寄存器的寬度和二輸入異或門的個數。

3.3 并行度可重構設計

可重構硬件設計思想是復用硬件電路中的主要資源,在增加少量控制硬件的情況下增加系統的功能或改善系統的性能[15]。本文將可重構設計思想應用于 LDPC 編碼器來改善系統性能。

綜上分析,在控制模塊的控制下,采用可重構思想設計的編碼器可以有效保證編碼器動態自適應調整以適用于不同近地衛星通信系統對編碼指標、性能的不同要求,使得所設計的編碼器具有靈活性與通用性,而且可以取得編碼數據吞吐率和資源消耗之間的良好折中。

4 實現結果與分析

4.1 編碼器硬件實現分析

對本文提出的低復雜度可重構LDPC編碼器,在Xilinx XC4VLX80-12ff1148型號FPGA上進行了實現,開發環境為ISE14.7,與其它文獻編碼器對比結果如表2所示。

文獻[8]通過插0處理和改變矩陣結構實現了2路并行編碼。文獻[11]利用矩陣轉換的概念,即只要循環矩陣的階數可以分解為兩個互質的數,那么可按照一定規則將其轉換為維度更小的塊循環矩陣,由于511=7×73,因此文獻[11]將511×511的循環矩陣轉換為73×73的塊循環矩陣實現了7路并行編碼。文獻[12]中800 Mbps數傳吞吐率需求以及Spacewire接口和組幀模塊的設計要求編碼在886個時鐘周期完成,因此設計了98路高并行度編碼。上述文獻只支持單一編碼并行度,而本文提出的編碼器通過插0處理和拆分循環矩陣支持2, 4和8 共3種編碼并行度,具有可重構性,其中控制模塊有效保證了編碼器的動態自適應調整,提高了編碼器的靈活性與通用性。

從表2可以看出,由于采用OpSRAA單元完成基本編碼運算,本文提出的編碼器寄存器資源、查找表資源與文獻[8]采用SRAA單元的編碼器相比分別節約了13.7%和14.8%,具有低實現復雜度。文獻[11]根據轉換的塊循環矩陣結構和向量乘法運算規則,利用2個并行移位寄存器累加單元(Parallel Shift Register Adder Accumulator, PSRAA)實現編碼,且由于編碼并行度7是CCSDS標準循環矩陣階數511的約數,可以將信息比特序列直接分割,節省了插0處理需要的硬件邏輯,而本文為兼容多種編碼并行度,采用了最大化備份編碼策略,因此總體寄存器資源和查找表資源消耗比文獻[11]多。但文獻[11]設計的PSRAA需消耗2×73個7比特寄存器、7×511個 2 輸入與門、7×511個2輸入異或門和146個矩陣向量乘法運算單元,具有針對性,而本文設計的OpSRAA單元只需要2個511 bit寄存器和511個二輸入異或門,相較于PSRAA具有低復雜度,且對于具有準循環結構的編碼具有普適性,實際應用時,只需要根據循環矩陣階數改變寄存器的寬度和異或門的個數。文獻[12]的編碼器是針對OFDM鏈路而設計,除包括核心編碼模塊還包括輸入輸出組幀模塊、數據緩存等模塊,因此硬件資源占用較多。

表2 不同文獻編碼器對比

4.2 編碼器性能分析

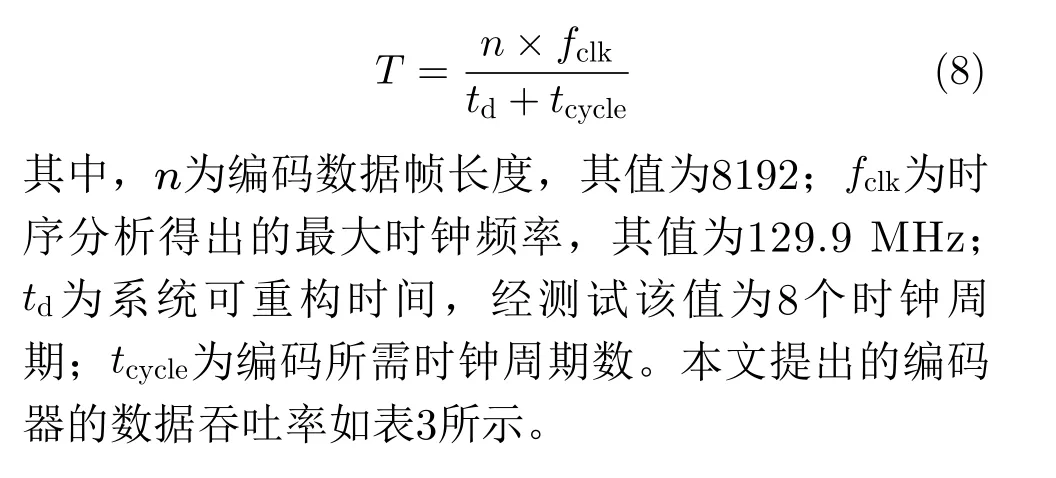

編碼數據吞吐率是衡量編碼器性能的一個重要指標。對于航天應用編碼器,考慮其可靠性和功耗約束,將系統時鐘約束為125 MHz,借助Timing Analyzer工具,對本文編碼器進行時序分析,并按式(8)計算編碼數據吞吐率

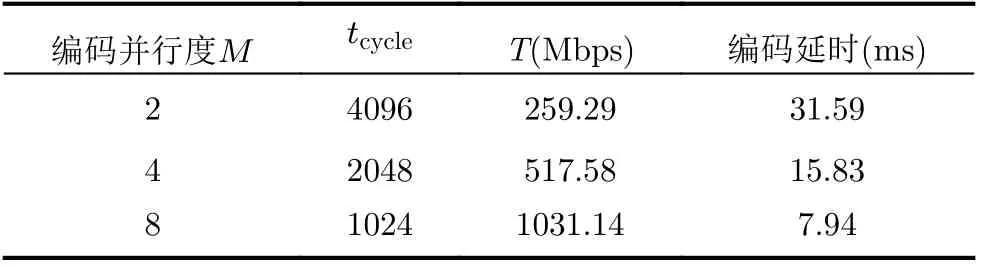

表3 本文編碼器吞吐率

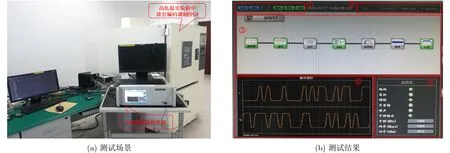

為進一步驗證本文編碼器的可行性及有效性,搭建如圖5(a)所示硬件平臺對該編碼器進行實際測試并利用高速數據接收終端對其進行狀態參數監控。測試時,設置編碼調制FPGA系統時鐘為125 MHz,LDPC編碼器并行度為8,數字調制方式為QPSK,測試結果如圖5(b)所示。

圖5(b)中“①”指示硬件健康狀態,顯示當前編碼調制通道的網絡連接、外設驅動、FPGA溫度、硬件電壓等狀態,綠色表示正常的硬件狀態,藍色表示正常的網絡連接。“②”指示編碼調制通道固件及基本性能,包括編碼調制通道、FPGA固件版本以及支持的中頻和調制符號速率范圍。“③”指示編碼調制流程圖,綠色表示該模塊正常工作,灰色表示該模塊被旁路,從圖中可看到數據源經LDPC編碼和QPSK調制后輸出。“④”顯示I, Q調制基帶波形的時域圖,便于用戶觀察調制數據。“⑤”為編碼調制狀態參數顯示,包括編碼開關、卷積開關、調制開關、中頻、噪聲、碼率、功率等信息,從圖中可看到實測編碼數據吞吐率為1 Gbps。

圖5 測試場景與測試結果

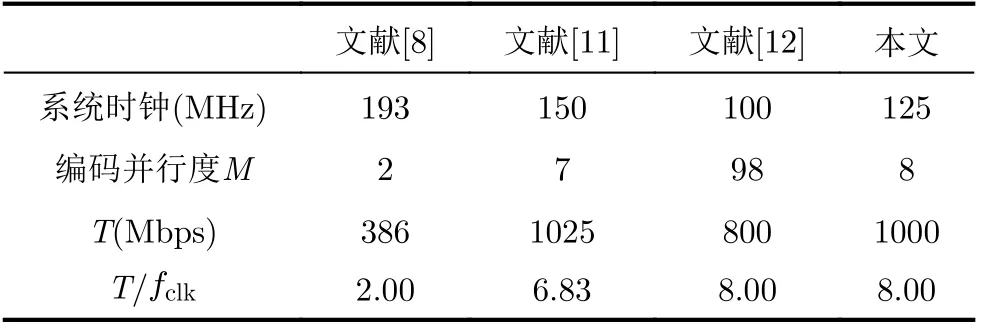

系統時鐘直接影響編碼數據吞吐率的大小,而系統時鐘會受硬件平臺影響,因此本文對系統時鐘進行歸一化處理,比較歸一化編碼數據吞吐率。本文與其它編碼器歸一化編碼數據吞吐率比較如表4所示。

由表4可以看出,與文獻[11]設計的7路并行編碼器相比,本文歸一化編碼數據吞吐率提高了17.1%,文獻[12]采用98路并行編碼達到了和本文相同的歸一化編碼數據吞吐率。由此可見,本文設計的編碼器更高效。

表4 不同文獻歸一化編碼器吞吐率對比

綜上分析,本文提出的低復雜度可重構LDPC編碼器,降低了硬件資源規模,提高了編碼數據吞吐率,實現了硬件資源和編碼數據吞吐率之間的動態平衡,而且能夠兼容3種編碼并行度,提高了編碼器的靈活性,可以滿足不同衛星通信系統的要求。

5 結束語

本文面向LEO衛星星地高速數傳系統對高通量、低復雜度、高可靠性信道編碼的應用需求,提出了一種低復雜度可重構LDPC編碼器。通過對輸入信息比特插0處理、拆分循環矩陣并動態重構編碼電路,實現了并行度可重構編碼,提高了編碼器的靈活性與編碼數據吞吐率;采用OpSRAA 結構顯著降低了編碼器硬件資源。FPGA實現結果表明,本文設計的編碼器,在系統時鐘為125 MHz時,采用8路并行編碼最高編碼數據吞吐率可達1 Gbps,歸一化編碼數據吞吐率與并行度相近的編碼器相比提高了17.1%,且寄存器資源和查找表資源與相同平臺已有方案相比分別降低了13.7%和14.8%。綜上,本文設計的編碼器在對資源、功耗、編碼數據吞吐率要求苛刻的LEO衛星星地高速數傳系統中具有較高應用價值。