輻射發生器的設計

凌濤

(東華理工大學機械與工程技術學院,江西南昌,330032)

0 引言

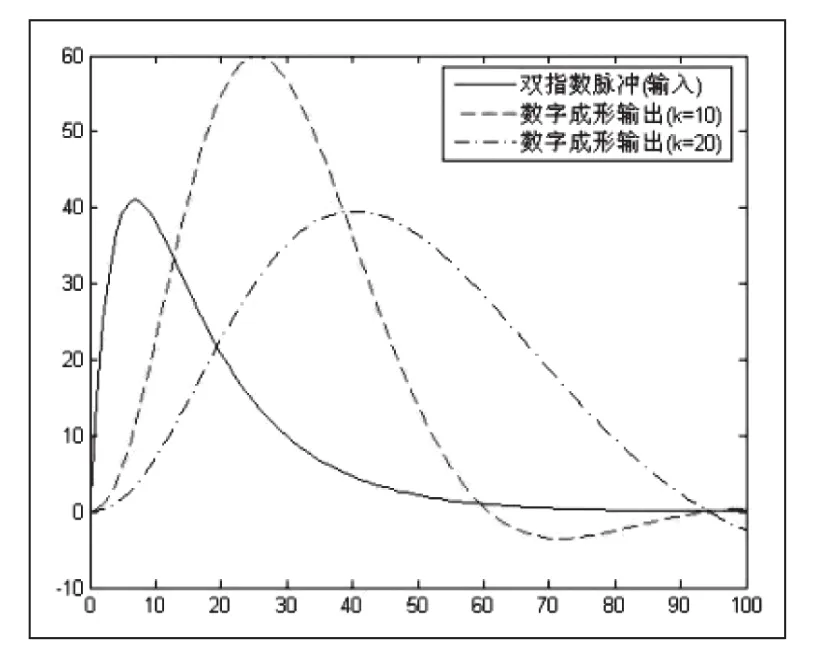

理想的通過核輻射探測器輸出的核脈沖信號是一個負指數脈沖信號(射線本身可看作單位沖激信號)[1],但是實際上,射線經過放射性探頭自身(如晶體、半導體、氣體等)及其配套部件(如光電倍增管等)的轉化后,會成為雙指數脈沖信號,如圖1所示,相當于電子學里面對沖激響應的積分和微分過程。但不同類型的探測器輸出核脈沖的前沿、后沿的衰減時間會各有不同,即可看作積分和微分時間常數各有不同。

圖1 雙指數型核脈沖信號

最早的輻射信號發生器有模擬電路產生[1],后來又有單片機和FPCA為核心來設計[2],分別采用函數法,余數法,中心極限定理法和Box-Muller變換法[3][4]。

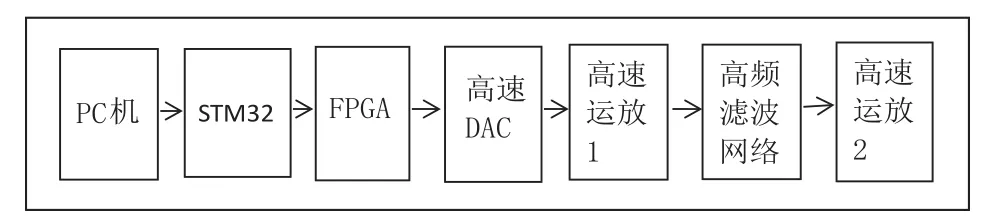

因此一個簡單的核脈沖發生器可設計成一個雙指數信號發生器,其脈沖幅度、 前沿積分時間常數、后沿微分時間常數、脈沖發生頻率均可在線調節即可。原理框圖如圖2所示。

圖2 核脈沖發生器原理框圖

在圖2中,由PC機向便攜式核脈沖發生器傳送脈沖幅度、前沿積分時間常數、前沿積分時間常數、后沿微分時間常數、脈沖發生頻率等命令,STM32將相關命令保存到數組中,同時利用STM32通過脈沖幅度和前/后沿時間常數調用指數函數計算各個點數據。STM32將所有點的幅度數據傳遞到FPGA的ram中,FPGA根據固定或指定的頻率向高速DAC發送數據,請求將數字信號轉換為模擬信號,并通過高速運放1將電流信號轉換電壓信號,并進行放大處理后由高頻濾波網絡消除掉DAC轉換過程中出現的階梯毛刺。

1 雙指數信號算法

式(1)中,X表示信號的時間值,A表示雙指數信號的前沿時間常數(可等效為前沿積分時間常數),B表示雙指數信號的后延時間常數(等效為后延微分常數),Y表示信號隨時間變化的幅值。

具體方法即通過在MDK5上函數產生呈雙指數分布的一定個數的幅值數據,再將產生的數據保存在芯片本身的數組中,作為信號的原始數據;

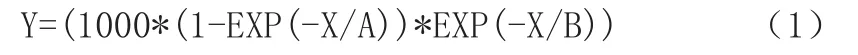

2 SPI數據通信模塊

STM32單片機與FPGA之間的數據通信采用SPI通信,其實物連接如圖3;將單片機PA4,PA5,PA7依次連接到FPGA開發板J2的3,5,7口,作為數據通信接口進行數據傳輸。

圖3 SPI通信連接圖

同樣,用MDK5編譯軟件編寫SPI通信協議以及傳輸函數,主要設置SPI的通信模式,一次傳輸位數,傳輸速率,時鐘特性和時鐘相位等;這些參數設置好后就可以進行數據傳輸了。

3 FPGA設計模塊

FPGA主要采用的是由上而下的設計思路,具體設計如圖4所示。

圖4 FPGA設計模塊

如圖4所示,其主要包括按鍵發送模塊,SPI接收模塊,雙端口RAM存儲發送模塊,數據發送模塊以及DA模塊;數據以16位數據串的形式發送給FPGA芯片的緩存區,作為DA轉換的固定的脈沖源,將緩存區的數據循環讀出,經過AN9767芯片的數模轉換,將雙指數的幅值數據轉換為電流輸出,再經過一級運放將電流轉換為電壓輸出,其次經過濾波器濾波,最后再用一個二級運放進行電壓放大作為信號輸出;以此得到一個簡單的雙指數型核脈沖信號,可以實現如圖1的雙指數信號輸出;其前沿積分時間常數,后延微分常數,頻率,幅值常數都可以根據現實需要進行設置調節。

4 高速DA轉換

DA轉換模塊采用的是AN9767,其主要參數包括:DA轉換芯片:AD9767;通道數:2通道;DA轉換位數:14bit;DA更新速率:125MSPS;輸出電壓范圍:-5V~+5V;完全能滿足本設計需要。FPGA開發板與AN9767實物連接如圖5所示。

圖5 FPGA開發板與AN9767連接圖

5 輻射信號發生器平臺的實現與測試

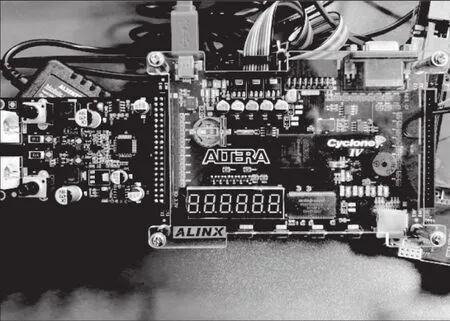

FPGA芯片采用Altera公司的FPGA芯片颶風,四代EP4CE6F17C8N;STM32芯片采用STM32F 103ZET6。搭建的實驗平臺實物如圖6所示。

圖6 完整系統實物圖

實驗步驟如下:將各個模塊通過杜邦線正確的連接起來,接通電路的電源,將程序下載到開發板中,然后將FPGA產生波形信號輸入到DAC電路模塊,經過DA轉換后的結果將在TDS3032上顯示。

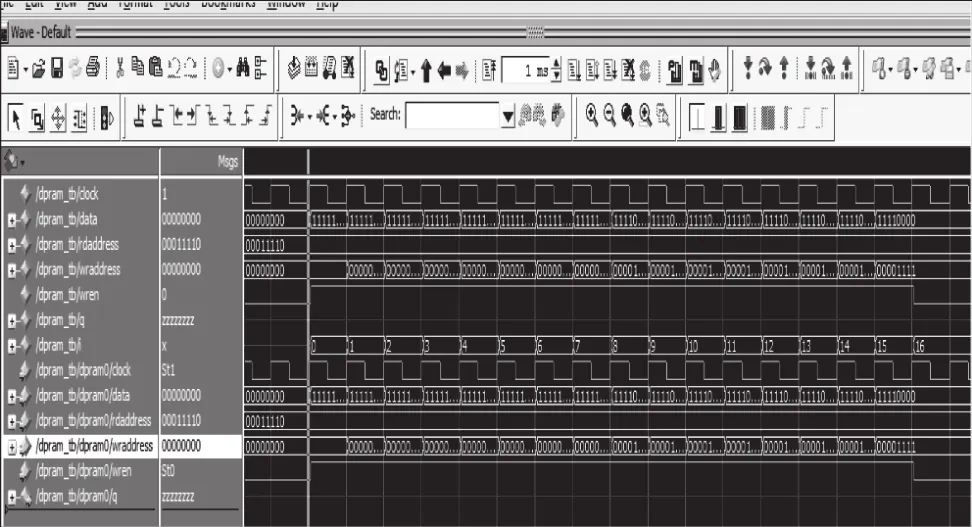

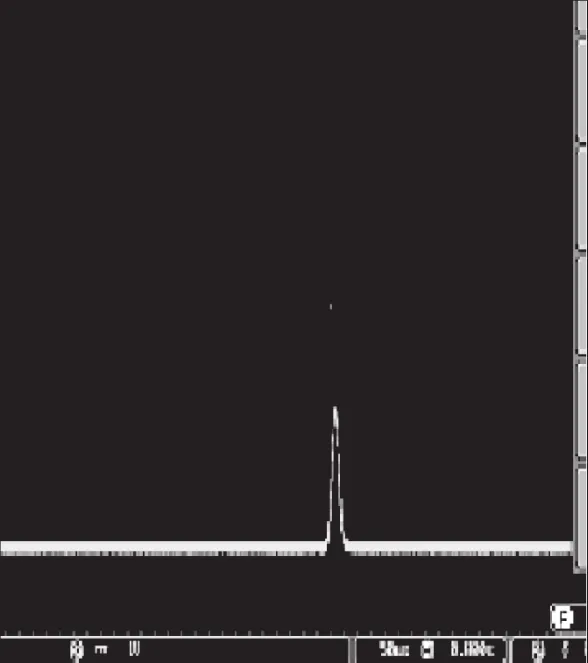

在MDK5上將信號的初始幅值設置為4,前后延常數設置為8,然后頻率設置為50MHz,再將通信模式設置為主模式,數據傳輸為16位,時鐘相位為高,時鐘極性為0;同時用quartus 軟件將FPGA程序用JTAG下載到FPGA開發板,可以得到其RTL視圖;仿真軟件用的是Modelsim 10.1,其仿真如圖7所示,是一段將一個16位數據以此寫入ram內核里,同時其地址依次增加;然后進行引腳分配;最后是用TDS3032示波器觀察DA通過BNC線觀察轉換輸出雙指數脈沖波形,如圖8所示,其脈寬約為8μs幅值約為4v,基本符合設計要求。

圖7 Modelsim仿真圖

圖8 示波器輸出測試圖

6 結論

通過STM32單片機和FPGA開發板為核心設計,以C和Verilog HDL語言進行軟件編程,可以設計出一個簡易的輻射信號發生器,為以后復雜的輻射信號發生器的設計提供了思路。