電荷泵鎖相環行為級建模研究

謝寧波,高健超

(1.桂林電子科技大學 信息與通信學院,廣西 桂林 541004;2.桂林市桂電中學教務處,廣西 桂林 541004)

0 引 言

在現代通信系統中,穩定而精準的時鐘電路是系統正常工作必不可少的基本模塊。其中,傳統的壓控振蕩器(Voltage Controlled Oscillator,VCO)因功耗高、穩定性差、頻率范圍窄且難以集成等缺點,已不能滿足現代高性能電子設備的需求,采用鎖相回路構建高穩定性、寬頻帶輸出的頻率合成器是當今的主流解決方案[1,2]。

另外,基于鎖相環實現的高速頻率合成器電路設計復雜,涉及多模塊的結構及參數設計優化,如果直接基于傳統的晶體管級電路設計流程進行電路搭建、仿真、結果分析、結構調整進而迭代,那么該方法將面臨仿真數據量大、耗時長以及誤差積累嚴重等問題。為此,本文從PLL的系統行為級建模出發,基于Verilog-AMS語言對PLL環路進行建模描述。通過EDA仿真實驗驗證環路參數對系統的影響,并通過參數迭代優化提升系統的性能指標。行為級建模仿真可有效減少仿真耗時和設計的復雜度,對電路級設計具有前瞻性的指導意義。

1 PLL系統結構

典型的基于電荷泵的鎖相環由鑒相器(Phase Detector,PD)、電荷泵、環路濾波器、壓控振蕩器以及分頻器5部分構成,其結構如圖1所示。

圖1 典型PLL結構

鎖相環是一種典型的反饋控制電路,其中鑒相器用于比較外部參考信號與反饋信號之間的相位和頻率差,將比較出來的相位差轉換為電壓信號輸出給電荷泵。電荷泵受鑒相器輸出信號控制,以電流源對后級充放電的方式為壓控振蕩器提供控制電壓。環路濾波器的目的是過濾環路中的噪聲和高頻毛刺,以增強環路穩定性。壓控振蕩器作為環路的核心,受電荷泵輸出的電壓控制,其輸出的信號頻率受反饋環路的控制逐漸逼近目標頻率和相位。而分頻器將鎖相環的輸出信號和輸入參考時鐘的頻率形成一個倍數關系,最終在環路平衡時完成環路鎖定。

2 PLL行為級建模

2.1 環路參數計算

PLL的設計涉及到多模塊的參數選擇,主要包括鑒相器的增益系數KPD、壓控振蕩器的增益系數KVCO、環路濾波器的器件參數及帶寬ωbw以及分頻器的分頻倍數N。這些參數對系統的穩定性和環路鎖定時間起到決定性的作用,對其進行研究和分析是行為級建模的目的和意義。通過分析環路的傳輸函數,可對上述參量的選擇作進一步的分析。

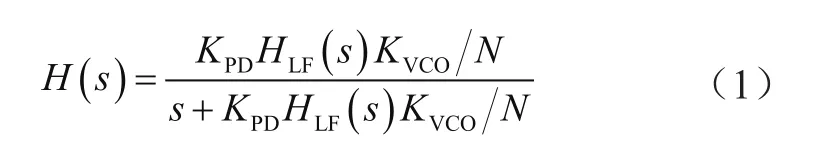

已有大量文獻對環路參數的計算作詳實的分析,現簡單總結如下[3-5]。環路的閉環傳輸函數表示為:

2.2 模塊行為級建模

2.2.1 鑒相器

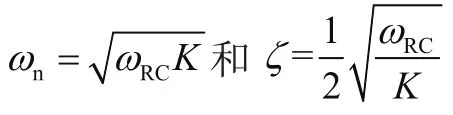

鑒相器的作用是將參考信號與反饋信號之間的相位差轉換為電壓信號UP和DOWN,以控制電荷泵輸出。不同于晶體管級電路設計,在行為級建模上,該模塊的工作原理本質上可視為輸出狀態的轉移,其狀態轉移過程可簡化為如圖2所示。

圖2 鑒相器行為級建模狀態轉移

其工作過程簡單介紹如下,假設參考信號和反饋信號之間存在相位差且初始狀態為IDLE,如果鑒相器PD檢測到REF信號時鐘上沿先于DIV信號到來,則轉為UP狀態,UP信號輸出為高。下一步,如果PD檢測到的依然是REF的時鐘上升沿,則保持當前狀態,如果檢測到的是DIV時鐘沿,則此時轉為RST狀態,反之亦然。值得注意的是,鑒相器不存在UP和DOWN同時為“1”的狀態。

2.2.2 電荷泵

電荷泵由PD輸出的UP和DOWN信號控制,其原理可等效視為一個受UP和DOWN電壓信號所控制的為負載電容進行充放電的通路。一般而言,典型的電荷泵通路可等效視為正向充電的電流源和反向放電的電流源構成,行為級建模時以兩個理想電流源Ip和In來表示。

2.2.3 環路濾波器

典型的PLL環路濾波器由二階RC電路構成。其行為級建模可直接調用Verilog-AMS語言的內建原語resistor和capacitor來實現,同時調用及例化時需要注意端口匹配。此外,器件參數初始選擇參考環路參數計算,后續仿真驗證時會根據仿真結果對其作調整優化。

2.2.4 壓控振蕩器

壓控振蕩器的電路模型為:

式中:ωout為VCO的瞬時輸出頻率;ω0為VCO的中心頻率;KVCO為VCO的頻率增益系數,理想化模型下是一個常數;Ucont為VCO的控制電壓,即電荷泵的輸出電壓。

上述模型是頻域模型,行為級建模時需要對應到時域模型,其本質上是角頻率對時間的積分,故對VCO進行行為級建模可利用內建的積分函數idt( )及信號的正弦表示來實現。

2.2.5 整數分頻器

為簡化系統分析,本設計所使用的分頻器采用整數分頻,暫不涉及小數分頻,故分頻器的行為級建模利用簡單的計數器來描述。通過設置一個變量count用作計數,使用cross( )函數對VCO輸出的時鐘沿作統計,當計數到設置的閾值則輸出分頻信號。

2.3 系統級建模設計

在完成各模塊建模的前提下,將各模塊按照系統結構順序連接組合即可得到系統層面的行為級建模。具體來說,先完成分模塊的行為級描述并創建獨立的文件,進而例化各模塊并利用端口映射關系完成系統各模塊的連接和信號傳遞。為簡化仿真過程,可以把需要迭代優化的參量全部寫在一個參量定義文件中,利用參數傳遞的方式進行迭代修改。

3 系統仿真驗證

仿真和驗證的功能是檢查設計的正確性,同時也是系統不斷修正、改進以及優化的過程。為整個系統設計一套比較完善的驗證方案,驗證系統的功能正確性并總結分析影響系統穩定性和性能的參數作用機制。

3.1 設計參數指標

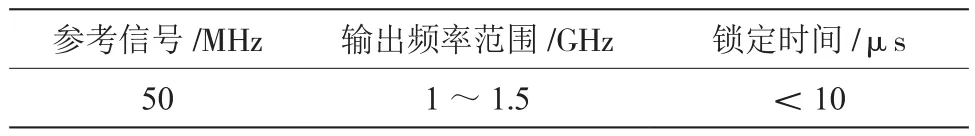

由于行為級建模僅為電路級設計的參考和指導,并不限定于具體的應用需求,故本設計的參數指標設定進行了一定的簡化。本設計的參數指標描述如表1所示。

表1 系統參數指標

3.2 功能驗證

通過驗證環路是否能跟蹤參考信號變化并成功鎖定來驗證設計的正確性。從圖3(a)可得REF信號和DIV信號已達到相位鎖定,同時VCO輸出的信號頻率與設計的分頻倍數相符合。圖3(b)反映了鎖相過程中VCO控制電壓的變化趨勢,相位鎖定過程大約需要3.8 μs,符合預期,且信號的紋波在可接受范圍。

圖3 環路瞬態仿真結果

3.3 環路參數對系統性能的影響

研究環路參數對系統的穩定性和環路鎖定時間的影響是行為級建模的目的和意義,對后續電路級設計和迭代優化具有前瞻性的指導作用。這里主要分析電荷泵充放電電流、環路濾波器選擇以及VCO增益系數對設計的影響,通過仿真結果分析可總結如下。

一是VCO控制電壓的增益與充放電電流成正比,同時充放電電流的不匹配會在一定程度上影響環路的鎖定時間。當充放電電流失配時,鎖定時間比電流匹配時增加了幾百納秒的時間,故電路級設計時應盡量滿足充放電電流的匹配。二是環路濾波器的設計對系統的穩定性和鎖定時間有極大的影響,且兩者是一對互相牽制的參數指標。三是VCO的增益系數在實際模型中與控制電壓不再是線性關系,其非線性關系會使得PLL的鎖定時間變長,且會引起抖動或失鎖問題,故電路級設計時需考慮從電路結構或者器件特性上盡量避免非線性問題。

4 結 論

本文系統總結了基于Verilog-AMS的電荷泵鎖相環行為級建模的方法和相關理論研究,通過仿真實驗驗證了設計的正確性,并針對環路參數對系統穩定性和性能的影響等相關問題進行較為充分的分析,從而為后續的電路級設計提供重要的理論依據和指導作用。