虛擬示波器硬件設(shè)計

李鴻松,武 錦,李澤宏,周 磊,季爾優(yōu)

(1.電子科技大學(xué)電子科學(xué)與工程學(xué)院,成都 610054;2.中國科學(xué)院微電子研究所,北京 100029)

1 引言

示波器是一種功能眾多的電子測量測試儀器,可以將肉眼看不見的模擬信號轉(zhuǎn)換為肉眼可見的波形圖像,便于人們研究和分析處理模擬信號。虛擬儀器是以計算機(jī)軟件為核心,功能可以由用戶自由定義、修改和設(shè)計,具有虛擬面板的一種新型儀器模式。基于虛擬儀器的思想,本文提出了一種基于FPGA和國產(chǎn)ADC芯片的虛擬示波器的硬件結(jié)構(gòu)設(shè)計和實(shí)現(xiàn)方案。該方案以FPGA作為主邏輯控制單元,當(dāng)硬件電路檢測到模擬信號輸入時,經(jīng)過模擬前端處理和AD轉(zhuǎn)換,在時鐘信號控制下將轉(zhuǎn)換后的數(shù)字信號同步到FPGA控制的存儲單元中,最后通過PCIE接口傳輸至上位機(jī)完成信號處理、分析、測量、顯示等功能。

虛擬儀器是一種新型儀器模式,通過電子儀器與計算機(jī)應(yīng)用深層次結(jié)合而成,比傳統(tǒng)儀器和一般智能儀器具有更強(qiáng)大的功能,是儀器發(fā)展的又一次飛躍。虛擬示波器就是虛擬儀器的一種,可以實(shí)現(xiàn)傳統(tǒng)示波器大部分的功能,而且在很大程度上有著傳統(tǒng)示波器無法比擬的優(yōu)點(diǎn),比如豐富齊全的功能、使用簡單靈活和低廉的價格等。

2 總體硬件結(jié)構(gòu)設(shè)計

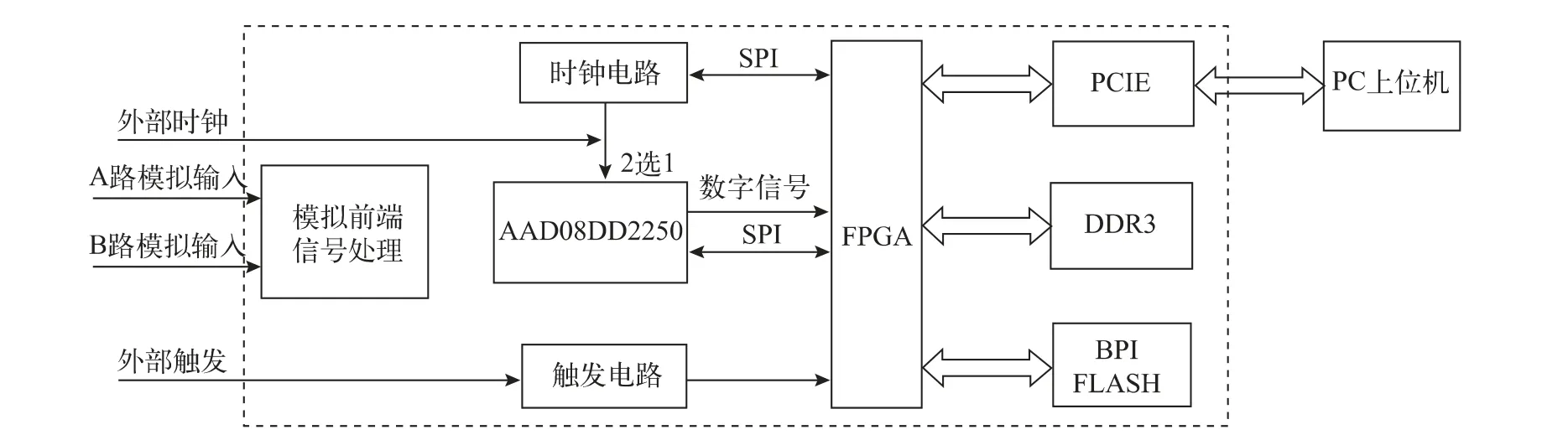

本次設(shè)計是基于數(shù)據(jù)采集上的虛擬儀器系統(tǒng)方案來完成實(shí)現(xiàn)的虛擬示波器功能,通過FPGA與ADC完成數(shù)據(jù)采集并借助于上位機(jī)來完成各種信號的處理、分析、顯示和存儲等功能[1],其硬件結(jié)構(gòu)如圖1所示。

圖1 系統(tǒng)硬件結(jié)構(gòu)

本文采用FPGA在整個硬件電路作為主邏輯控制單元完成外部輸入信號的采集工作。當(dāng)硬件電路檢測有外部模擬信號進(jìn)入時,首先通過模擬前端信號處理電路完成對信號的衰減放大等處理,能夠使該輸入信號幅值滿足ADC轉(zhuǎn)換電路的輸入要求;之后ADC將其接收到的模擬信號轉(zhuǎn)換為數(shù)字信號并在時鐘信號的控制下同步輸入到FPGA控制電路的存儲單元中;最后通過PCIE接口將數(shù)據(jù)傳輸至計算機(jī),再由相應(yīng)的應(yīng)用軟件完成信號的處理和參數(shù)測量、頻譜分析、波形顯示等工作。

2.1 模擬前端

模擬前端處理就是一個信號調(diào)理電路處理的過程,是指把來自傳感器或外界輸入的模擬信號經(jīng)過衰減、放大和濾波等操作后,轉(zhuǎn)換為可用于數(shù)據(jù)采集、分析處理和計算顯示等其他目的,且更容易存儲、處理的數(shù)字信號的電路過程。其電路的作用有兩個:一是通過衰減和放大電路將被測模擬信號的幅值調(diào)整至符號ADC芯片要求范圍以內(nèi),保證ADC采樣測試有較大的動態(tài)范圍;二是為了不對被測模擬信號產(chǎn)生其他影響,同時需要保證調(diào)理電路有高的輸入阻抗[2-3]。

本文設(shè)計的模擬前端信號調(diào)理電路結(jié)構(gòu)如圖2所示。由于在數(shù)據(jù)采集過程中信號大小是未知的,為了防止因采樣信號過大損壞信號調(diào)理電路中的其他器件,在采樣信號進(jìn)入前加入了由兩個二極管組成的輸入保護(hù)電路。衰減網(wǎng)絡(luò)主要是利用電阻分壓,再加上用于頻率補(bǔ)償?shù)碾娮韬碗娙萁M成[4],并通過繼電器來選擇多少大小的衰減。同時增加直流偏置模塊對被測信號偏置電壓進(jìn)行調(diào)節(jié),進(jìn)而實(shí)現(xiàn)波形顯示偏置調(diào)節(jié)。選用了一款低噪聲、低功耗全差分放大器LMH5401將衰減后的被測單端信號轉(zhuǎn)換為差分信號,再通過一個可調(diào)增益放大器實(shí)現(xiàn)信號的放大,最后通過低通濾波器去除掉高頻分量和干擾的噪聲進(jìn)入到ADC模數(shù)轉(zhuǎn)換器中。

圖2 模擬前端結(jié)構(gòu)

2.2 ADC模數(shù)轉(zhuǎn)換

2.2.1 ADC芯片簡介

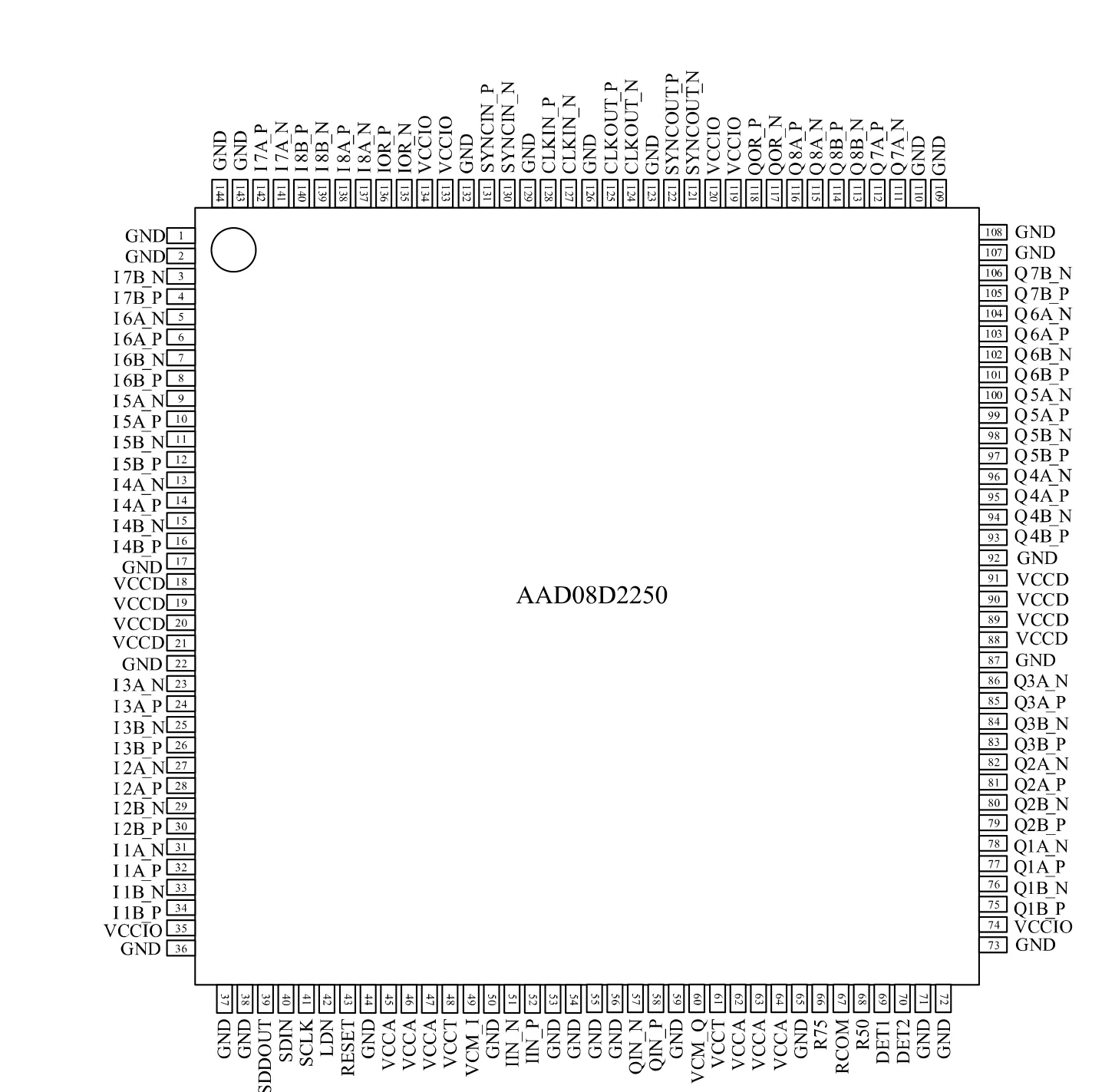

ADC模數(shù)轉(zhuǎn)換器是將連續(xù)的模擬信號轉(zhuǎn)換為離散數(shù)字信號的器件,也是測試測量領(lǐng)域中關(guān)于數(shù)據(jù)采集硬件系統(tǒng)的核心器件[5]。本次設(shè)計選用全國產(chǎn)的ADC芯片AAD08D2250,是采用硅基工藝制造的高速寬帶模數(shù)轉(zhuǎn)換器。該芯片可將差分420 mV輸入模擬信號轉(zhuǎn)換成8 bit數(shù)字信號,芯片內(nèi)包含2個最高工作在2.5 GS/s的子ADC,可工作在交織和非交織模式,在對數(shù)據(jù)進(jìn)行2倍解復(fù)用(Demux)之后通過LVDS接口輸出。輸出信號包括1路時鐘(2或4分頻)、32路數(shù)據(jù)輸出以及2路超量程比特輸出,均為LVDS電平標(biāo)準(zhǔn)。芯片采用+4.6 V/+3.3 V/+1.8 V電源供電,總功耗約為4.2 W。芯片有144個引腳,為增強(qiáng)型導(dǎo)熱焊盤LQFP封裝,芯片封裝及引腳如圖3所示。

圖3 AAD08D2250封裝結(jié)構(gòu)

管腳INI_P/INI_N和INI_Q/INI_Q為2路模擬信號輸入通道,單路輸入時最高采樣率為2.5 GS/s,雙路輸入時交織狀態(tài)下最高采樣率為5 GS/s;I1A-I8A和Q1A-Q8A、I1B-I8B、Q1B-Q8B為32對差分?jǐn)?shù)據(jù)輸出端口;SDOUT和SDIN、SCLK、LDN為4線SPI接口,用于對ADC芯片的功能配置及性能校準(zhǔn)。

2.2.2 ADC芯片特點(diǎn)

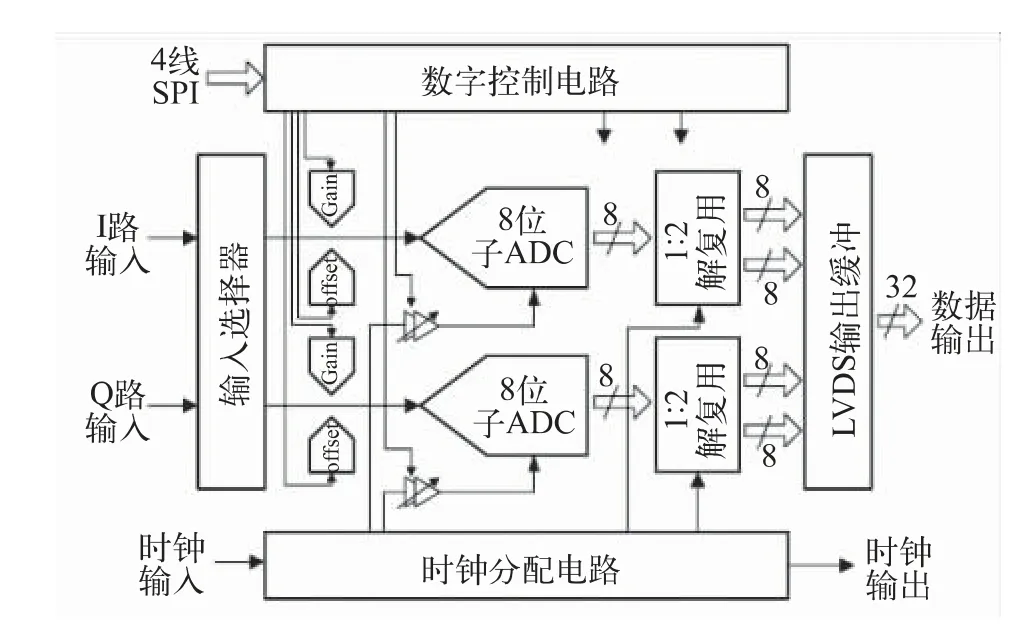

AAD08D2250高速寬帶模數(shù)轉(zhuǎn)換器電路結(jié)構(gòu)如圖4所示。根據(jù)虛擬示波器的性能要求,其主要性能指標(biāo)如下。

圖4 AAD08D2250內(nèi)部結(jié)構(gòu)

(1)分辨率:8 bit;

(2)采樣精度:雙通道模式1~2.5 GS/s,單通道模式2~5 GS/s;

(3)輸入信號帶寬:3.5 GHz;

(4)ENOB:6.4 bit;

(5)功耗:4.2 W;

(6)芯片封裝形式:LQFP。

2.3 PCIE接口電路

2.3.1 PCIE總線簡介

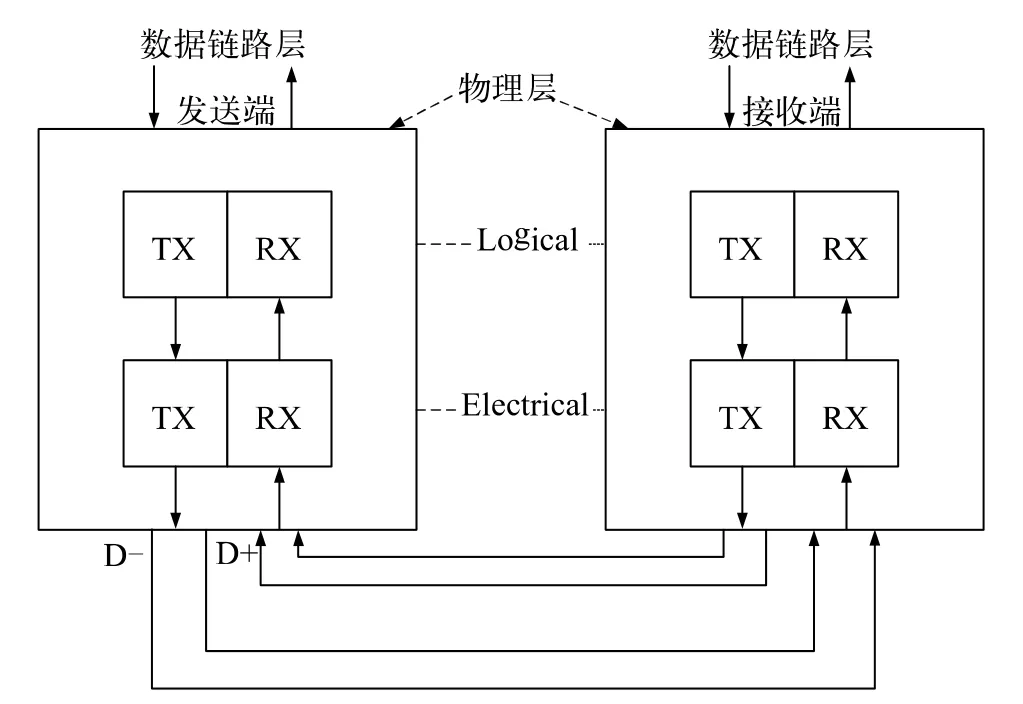

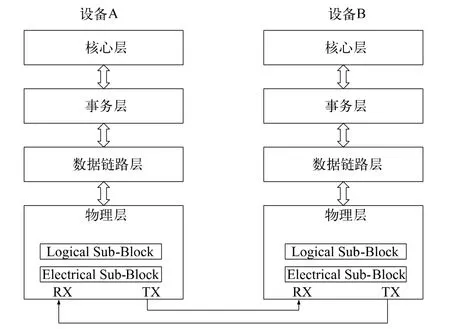

隨著高速串行計算機(jī)擴(kuò)展總線標(biāo)準(zhǔn)(PCIE)技術(shù)的發(fā)展逐漸成熟,同時為了滿足高速率的數(shù)據(jù)傳輸要求,越來越多的數(shù)據(jù)采集設(shè)備使用了PCIE接口進(jìn)行數(shù)據(jù)傳輸[6]。PCIE總線采用的是高速差分信號線連接發(fā)送端和接收端而成,其總線鏈路結(jié)構(gòu)如圖5所示。PCIE總線上的數(shù)據(jù)發(fā)送端和數(shù)據(jù)接收端分別連接在PCIE鏈路的兩端,形成一個數(shù)據(jù)傳輸通道。除了總線鏈路外,PCIE總線在發(fā)送和接收數(shù)據(jù)時還被劃分為多個層次。PCIE的總線層次結(jié)構(gòu)與網(wǎng)絡(luò)協(xié)議相仿,但與一般的計算機(jī)網(wǎng)絡(luò)協(xié)議不同的是PCIE總線采用硬件邏輯來實(shí)現(xiàn)不同層次的功能[7]。

圖5 PCIE總線的物理鏈路結(jié)構(gòu)框圖

由圖5所示,在PCIE總線物理鏈路的每個數(shù)據(jù)通路(Lane)中,包含2組發(fā)送和接收的差分信號。其中發(fā)送端的發(fā)送鏈路同時也是接收端的接收鏈路,由一組差分信號連接發(fā)送端的TX部分與接收端的RX部分組成;而發(fā)送端的接收鏈路同時也是接收端的發(fā)送鏈路,使用另一組差分信號連接發(fā)送端的RX部分與接收端的TX部分組成[8]。每一個PCIE鏈路都可以由單個或多個Lane組成。

2.3.2 PCIE總線的層次結(jié)構(gòu)

PCIE總線采用了串行通信連接方式,在其發(fā)送和接收時數(shù)據(jù)使用數(shù)據(jù)包(Packet)來進(jìn)行數(shù)據(jù)傳輸,很大程度上去除了在PCI總線中存在的某些邊帶信號,如INTx和PME#等信號。如圖6所示為PCIE總線的層次結(jié)構(gòu),通過其層次結(jié)構(gòu)可知數(shù)據(jù)包在PCIE總線的收發(fā)過程中需要依次通過包括設(shè)備核心層、事務(wù)層、數(shù)據(jù)鏈路層和物理層等在內(nèi)的多個層次[7]。

圖6 PCIE總線的層次結(jié)構(gòu)框圖

在某種程度上PCIE的層次結(jié)構(gòu)類似于網(wǎng)絡(luò)的層次結(jié)構(gòu),但是PCIE總線的每個層次結(jié)構(gòu)都是通過硬件邏輯來完成實(shí)現(xiàn)的。在PCIE總線收發(fā)數(shù)據(jù)的層次結(jié)構(gòu)中,首先報文數(shù)據(jù)通過發(fā)送端設(shè)備的核心層中產(chǎn)生,依次經(jīng)過事務(wù)層的封裝、數(shù)據(jù)鏈路層的可靠性處理和物理層封裝后發(fā)送至其他設(shè)備。接收端設(shè)備的物理層接收到數(shù)據(jù)報文后經(jīng)數(shù)據(jù)鏈路層、事務(wù)層處理,最后到達(dá)核心層。其中在發(fā)送數(shù)據(jù)時事務(wù)層將來自PCIE總線中的核心層的數(shù)據(jù)封裝為TLP(Transaction Layer Packet)后發(fā)送至數(shù)據(jù)鏈路層;然而在接收數(shù)據(jù)時事務(wù)層的流程與發(fā)送數(shù)據(jù)時恰好相反,是將數(shù)據(jù)鏈路層中接收到的數(shù)據(jù)報文發(fā)至PCIE總線的核心層。數(shù)據(jù)鏈路層將來自事務(wù)層的數(shù)據(jù)報文添加Sequence Number前綴和CRC后綴進(jìn)行可靠性處理,保證數(shù)據(jù)在發(fā)送過程中能夠完整可靠地進(jìn)入到其他設(shè)備接收端的數(shù)據(jù)鏈路層。物理層是PCIE總線的層次結(jié)構(gòu)中的最底層,它將需要PCIE通信的設(shè)備連接在一起,同時也是PCIE體系結(jié)構(gòu)中最重要、最難以實(shí)現(xiàn)的組成部分,它為數(shù)據(jù)通信的PCIE設(shè)備間提供可靠的傳送介質(zhì),為數(shù)據(jù)報文的收發(fā)提供一個合法可靠的物理系統(tǒng)環(huán)境。

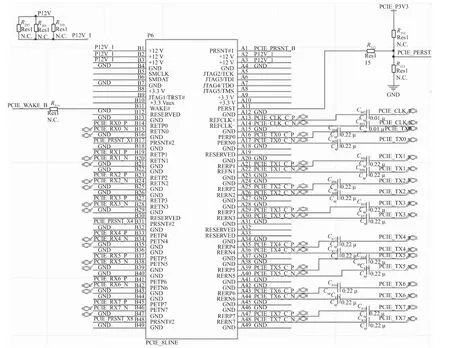

2.3.3 PCIE接口實(shí)現(xiàn)

PCIE的物理鏈路可以由單條或多條Lane組成,當(dāng)前PCIE可以支持1、2、4、8、16和32個Lane,而總線上的每一個Lane與外部設(shè)備間的數(shù)據(jù)交換速率和帶寬與PCIE總線版本相關(guān),以×1為例,PCIE 1.0的吞吐量為250 MB/s,而PCIE 4.0的吞吐量高達(dá)2 GB/s,在性能上提升了近8倍[8]。為滿足需求,本文采用的是×8寬度的PCIE 2.0鏈路結(jié)構(gòu),其電路設(shè)計結(jié)構(gòu)如圖7所示。

圖7 PCIE接口外圍電路設(shè)計

隨著頻率的提高,對于PCI并行接口傳輸出現(xiàn)問題:高速傳輸?shù)臅r候,并行的連線直接干擾異常嚴(yán)重,而且隨著頻率的提高,干擾越來越不可跨越。而在PCIE總線的每一個物理鏈路中的數(shù)據(jù)通路中有2條低壓差分信號線,一條用于發(fā)送,另外一條用于接收。相同內(nèi)容通過一正一反的差分信號傳輸,干擾可以很快被發(fā)現(xiàn)和糾正,從而可以將傳輸頻率大幅提升,同時PCIE接口是串行全雙工通信,那么從頻率提高所得到的收益大于一次傳輸多個bit的收益,而且在PCB設(shè)計時布線更簡單,也可使用更多Lane整合成為更高帶寬的線路。

3 測試與驗(yàn)證

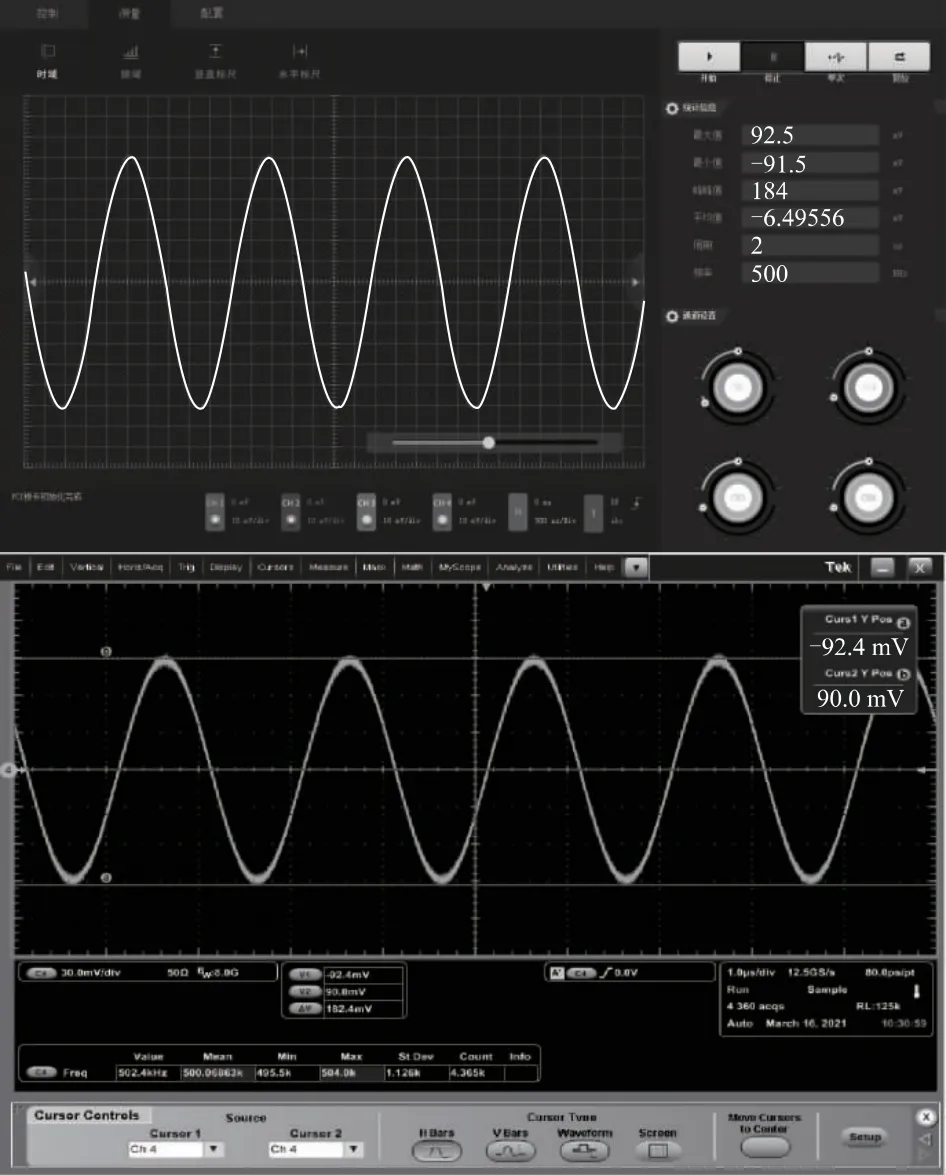

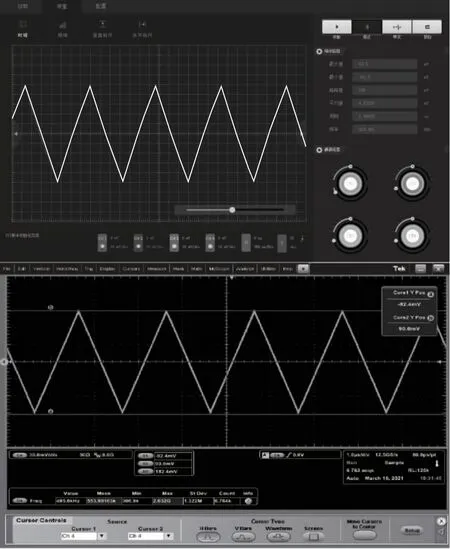

通過DG1022U函數(shù)發(fā)生器依次輸出一個峰峰值為183 mV的500 kHz正弦波信號、5 MHz方波信號和500 kHz三角波信號為該系統(tǒng)提供輸入采樣信號,其測試結(jié)果與原始信號對比如圖8、9、10所示,圖片上方為實(shí)際測量結(jié)果,下方為真實(shí)信號參數(shù)。

圖8 正弦波信號虛擬示波器測試對比結(jié)果

圖10 三角波信號虛擬示波器測試結(jié)果

從上述實(shí)際測量結(jié)果可知本次設(shè)計的虛擬示波器能夠基本實(shí)現(xiàn)傳統(tǒng)示波器的測試功能,且實(shí)際測量的信號頻率大小和幅值大小與真實(shí)值基本相同。為了觀測實(shí)際測量結(jié)果與輸入信號的誤差情況,給定幅值為400 mV、頻率大小為500 kHz~100 MHz的輸入信號進(jìn)行測試,實(shí)驗(yàn)結(jié)果見表1。

4 結(jié)束語

通過測試驗(yàn)證,本文基于國產(chǎn)ADC設(shè)計的虛擬示波器能夠?qū)崿F(xiàn)高速高精度采樣,并具有穩(wěn)定性好、抗干擾能力強(qiáng)等特點(diǎn)。該系統(tǒng)單路最高采樣4 GS/s,雙路使用最高采樣2 GS/s,同時具有PCIE接口可直接與PC端連接進(jìn)行數(shù)據(jù)傳輸,便于后續(xù)的信號處理、數(shù)據(jù)分析判斷和顯示以及數(shù)據(jù)存儲。