CPLD在DSP與液晶及鍵盤接口設計中的應用

姚國珍 尚秋峰

(華北電力大學(保定) 河北省保定市 071003)

數字信號處理器(Digital Signal Processing, DSP)是一種適合完成實時數字信號處理算法的微處理器,廣泛應用在通信、家用電器、軍事和醫療等領域。美國TI公司的TMS320C5509A為C5000系列中的一款低功耗16位定點DSP,在信號分析、數字通信、圖形圖像處理等方面應用較普遍[1]。在DSP構成的微處理器系統中,通常采用液晶和鍵盤作為人機交互工具,可實現參數或命令的輸入及處理結果的顯示輸出等功能。

在微處理器系統中,進行液晶和鍵盤擴展時,通常采用輸入輸出端口(General-Purpose Input/Output,GPIO)實現。由于C5000系列DSP主要針對便攜消費電子產品而設計,所以單獨的GPIO較少。很多可以用作GPIO的引腳是和片上外設功能復用的,當其作為片上外設功能引腳時,就不能作為GPIO來使用[2]。所以,進行液晶和鍵盤擴展時,不能采用GPIO的方法進行擴展,否則會用影響片上外設的使用。

針對上述問題,本文采用復雜可編程邏輯器件(Complex Programmable Logic Device,CPLD)設計了點陣式液晶和矩陣鍵盤與TMS320C5509A的接口方法。利用本文的設計方法,通過DSP的外部總線即可實現DSP對液晶和鍵盤的控制,不占用GPIO資源,從而可以提高整個DSP系統設計的冗余度。

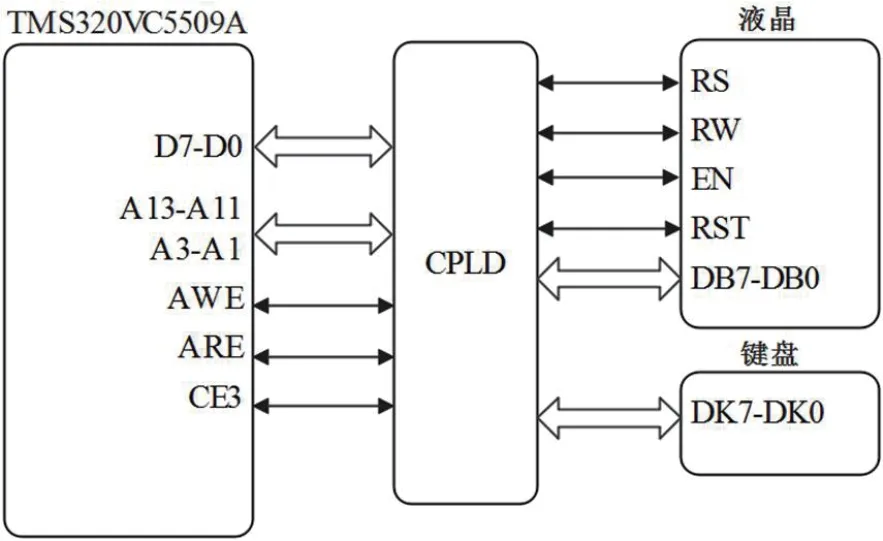

1 接口框圖

DSP與液晶和鍵盤的接口框圖如圖1所示。DSP通過外部數據總線、地址總線及控制信號與CPLD相連,其中D7-D0為低8位數據總線,AWE為異步寫使能信號,ARE為異步讀使能信號,CE2為空間片選信號;為了減少電路布線壓力,地址總線只用了其中一部分,包括A13-A11及A3-A0。液晶采用了128x64點陣式顯示器,其接口有RS(指令/數據選擇信號)、RW(讀寫選擇信號),EN(使能信號),DB7-DB7(數據線)。鍵盤采用了4x4矩陣鍵盤,其中DK3-DK0對應矩陣鍵盤的“行”,DK7-DK4對應矩陣鍵盤的“列”。

圖1:接口原理框圖

2 CPLD程序設計

2.1 液晶部分

對液晶進行驅動時,需要產生兩組信號,一組是控制信號RS、RW、EN和RST,另一組是用于傳輸命令或顯示數據的總線信號DB7-DB0。上述兩組信號都由DSP的數據線產生,圖2給出了兩組信號的CPLD圖形化編程方法。四個控制信號RST、RS、RW和EN通過鎖存器74273鎖存數據線的低四位D3-D0產生,74273的鎖存信號CLK由地址總線A13-A11和A3-A1、寫信號AWE以及空間片選信號CE3譯碼產生,如圖2(a)所示。地址信號A1和A12經過非門,并與其余地址信號、AWE和CE3進行“或非”運算后得到CLK信號,所以當A1和A12為邏輯“1”,其余信號為邏輯“0”時,則CLK為邏輯“1”,產生一個上升沿變化,可將數據總線D3-D0的狀態鎖存到74273的輸出端。當CE3為邏輯“0”時,訪問的是DSP的字地址為0x600000開始的空間,所以A1和A12位為邏輯“1”、其余位為邏輯“0”時,對應的地址為0x600801,即當DSP向地址0x600801進行寫數據時,即可將D3-D0的狀態鎖存到74273的輸出端,從而產生液晶的控制信號。限于CPLD引腳數量的限制,未將DSP的全部地址信號引入CPLD,只引入了A13-A11及A3-A1。所以,產生液晶控制信號的地址并不是唯一的,即只要滿足A1和A12位為邏輯“1”、A13、A11、A3、A2位為邏輯“0”時都滿足要求,0x600801只是多個地址中的一個,所以如果DSP系統中還擴展了其它外設及存儲器,應注意避免地址沖突情況的發生。

液晶的數據信號由DSP的數據線D7-D0產生。由于DSP的數據線還要驅動鍵盤、存儲器等其它器件,在不驅動液晶時,需要液晶與DSP的數據線進行隔離,所以,產生液晶數據信號時,除了要用74273進行鎖存外,還采用了74244完成總線隔離,如圖2(b)所示。74244的選通信號由一片74273通過鎖存DSP數據線的D0位產生,74273的鎖存信號的產生方式與圖2(a)中74273的鎖存信號產生方式相同,對應的地址為0x600800。74244的輸入端為74273鎖存的DSP的數據線D7-D0,此74273的鎖存信號對應的地址為0x600802。

圖2:液晶驅動信號產生

綜上,對液晶進行控制需要訪問3個地址,相當于在CPLD中定義了3個寄存器,寄存器地址分別是0x600800、0x600801和0x600802,根據寄存器的功能,分別稱三個寄存器為數據選通寄存器、控制寄存器和數據寄存器,分別用GR、CR和DR表示。

2.2 鍵盤部分

鍵盤模塊采用了4x4的矩陣鍵盤,通過行列掃描方式工作[3],如圖3所示。鍵盤共包括8個引腳DK7-DK0,其中DK3-DK0對應矩陣鍵盤的“行”,DK7-DK4對應矩陣鍵盤的“列”。鍵盤工作時,首先依次向行引腳寫入掃描數據1110、1101、1011和0111,然后讀取列引腳的狀態,通過行列數據即可確定是哪個按鍵按下。圖4給出了CPLD的圖形化編程方法,由圖3可知,寫行數據時,通過74273將DSP數據線的D7-D4鎖存到矩陣鍵盤的DK7-DK4引腳上,對應的地址為0x600803;讀列數據時,通過74244將DK3-DK0的狀態讀取到DSP的數據線D3-D0上,對應的地址為0x600804。

圖3:鍵盤引腳圖

圖4:鍵盤驅動信號產生

3 驅動程序設計

3.1 液晶部分

用C語言進行編程時,需要根據液晶的各個引腳的時序要求,使CPLD的輸出引腳產生相應的信號。圖5給出了對液晶進行寫操作時的時序圖,由圖5可知,進行寫操作時,首先要使RS和R/W信號有效,當向液晶寫要顯示的內容時,RS為高電平,當向液晶寫控制命令時,RS為低電平;由于是對液晶進行寫操作,所以R/W為低電平。然后,使能信號E變為高電平,數據總線上出現寫入液晶的數據,持續一段時間后,使能信號E再變為低電平,完成一次寫操作。

圖5:液晶寫操作時序圖

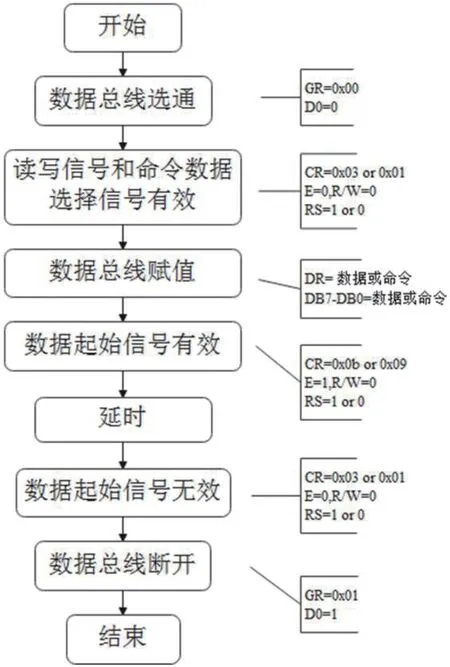

根據液晶寫操作的時序圖,圖6給出了在DSP上編程時的流程圖。首先向GR寫入0x00,此時DSP的地址總線上出現0x600800,數據總線上出現0x00,D0位為“0”,按照圖2(b)所示邏輯,74244將被選通。然后向CR寫入0x03(或0x01),使E=0、R/W=0、RS=1(或0),向DR寫入顯示數據或命令。再通過依次向CR寫入0x0b(或0x09)和0x03(或0x01)使信號E產生一段高電平信號,將顯示數據或命令寫入到液晶中,為了使高電平信號持續時間滿足時序要求,需要在此處加入一段時間的延時。最后向GR寫入0x01,使D0位變為“1”,將數據總線斷開,完成一次液晶的寫操作。

圖6:液晶寫操作流程圖

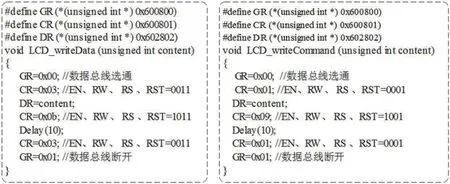

向液晶進行寫操作的C語言程序如圖7所示,其中void LCD_writeData (unsigned int content)和void LCD_writeCommand (unsigned int content)分別是向液晶寫數據和寫命令的函數,函數的參數unsigned int content為寫入的字節,函數的前面,采用宏定義的方式了定義了三個寄存器名稱。

圖7

3.2 鍵盤部分

對鍵盤進行編程時,首先寫入行數據,然后讀取列數據,并根據行列數據判斷是否有鍵按下。如果有鍵按下,則等待一段時間,再次判斷是否有鍵按下,以防止出現抖動導致的誤判。當判斷確實有鍵按下后,則可根據寫入的行數據和讀取的列數據判斷是哪個按鍵按下,掃描鍵盤的流程圖如圖8所示。

圖8:鍵盤掃描程序流程圖

下面給出了用C語言編程實現的鍵盤掃描程序,掃描過程由一個for循環完成,每循環一次完成鍵盤一行的掃描。當判斷出按下的鍵后,利用printf函數輸出該鍵對應的符號,實際應用時,可將printf函數替換為按鍵對應的子函數或功能代碼。如圖9所示。

圖9

4 總結

本文針對C5000系列DSP的GPIO較少的問題,采用CPLD設計了TMS320VC5509A與液晶和鍵盤的接口電路,詳細給出了CPLD圖形化編程實現方法和DSP的C語言編程的實現方法。該方法采用TMS320C5509A的數據總線和地址總線訪問液晶和鍵盤,避免了占用過多的GPIO的問題。本文的設計方法不僅可應用在DSP系統中,在其它具有外部總線的微處理器構成的系統中同樣適用。