基于DDS的BPM短波授時信號設計

賴文彬,李實鋒

( 1.中國科學院國家授時中心,西安 710600;2.中國科學院大學,北京 100049 )

0 引言

BPM 短波授時系統是國家重大科技基礎設施之一,它通過與世界標準時間(UTC)建立溯源關系,保持與協調UTC的同步,實現標準頻率信號和標準時間信息的精確發播[1-3].BPM 短波授時信號通過電離層的一次或多次反射來傳遞,能夠覆蓋我國陸地和近海海域,具有覆蓋范圍廣、接收方法簡單、終端成本低和戰時頑存性強等不可替代的優點[4].隨著民用領域和軍事領域BPM 短波授時應用日益增加,在應用終端的研發調試、性能評估和時延標定過程中,對性能可靠、功能完善、操作簡單的BPM 短波授時信號模擬源的需求越來越迫切.但目前相關文獻設計的短波授時信號模擬源存在結構設計不夠合理、功能不完善、時號發播精度較低等問題,因此研制性能良好、功能完善、能夠滿足現在應用的新一代BPM(中國科學院國家授時中心短波授時臺)短波授時信號模擬源,對我國BPM 授時系統的發展及高性能應用終端的研發有著非常重要的意義.

針對上述情況,本文以新一代BPM 短波授時信號模擬源的設計需求出發,選用Stratix Ⅱ系列的現場可編程門陣列(FPGA)芯片EP2S60F1020C4ES以及模數轉換(DAC)芯片DAC904E為核心,結合直接頻率合成的技術.通過結構設計、參數設計及計算、程序仿真及驗證完成了對BPM 短波授時信號的研究設計.仿真測試和實驗驗證表明:該設計完成了預期目標,為后續新一代BPM 短波授時信號模擬器的設計研究奠定了重要的基礎.

1 基于DDS的BPM 短波授時信號設計原理

基于直接數字式頻率合成器(DDS)的BPM短波授時信號設計的核心是基帶信號以及載波信號的設計,利用DDS技術即可產生一定頻率的基帶信號以及載波信號,通過對其格式進行相應的時序設計就可以得到所需信號.

1.1 BPM 短波授時信號概述

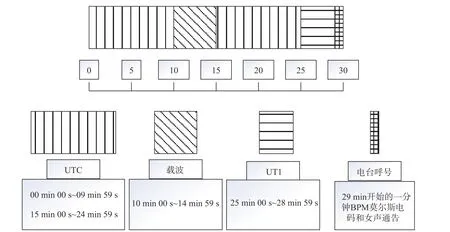

20世紀初,自無線電授時發明以來,短波授時是第一個使用短波無線電信號發播標準時間和標準頻率的授時方法.由于其覆蓋面廣、發送簡單、使用方便,受到廣大時間頻率用戶的歡迎,而且利用短波時號及進行時頻傳遞與校準是一種廉價而方便的方法,對于要求同步偏差在1 ms量級的用戶十分有利[5-7].BPM 短波授時信號發播標準時間、標準頻率信號是采用2.5 MHz、5 MHz、10 MHz、15 MHz 這四種載頻對1 kHz 正弦波信號進行調制來實現的[8], 現行的BPM短波授時信號發播體制如圖1所示.程序以半小時為一個周期,在每個周期的00 min 00 s~09 min 59 s及15 min 00 s~24 min 59 s發播 UTC,25 min 00 s~28 min 59 s 發播世界時信號 (UT1),10 min 00 s~14 min 59 s發播純載波信號,29 min 00 s開始發播莫爾斯電碼和女聲通告.

圖1 BPM 短波授時信號發播體制

UTC和UT1發播時長只發整秒和整分信號,各個時長信號的發播開始于整分而終止于該時段最后一個59 s.BPM 短波授時信號格式如圖2所示,UTC秒信號、UT1秒信號、UTC分信號及UT1分信號為不同周期的等幅1 kHz正弦波信號,UTC秒信號采用10個周波,即10 ms,UT1秒信號采用100個周波,即100 ms,UTC和UT1分信號均采用300個周波,即300 ms[9-10].

圖2 BPM 短波授時信號格式

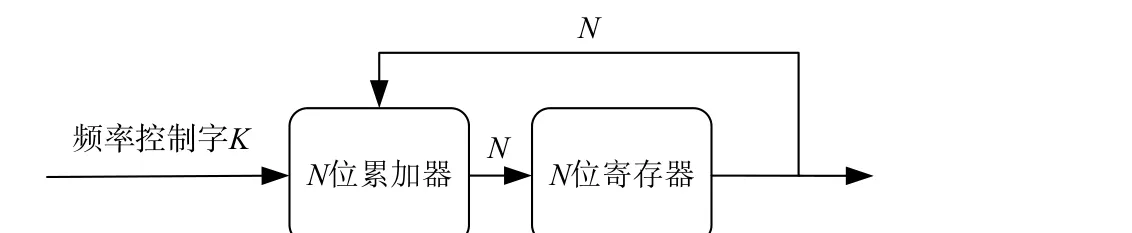

DDS中最關鍵的相位累加器是由N位累加器以及N位寄存器級聯而構成的,如圖4所示.其工作原理如下:每當到達參考時鐘fclk上升沿時,累加器就把頻率控制字K與N位寄存器輸出的數據相加,并將累加器的結果輸出到寄存器的數據輸入端[14].這樣周而復始,頻率控制字K不斷地進行線性相位累加,最終累加溢出頻率就是DDS輸出信號的頻率.

1.2 DDS技術原理

DDS是直接數字式頻率合成器的簡稱,是頻率合成技術的一次巨大突破[11],隨著集成電路系統以及半導體微電子技術的迅猛發展,DDS因其具有分辨率較高、相位噪聲較低以及輸出信號切換速率快等突出優點而日益顯露出它的優越性[12].

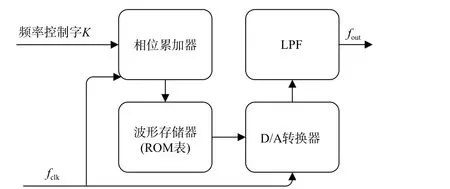

DDS技術的原理可以概述為:在設定系統時鐘的作用下,相位累加器線性累加計算所得的頻率控制字,再用得到的相位碼對ROM 表進行尋址,尋址后即可找到相對應的幅度碼,幅度碼經D/A 轉換器可得到相應的階梯波,最后使用LPF對階梯波進行平滑處理[13],就可以得到我們所需頻率的平滑連續波形,其結構框圖如圖3所示.

圖3 DDS 的結構框圖

圖4 DDS 相位累加器

2 系統的總體設計

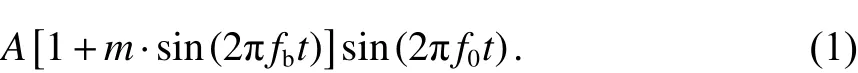

BPM 短波授時信號采用2.5 MHz、5 MHz、10 MHz、15 MHz 這四種頻點作為載波信號,對1 kHz 正弦波基帶信號進行載波調制,調制信號如下式所示:

式中:A為信號的幅度;m為信號的調制度;fb為正弦波基帶信號的頻率,其值為1 kHz;f0為載波信號的頻率,其值為上述的四個頻點.依據上述調制信號的公式,對系統進行了設計,系統結構如圖5所示.

圖5 系統總體設計框圖

可以看到系統主要由四個模塊組成:DDS 模塊、基帶信號產生模塊、載波產生模塊、AM 調制模塊.所設計系統的工作流程如下:首先板載晶振輸入頻率為100 MHz 的參考時鐘,通過鎖相環(PLL)擴頻為120 MHz 作為系統的工作時鐘;由FPGA 控制驅動DDS,計算出所需頻率的控制字,使DDS輸出系統設計所要求的特定頻率的正弦波信號;經過處理后的波形進入基帶信號產生模塊以及載波信號產生模塊,生成1 kHz的正弦波基帶信號以及四個頻點的載波信號,最后兩路信號經AM 調制模塊形成BPM 短波授時信號.

2.1 硬件平臺介紹

系統選用Stratix Ⅱ系列的FPGA 芯片EP2S60F10 20C4ES為核心硬件平臺,該芯片功耗較低且性能穩定,擁有豐富的邏輯資源,非常適合系統的設計研究.而且該硬件平臺具備豐富的I/O控制端口和串口通信端口,可以與各類設備進行互傳數據;具備實驗所需的板載100 MHz 晶振;同時集成了兩個最高速率達165 MHz 的14位D/A 轉換芯片DAC904E,D/A 輸出性能優良,具有優良的動態特性.

2.2 DDS信號源設計

對于板載晶振輸入的頻率為100 MHz 的參考信號,結合考慮BPM 短波授時信號輸出頻率的大小,選取PLL 的倍頻頻率為120 MHz 作為系統的工作時鐘,同時為降低DDS產生的幅度量化和截斷誤差對輸出信號的影響,綜合考慮系統的總體設計的可行性,選取相位累加寄存器的位寬N為32位,因此基帶信號的頻率控制字K1的大小可以設定為

3 實驗分析

實驗測試分析的主要目的是驗證所設計的BPM短波授時信號是否能夠有效且準確地輸出,由于四個頻點設計及工作方式大同小異,故實驗中選取5 MHz作為代表來驗證設計是否滿足要求.通過仿真分析,DDS所產生的載波信號以及觀測分析示波器輸出的載波信號和邏輯分析儀調制模塊所輸出的信號對所設計的BPM短波授時信號的性能進行評估.

3.1 DDS仿真分析

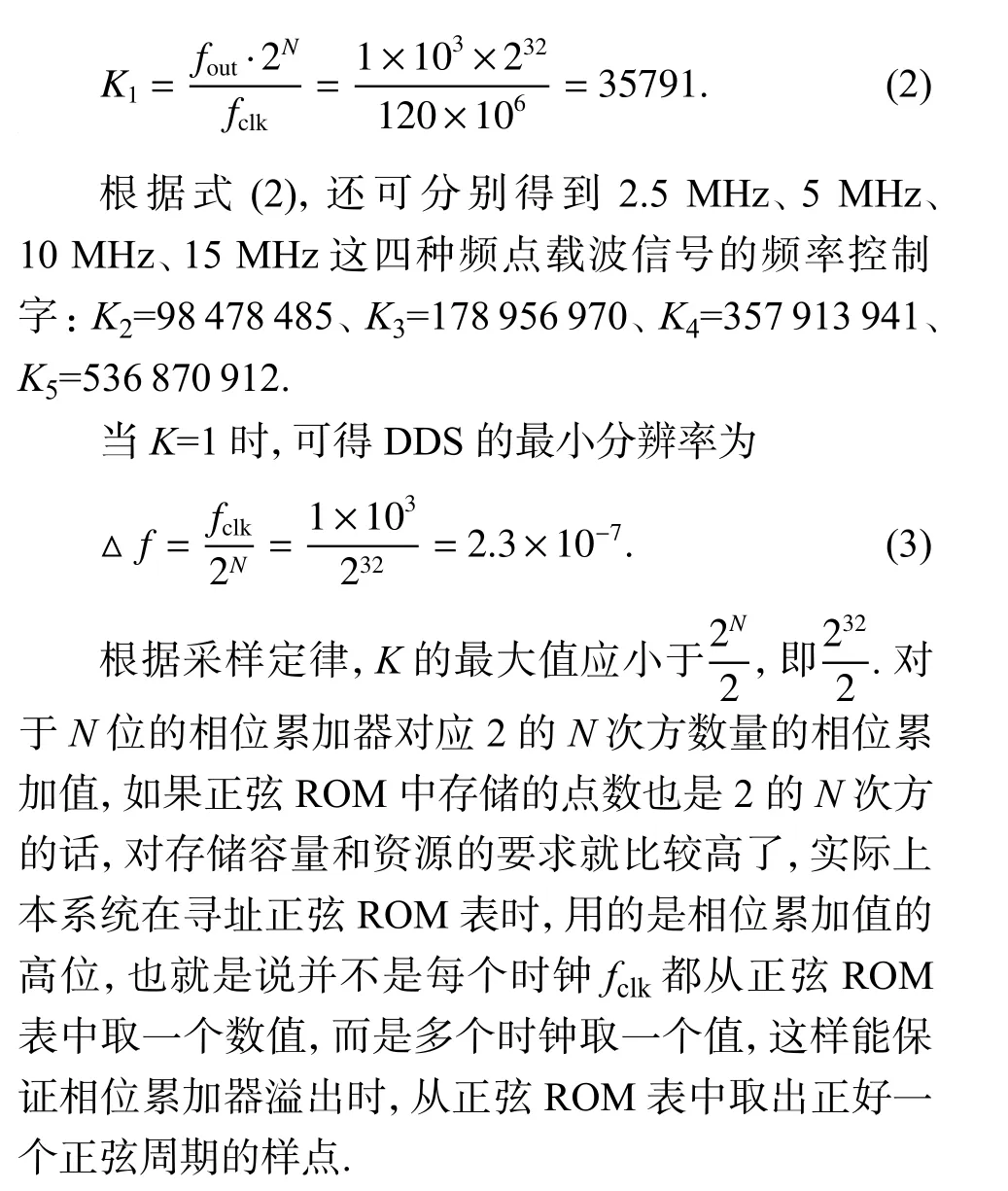

由于各類條件限制,DDS在產生相應頻率的波形時必然會產生許多誤差,如幅度量化以及相位截斷所產生的誤差[15-16]. 使用MATLAB創建DDS模型(以5 MHz 為例)進行數據仿真分析處理,圖6是生成的5 MHz 標準正弦波,并使用120 MHz 的時鐘進行采樣,采樣點數為48 個,此時包含48/(120 MHz/5 MHz)=2 個周期的采樣點.由圖6可知,正弦信號采樣的結果接近理想程度,并且從DFT圖中可以看出噪聲被壓制在?280 dB以下(現實世界中電子熱運動噪聲才?180 dB),因此DDS產生的特定頻率波形可以相當好地滿足工程需求.

圖6 5 MHz 時頻域采樣圖

圖7是對DDS產生的5 MHz 正弦波時存在相位截斷誤差以及幅度量化誤差的頻譜分析圖,此處選取相位累加器的位數N=32,采樣頻率設置為120 MHz,仿真參數設置為K=178956970,相位位數在仿真中截取8位,幅度量化位寬設置為10位.分別考慮有相位截斷誤差無幅度量化誤差情況如圖7(a)所示;無相位截斷誤差有幅度量化誤差情況,如圖7(b)所示,以及有相位截斷誤差和幅度量化誤差情況,如圖7(c)所示.比較三組圖可以看出:在固定累加器位數、截取位數以及幅度量化位寬的情況下,由相位截斷及幅度量化引起的誤差對DDS產生的正弦波的波形頻譜的雜散位置和譜線數目影響不大,除5 MHz 處有一根有用的正弦譜線外,其余雜散分量都較低.因此在FPGA 中產生BPM短波授時信號的載波信號時累加器位數、頻率控制字以及相位截取位數的選取可參照仿真中所采用的設置來滿足實際設計需求.

圖7 相位截斷誤差以及幅度量化誤差的頻譜分析圖

3.2 DDS產生的波形

BPM 短波授時信號發播標準時間、標準頻率信號是采用2.5 MHz、5 MHz、10 MHz、15 MHz 這四種載頻對1 kHz正弦波信號進行調制來實現的.由于產生的波形原理都是類似的,所以這里選取DDS產生的5 MHz 的波形為代表來對短波授時信號進行初步的評估.

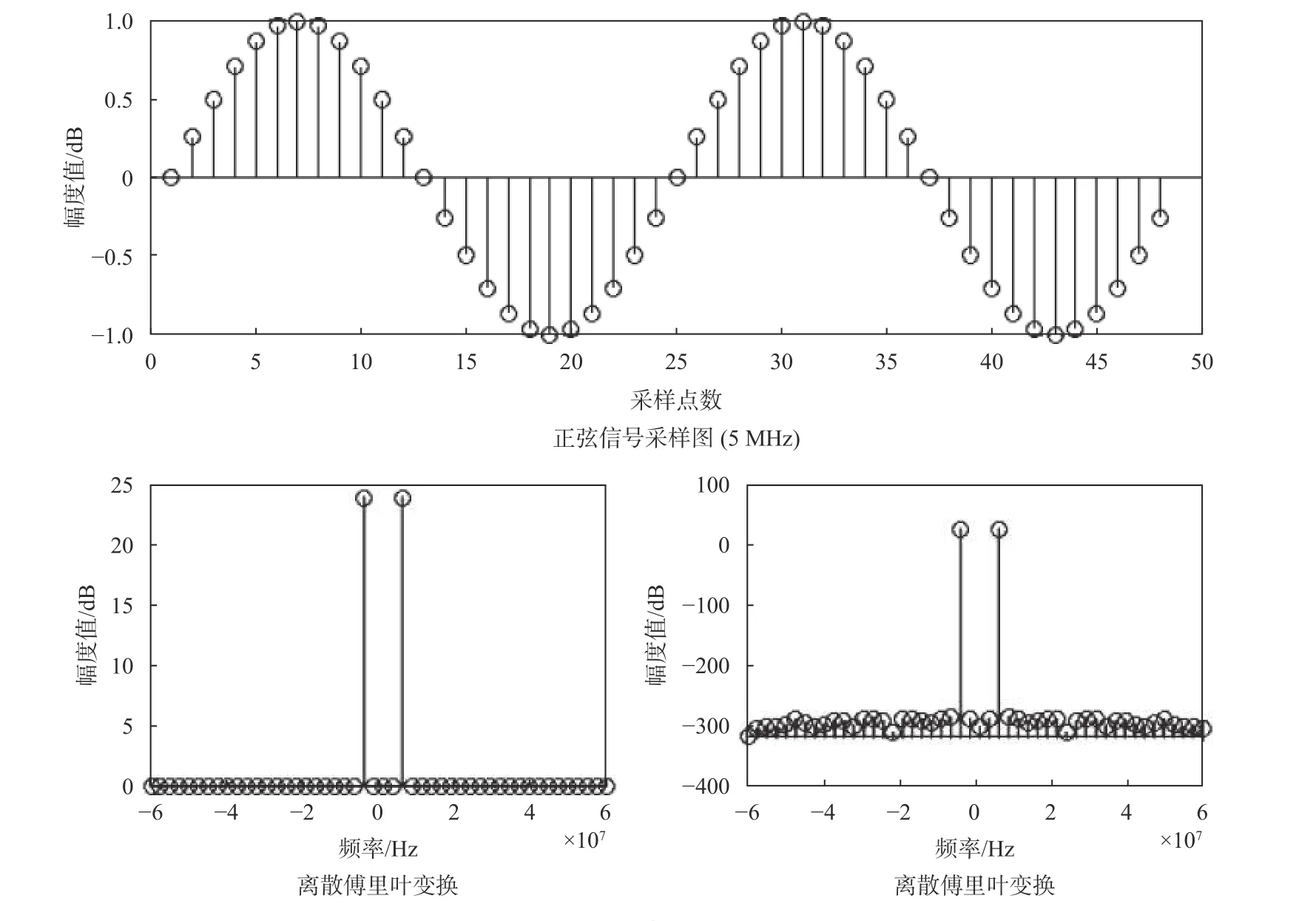

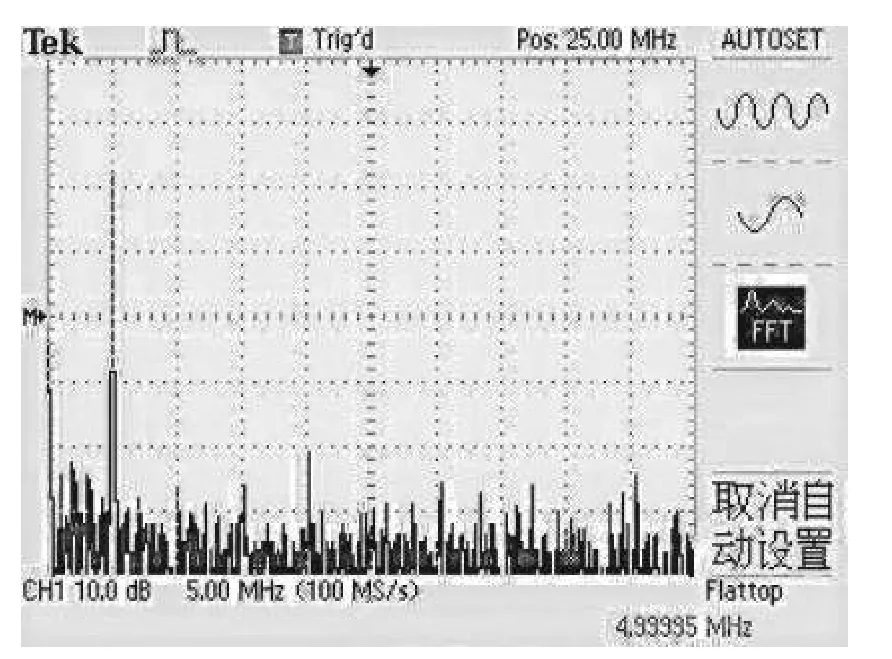

圖8和圖9是從Tektronix 示波器上直接截取下來的部分波形,可以看到DDS輸出波形的頻率為4.99996 MHz,比預期的5 MHz 的頻率誤差小0.01%,而且輸出信號中混疊無用的雜散分量較少,波形曲線平滑,效果良好.

圖8 DDS產生信號的時域圖

圖9 DDS產生信號的頻域圖

3.3 AM 調制信號

以5 MHz 為例,采用quartus自帶的邏輯分析儀對信號進行仿真測試.在建立signaltap文件后設置120 MHz 為采樣時鐘,選擇時鐘上升沿對信號進行觸發,并將編譯后的輸出文件下載到芯片上,實時觀測輸出的1kHz 基帶信號(sine)、5 MHz 載波信號(carrier_5M)以及輸出的AM 調制信號(signal),如圖10和圖11所示.其中圖10是圖11的局部細節圖,圖11為輸出波形半個周期的截圖.對比圖10和圖11可以看出,基帶信號及載波信號輸出波形的局部細節圖波形采樣點數合適使得輸出曲線平滑無毛刺,且調制后波形的輸出特性能夠達到的BPM 短波授時信號設計的指標,即準確且有效地輸出了BPM 短波授時信號.

圖10 signaltap II 觀測波形截圖a

圖11 signaltap II 觀測波形截圖b

4 結束語

文中從理論和實驗分析兩方面對基于DDS的BPM 短波授時信號設計的工作原理進行了詳細的闡述,并給出了系統的總體設計方案,包括設計中所使用的硬件平臺的介紹以及DDS信號源設計的細節.而且通過仿真分析DDS所產生的特定頻率的正弦波信號的誤差以及AM 調制模塊所輸出的特定頻率的信號性能指標,驗證了所設計的BPM 短波授時信號能夠滿足信號的格式以及系統的總體設計要求,進而為新一代BPM 短波授時信號模擬器的設計研究和BPM 應用終端開發調試、測試標定提供了堅實的基礎.