一種基于FPGA的4K HDMI轉(zhuǎn)eDP視頻接口的設(shè)計(jì)

謝緒煜,龍 彬,周 軍,胡 彬

(長沙湘計(jì)海盾科技有限公司,湖南 長沙 410100)

0 引 言

現(xiàn)場可編程邏輯門陣列(Field Programmable Gate Array,F(xiàn)PGA)技術(shù)以其可靠性高、速度快及設(shè)計(jì)靈活的特點(diǎn)廣泛應(yīng)用于圖像處理領(lǐng)域。目前在民用領(lǐng)域,液晶顯示器或者4K電視機(jī)廠商常用驅(qū)動(dòng)4K eDP接口液晶面板的方案,主要是基于晨星MSTAR或者Realtek、國內(nèi)海思及瑞芯微等圖像處理芯片設(shè)計(jì)的,而該方案靈活性較低,如需要增加新的視頻圖像接口或者改變某一項(xiàng)圖像處理功能較為困難。例如,在主顯示屏幕eDP顯示畫面基礎(chǔ)上再增加一個(gè)副屏幕eDP環(huán)出顯示或者VGA環(huán)出顯示不一樣的分辨率圖像就不能用上述方案來實(shí)現(xiàn),局限性較大,且該方案視頻接口切換畫面顯示較慢,多達(dá)10 s鐘的時(shí)間才能完成畫面切換,無法做到無縫切換[1-4]。針對上述情況,介紹一種基于FPGA將4K HDMI視頻信號轉(zhuǎn)為eDP接口信號的方法。

1 系統(tǒng)總體設(shè)計(jì)

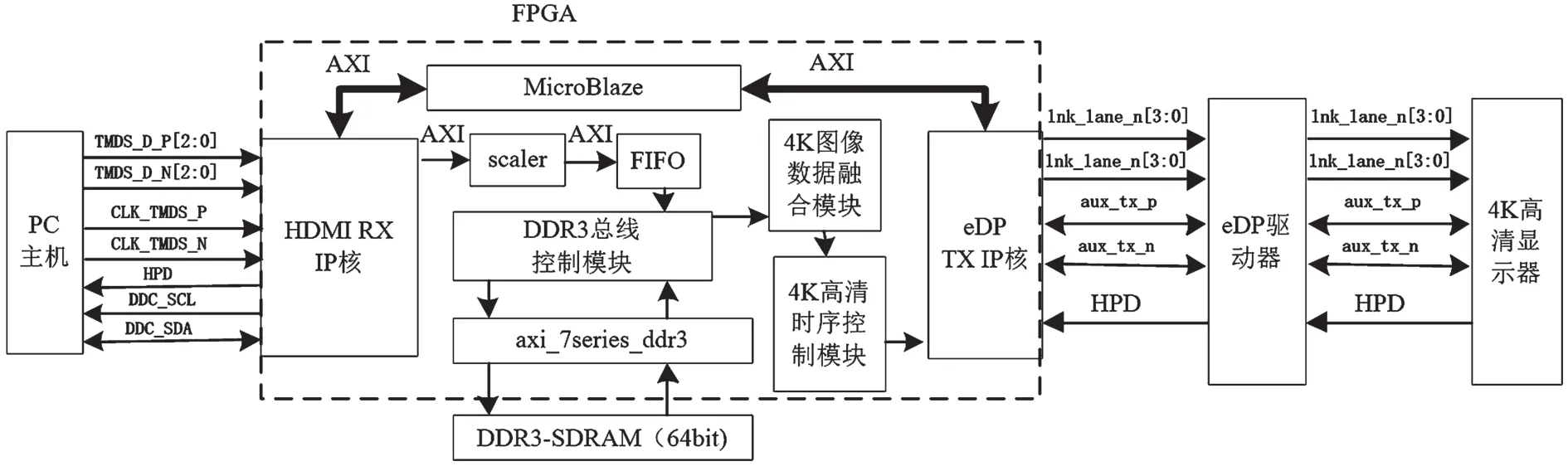

根據(jù)設(shè)計(jì)要求,本系統(tǒng)利用高速FPGA將HDMI視頻信號通過圖像處理后轉(zhuǎn)為eDP的接口信號。系統(tǒng)中的FPGA內(nèi)部采用模塊化設(shè)計(jì)思路,例化的模塊包括HDMI RX模塊、MicroBlaze軟核模塊、scaler縮放模塊、FIFO模塊、DDR3總線控制模塊、DDR3的IP核模塊、4K圖像數(shù)據(jù)融合模塊、4K高清時(shí)序控制模塊以及eDP TX模塊。其中,HDMI RX模塊從PC主機(jī)接收視頻圖像,對4K HDMI信號進(jìn)行解碼,并將HDMI視頻圖像轉(zhuǎn)換為通用的圖像數(shù)據(jù)處理RGB格式;scaler縮放模塊采用雙線性插值算法將分辨率低于3 840*2 160的RGB格式的視頻圖像分辨率放大至4K,縮放后的圖像數(shù)據(jù)用高速FIFO模塊保存;FIFO模塊的保存數(shù)據(jù)達(dá)到預(yù)設(shè)像素點(diǎn)數(shù)量時(shí),按行將當(dāng)前保存的像素點(diǎn)寫入DDR3 SDRAM;4K圖像數(shù)據(jù)融合模塊采用乒乓操作方式從DDR3 SDRAM中讀取圖像數(shù)據(jù)進(jìn)行預(yù)處理,包括對比度調(diào)節(jié)、亮度調(diào)節(jié)及圖像降噪處理;處理完成后由4K高清時(shí)序控制模塊轉(zhuǎn)換為eDP信號,最終由eDP TX硬件接口發(fā)送至4K高清顯示器顯示。本設(shè)計(jì)可使4K高清液晶顯示器的顯示速度加快,系統(tǒng)總體框圖如圖1所示。

圖1 實(shí)現(xiàn)4K HDMI視頻轉(zhuǎn)eDP視頻接口原理框圖

本設(shè)計(jì)中采用的高速FPGA為美國Xilinx公司的生產(chǎn)的kinetx-7系列XC7K325T-2FFG900I,該系列FPGA采用28 nm工藝生產(chǎn),內(nèi)部含有豐富的邏輯資源,包括高速GTX接口、DDR3高速接口等,可以滿足4K的高速圖像處理要求。eDP驅(qū)動(dòng)器采用SN65DP159RZ芯片來增強(qiáng)其傳輸數(shù)據(jù)的能力,以適應(yīng)高速數(shù)據(jù)長線傳輸要求,避免數(shù)據(jù)時(shí)鐘抖動(dòng)現(xiàn)象[5-6]。

2 系統(tǒng)硬件設(shè)計(jì)

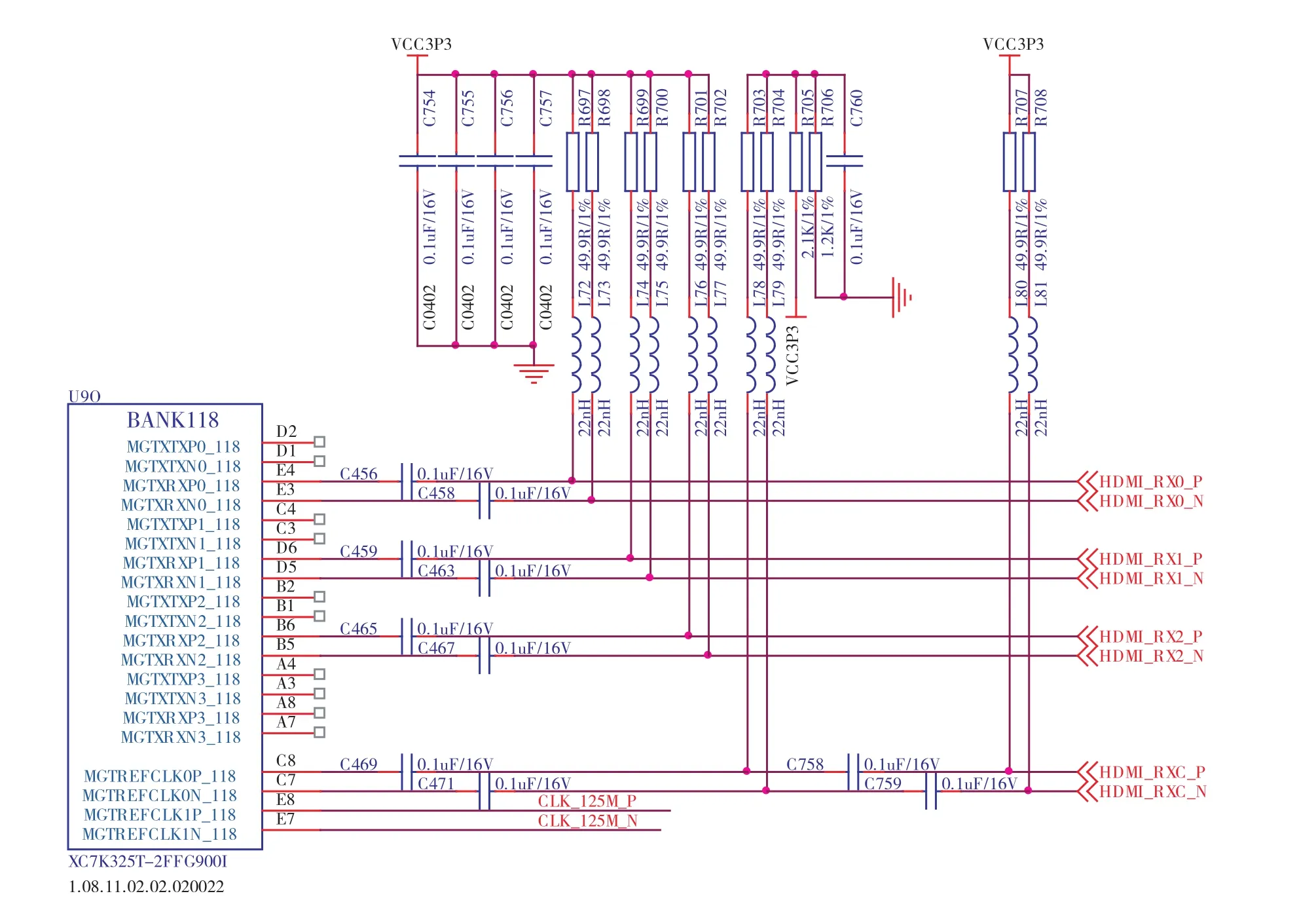

HDMI RX硬件接口與PC主機(jī)通過HDMI線纜連接,HDMI RX硬件接口由FPGA內(nèi)部的MicroBlaze軟核模塊控制,從PC主機(jī)接收HDMI視頻圖像數(shù)據(jù)并做處理。在本設(shè)計(jì)中,PC電腦主機(jī)應(yīng)能輸出分辨率為3 840*2 160的4K HDMI視頻圖像,若PC主機(jī)不能輸出4K圖像分辨率,也可以通過縮放模塊將其放大為4K圖像信號。為了改善信號的傳輸質(zhì)量,在HDMI RX模塊的HDMI RX硬件接口的前端增加了視頻圖像信號調(diào)理電路,具體的信號調(diào)理電路如圖2所示,PC主機(jī)與HDMI RX硬件接口之間上拉串聯(lián)的50 Ω電阻和20 nH電感,然后在上拉點(diǎn)與HDMI RX硬件接口之間設(shè)置0.1 uF電容。通過該信號調(diào)理電路對PC主機(jī)傳輸?shù)腍DMI視頻圖像數(shù)據(jù)進(jìn)行抗干擾處理,從而使HDMI RX模塊接收到的HDMI視頻圖像數(shù)據(jù)質(zhì)量更高,避免出現(xiàn)閃屏和信號出現(xiàn)噪點(diǎn)的現(xiàn)象。HDMI接口的EDID信息保存在硬件電路的EEPROM芯片中,EEPROM 芯片選用24LC02B。當(dāng)PC主機(jī)檢測到HDMI熱插拔HPD信號后,通過IIC管腳的SCL和SDA管腳讀取EDID信息,以確定其輸出的圖像分辨率大小。

圖2 HDMI信號調(diào)理與FPGA GTX連接硬件電路圖

3 系統(tǒng)程序設(shè)計(jì)

3.1 HDMI圖像數(shù)據(jù)流處理設(shè)計(jì)

HDMI RX模塊從PC主機(jī)接收到的HDMI信號包括像素時(shí)鐘hdmi_clk、像素點(diǎn)有效指示信號hdmi_de、行同步信號hdmi_hsync、場同步信號hdmi_vsync以及像素點(diǎn)24 bit的hdmi_rgb[23:0]數(shù)據(jù);對于分辨率為3 840*2 160的視頻圖像無需進(jìn)行縮放處理,對于分辨率小于3 840*2 160的圖像進(jìn)行scaler模塊放大成3 840*2 160的分辨率;縮放后的數(shù)據(jù)存入FIFO模塊,由于DDR3程序存入圖像按行存儲(chǔ),因此當(dāng)FIFO模塊的數(shù)據(jù)計(jì)數(shù)值fifo_data_count計(jì)到大小為3 840個(gè)像素點(diǎn)的時(shí)候,表明一行圖像數(shù)據(jù)已經(jīng)緩存完畢。邏輯模塊調(diào)用FPGA內(nèi)部的DDR3 IP核模塊,將一行大小為3 840的像素點(diǎn)數(shù)據(jù)寫入DDR3 SDRAM存儲(chǔ)芯片中。4K圖像數(shù)據(jù)融合模塊讀取DDR3 SDRAM中的圖像數(shù)據(jù)并經(jīng)過圖像增強(qiáng)、去噪等處理之后發(fā)送至4K高清時(shí)序控制模塊,4K高清時(shí)序控制模塊將數(shù)據(jù)寫入eDP TX IP核,最終調(diào)用eDP TX模塊內(nèi)部的高速接口將圖像數(shù)據(jù)發(fā)送到高清顯示器,F(xiàn)PGA內(nèi)部的數(shù)據(jù)處理流程如圖3所示。

圖3 FPGA內(nèi)部圖像數(shù)據(jù)處理流程圖

DDR3模塊讀寫視頻圖像數(shù)據(jù)采用AXI總線控制方式。AXI總線控制方式具有讀寫速度快、操作規(guī)范的特點(diǎn)。該設(shè)計(jì)中,DDR3 IP核設(shè)置的工作主頻為667 MHz而沒有設(shè)置成800 MHz,目的是為了降低功耗及增加可靠性。AXI_Data_Width的位寬設(shè)置為512 bit,經(jīng)過計(jì)算得出一共需要4片16 bit數(shù)據(jù)位的DDR3 SDRAM組合才能滿足數(shù)據(jù)流帶寬要求,AXI總線為512 bit的數(shù)據(jù)位寬需要16個(gè)hdmi_rgb[23:0]像素點(diǎn)來拼接,拼接的原則為:先到達(dá)的像素點(diǎn)存于低位,晚到的像素點(diǎn)存于高位。1行3 840個(gè)像素點(diǎn)的數(shù)據(jù)可以拼接成240個(gè)512 bit的AXI總線數(shù)據(jù),數(shù)據(jù)拼接原理如圖4所示。

圖4 數(shù)據(jù)拼接原理圖

3.2 雙線性插值算法模塊設(shè)計(jì)

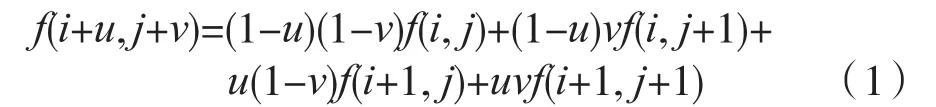

雙線性插值算法廣泛應(yīng)用于顯示器圖像處理領(lǐng)域,可以將圖像的分辨率放大來適應(yīng)顯示屏的顯示要求,核心思想是在相鄰的上下左右4個(gè)像素點(diǎn)插入1個(gè)像素點(diǎn),其計(jì)算方法為:

式中:f(i+u,j+v)可由原圖像中4個(gè)像素坐標(biāo)為(i,j)、(i+1,j)、(i,j+1)、(i+1,j+1)所 對應(yīng)的像素值決定;u、v為浮點(diǎn)坐標(biāo)的小數(shù)部分,通過計(jì)算得到,取值范圍為[0,1)區(qū)間的浮點(diǎn)數(shù)。

scaler縮放模塊采用雙線性插值算法實(shí)現(xiàn),其功能是將任意分辨率的輸入圖像轉(zhuǎn)變?yōu)?K圖像,實(shí)現(xiàn)圖像插值放大。

雙線性插值模塊用vivado HLS軟件進(jìn)行開發(fā)設(shè)計(jì)。vivado HLS工具可以將C語言高級綜合為硬件,極大地節(jié)約了設(shè)計(jì)人員的開發(fā)時(shí)間。HLS軟件部分代碼如下所示,生成的verilog硬件代碼如圖5所示。

圖5 HLS生成的verilog硬件代碼圖

for(col=1;col<=destW;col++){

srcCol=((float)col)*colRatio;

k=(unsigned int)(srcCol);

u=srcCol-k;

coffiecent0=(1.0-t)*(1.0-u);

coffiecent1=(1.0-t)*u;

coffiecent2=(t)*(1.0-u);

coffiecent3=t*u;

src_pixlel_coor1=getClip(k,srcW,1);

src_pixlel_coor3=getClip((k+1),srcW,1);

}

3.3 eDP發(fā)送4K高清圖像數(shù)據(jù)程序設(shè)計(jì)

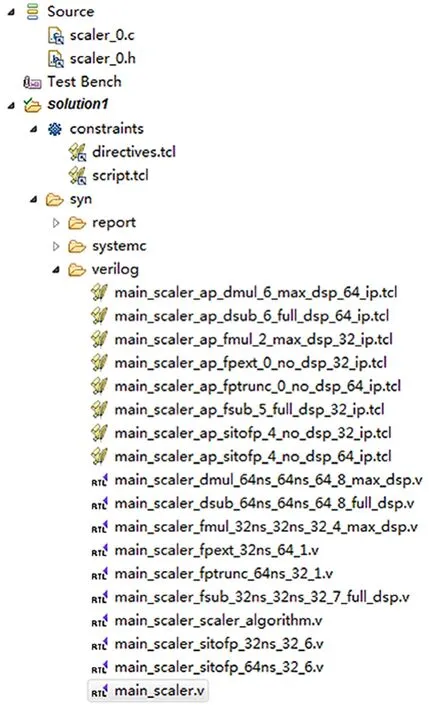

eDP是一種低電壓擺幅的差分信號技術(shù),它使得信號能在長距離的差分PCB線對或平衡線纜上以幾百兆赫茲的速率傳輸,視頻數(shù)據(jù)通過eDP接口標(biāo)準(zhǔn)傳輸時(shí)有特定的數(shù)據(jù)格式。本設(shè)計(jì)中,eDP協(xié)議包含在eDP IP核中,因此要實(shí)現(xiàn)eDP接口發(fā)送4K高清視頻數(shù)據(jù)功能,需使用官方推薦的eDP IP核,該IP核中有一些參數(shù)如鏈路速度、帶寬及數(shù)據(jù)位寬等需要C語言軟件配置才能更好管理及使用。由于需要配置eDP IP核的參數(shù)較多,為了降低配置管理的難度,本文調(diào)用了FPGA自帶的MicroBlaze軟核對eDP IP硬核參數(shù)進(jìn)行配置。MicroBlaze軟核具有嵌入式軟件管理功能,MicroBlaze核與eDP TX IP硬核的例化模塊如圖6所示。lnk_clk_p和lnk_clk_n分別為eDP IP核差分輸入時(shí)鐘的正負(fù)端口,此處設(shè)置輸入的時(shí)鐘頻率為135 MHz;lnk_tx_lane_p[3:0]和lnk_tx_lane_n[3:0]分別為eDP IP核傳輸?shù)牟罘謹(jǐn)?shù)據(jù)的正負(fù)端口,若要傳輸4K的分辨率要同時(shí)調(diào)用4對lnk_tx_lane;tx_hpd為PC主機(jī)檢測的熱插拔信號;aux_tx_io_p和aux_tx_io_n分別為eDP輔助信號通道,用來與顯示器的TCON板之間的信號握手和EDID信息讀取。

圖6 例化的eDP模塊圖

4K高清時(shí)序控制模塊根據(jù)自身產(chǎn)生的有關(guān)eDP模塊的控制時(shí)序,將數(shù)據(jù)預(yù)處理得到的4K視頻圖像數(shù)據(jù)轉(zhuǎn)換為eDP信號,進(jìn)而將eDP信號寫入eDP TX模塊。MicroBlaze軟核模塊控制eDP TX模塊,使eDP TX模塊通過eDP TX硬件接口將視頻圖像數(shù)據(jù)至4K高清顯示器。MicroBlaze軟核模塊控制eDP TX硬核模塊的軟件控制流程如圖7所示。首先初始化MicroBlaze軟核模塊與eDP TX模塊之間的AXI總線,接收來自4K高清顯示器的EDID信息,通過接收鏈路信息選擇對應(yīng)的lane通道和link rate速度;eDP TX模塊使用確定的lane通道并以確定的link rate速度,通過eDP TX硬件接口將視頻圖像數(shù)據(jù)至4K高清顯示器。

圖7 eDP軟件處理流程圖

在vivado開發(fā)軟件生成的工程導(dǎo)出硬件eDP_wrapper.hdf文件后,利用SDK軟件開發(fā)工具導(dǎo)入硬件eDP_wrapper.hdf文件配置信息;根據(jù)硬件信息生成軟件工程,該軟件工程包含BSP底層驅(qū)動(dòng),通過編寫MicroBlaze軟核C語言軟件程序來控制eDP參數(shù)的配置與發(fā)送數(shù)據(jù)的過程管理,可以實(shí)現(xiàn)4K高清圖像數(shù)據(jù)的發(fā)送[7]。

4 試驗(yàn)驗(yàn)證

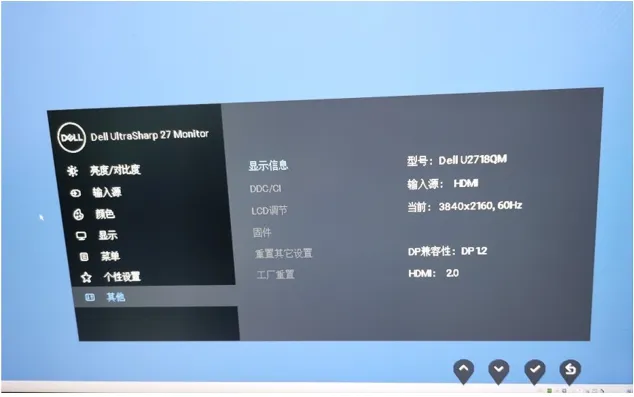

對基于FPGA的4K HDMI轉(zhuǎn)eDP視頻接口進(jìn)行設(shè)計(jì)驗(yàn)證時(shí),需要將PC主機(jī)視頻顯卡發(fā)送的分辨率為3 840*2 160的視頻圖像通過HDMI接口線纜連接到4K HDMI轉(zhuǎn)eDP視頻接口系統(tǒng)電路板,再從HDMI轉(zhuǎn)eDP視頻接口系統(tǒng)電路板用eDP線連接到4K高清顯示器進(jìn)行顯示。測試結(jié)果如圖8所示,在高清顯示器上顯示1路PC主機(jī)桌面圖像,桌面上顯示輸入的分辨率信息為3 840*2 160,可見設(shè)計(jì)滿足1路圖像接收機(jī)顯示要求[8]。

圖8 分辨率為3 840*2 160的HDMI圖像畫面

5 結(jié) 語

試驗(yàn)結(jié)果表明,基于FPGA的4K HDMI轉(zhuǎn)eDP視頻接口系統(tǒng)能滿足4K高清顯示技術(shù)要求,具有顯示速度快、可以無縫切換的特點(diǎn),可以廣泛應(yīng)用于自主可控設(shè)計(jì)領(lǐng)域如軍工或者航天等。本文研究對于高速4K高清顯示器或者4K電視機(jī)的設(shè)計(jì)具有一定的參考意義。