一種射頻單元中FPGA的遠程升級方法

彭磊磊 辛利

針對TD-LTE無線通信系統中遠端射頻單元的維護升級問題,提出一種FPGA固件遠程升級方法。該方法采用CPRI接口的以太網信道傳輸固件數據、控制命令和狀態信息,利用FPGA內部邏輯完成Flash的識別、擦除和寫入,并在Flash分區存儲的基礎上,通過控制FPGA加載起始地址實現遠程升級和失敗回退。經驗證,該方法具有易操作、可移植性強和可靠性高的特點。

當前,TD-LTE無線通信系統憑借通信效率、抗干擾性以及QoS業務保證等方面的技術優勢,成為城市軌道交通系統中CBTC、PIS和CCTV綜合業務承載的主要無線通信技術體制,得到了越來越廣泛的應用。TD-LTE無線通信系統采用分布式架構設計,將基帶處理單元集中部署在機房,而射頻單元通過光纖拉遠后沿軌道線路部署,形成全線的無線信號覆蓋。雖然此種部署方式減少了射頻信號在傳輸過程中的衰減,提升了信號覆蓋的質量,卻給壁掛于隧道內或架高于塔架上的射頻單元在維護升級方面帶來一定困難,間接影響了軌道交通的運營效率和安全。因此,有必要設計一種針對射頻單元中FPGA固件的遠程升級方法,降低維護難度,提高維護效率。

射頻單元遠程升級示意圖

射頻單元遠程升級示意圖如圖1所示。系統維護升級時,控制中心將新版本(1.2版)的FPGA固件通過網線和光纖介質傳輸到射頻單元。射頻單元將新版本固件更新到閃存,替換舊版本(1.1版)。升級成功后斷電重啟,射頻單元的FPGA將以新版本啟動。如果升級失敗,FPGA將以備份版本啟動。

硬件設計

硬件設計如圖2所示,主要包括三部分:微控制單元(MCU)、Xilinx 公司7系歹]FPGA以及SPI Flash。

射頻單元的FPGA通過CPRI協議接收上層傳來的以太網數據(包含控制命令、固件數據),并以媒體無關接口發送到MCU。MCU接收以太網數據并處理,再以本地總線(localbus)發送到FPGA。FPGA通過內部邏輯完成SPI Flash的識別、擦除和寫入,并將狀態信息通過以太網信道反饋給上層。

SPI Flash采用Spansion公司的s25fl256,該芯片是串行NOR Flash。FPGA 采用Xilinx 公司的XC7K325T-2FFG900I,該芯片屬于Kntex7系列,具有高性價比、低功耗的特點。FPGA需要配置成主SPI加載模式,配置電路如圖3所示。

Flash分區設計

本文的FPGA遠程升級方法具備升級失敗后自恢復的能力,設計思路是Flash存儲分區。如表1所示,SPI Flash的存儲區域分成三部分:FPGA加載地址控制區、備份區以及升級區。FPGA加載地址控制區存放一組用于IPROG命令的比特流,備份區存放備份固件,升級區存放升級固件。

Spansion公司的s25fl256存儲空間是32MByte,其扇區類型有2種規格,一種是統一64KyteB大小,另一種是統一256KByte大小,本文選取后者。FPGA芯片XC7K325T- 2FFG900I生成的固件大小約為11.9MByte,備份固件和升級固件可同時存放在s25fl256中。

首先分配IPROG命令比特流,如表2所示。

這組比特流中,“AA995566”是同步頭。FPGA只有在收到同步頭后才開始接收配置數據,而同步頭之前的數據后被FPGA忽略。本方案把“AA995566”放到Flash第一個扇區的最后四個字節上。同步頭后的比特流按次序從Flash的第二個扇區開始位置存放并執行16個字節對齊,不足的比特流用空操作指令填充。其中熱啟動起始地址(WBSA)是升級固件的起始地址,本方案確定該地址為0X00B40000。

IPROG命令比特流之后開始放置備份固件。備份固件結束之后升級固件開始之前的空間放置比特1。升級區從指定地址0X00B40000開始,并按512byte對齊,不足的比特填充‘1。升級區最后的32bit是CRC32校驗碼,計算升級區域所有比特的CRC32值,但不包括最后的32bit。

FPGA固件修改

初始化Flash

實現在線升級功能,需要初始化Flash,即用JTAG線把修改后的固件燒錄進Flash。該初始化工作只需要執行一次。修改后的固件包含IPROG命令比特流、備份固件比特流和升級固件比特流,它們的起始地址按Flash分區方案確定。

固件修改可由Matlab或C語言實現,流程如下:

1.以寫模式打開一個init.bin文件,寫入0x3FFFC個“FF”,并在后面的四個字節寫入0x“AA995566”。

2.繼續寫入IPROG比特流,以16個字節對齊,不足的字節填充0x“20000000”。

3.讀取備份固件并寫入imt.bin,其后填充比特‘1直到0X00B40000前一個地址。

4.讀取升級固件按512byte對齊,不足的比特填充‘1直到最后4個字節。計算加填充的升級固件的CRC32值并放到最后4個字節。

5.寫入加CRC32校驗的升級固件到init.bin。

升級固件添加CRC32

FPGA從RS232接口接收修改后的升級固件,并寫入到Flash實現在線升級,該過程不再需要JTAG線。

改寫升級固件只需要添加CRC32,流程如下:

1.以寫模式打開一個update.bin文件。

2.讀取升級固件按512byte對齊,不足的比特填充‘1直到最后4個字節。計算加填充的升級固件的CRC32值并放到最后4個字節。

3.寫入加CRC32校驗的升級固件到update.bin。

FPGA邏輯設計

媒體無關接口

本文設計中,媒體無關接口(MII)是CPRI接口的一部分。CPRI采用Xilinx公司的IP核實現,可實現同相/正交數據、廠商特定信息、以太網數據和高速數據鏈路控制的傳輸。MII接口在CPRI接口中的位置如圖4所示。

FPGA的MII接口與MCU的MII接口對接,實現以太網收發。

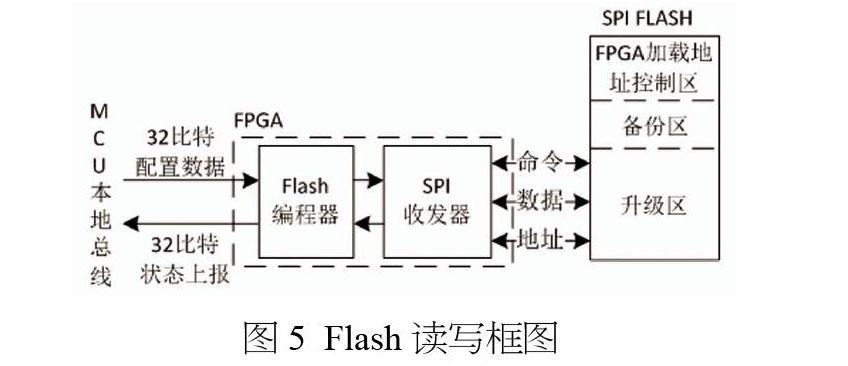

SPI Flash讀寫

SPI Flash讀寫模塊包含一個Flash編程器和一個基于SPI 協議的收發器,如圖5所示。Flash編程器的功能是識別、擦除和燒寫Flash,并通過MCU本地總線向層發送升級成功或失敗的指示信號。基于SPI協議的收發器功能是向SPI Flash發送命令或數據,并從SPI Flash中接收數據。

Flash編程器實現在線升級的流程如下:

1.初始化。完成升級過程中指示信號的復位。

2.檢驗Flash ID并上報上位機是否正常。

3.擦除第一個扇區最后4個字節的同步頭0x“AA995566”。

4.擦除升級區。

5.燒寫升級區。

6.校驗升級區,看CRC32余式是不是0x“C704DD7B”。

7.更新升級狀態,指示升級成功或失敗。如果升級成功,第一扇區最后4個字節燒寫同步頭0x“AA995566”。失敗情況下,會給出錯誤類型,如超時或CRC校驗有誤,并不燒寫同步頭。

Flash編程器實現升級失敗返回備份配置的關鍵是對同步頭的控制。如果升級成功,FPGA掉電重啟,檢測到同步頭后,執行后續的IPROG命令并跳轉到升級區的起始地址開始加載;如果升級失敗,FPGA無法檢測到同步頭,就會忽略預置的IPROG命令,從備份配置啟動。

測試驗證

采用多個不同的固件,在無線通信板卡上對本文方法做驗證,這些固件控制板卡上的指示燈以不同的方式閃爍。選取其中2個固件并制作imt.bm初始化Flash。選取其他的固件制作update.bin做在線升級。多次執行在線升級并穿插進行人為斷電操作。升級成功后,板卡上的指標燈按新固件中的邏輯閃爍。人為斷電致使升級失敗,板卡上的指標燈閃爍方式不變。上百次實驗中,沒有出現一次差錯,證明本文方法具有較高的可靠性。

本文方法操作簡單的特點體現在init.bin和update.bin制作上。兩個文件的制作只需要簡單的Matlab或C語言腳本即可實現。

本文方法的FPGA邏輯使用HDL語言編寫,移植時,只需修改與Flash和固件加載地址相關的部分,具有較強的可移植性。本方法的FPGA邏輯已成功移植到以Micron公司MT25Q25做為配置存儲芯片的xc7a200tfbg676-2上。

本文提出的射頻單元中FPGA固件遠程升級方法,操作簡單、可移植性強和可靠性高,已成功應用到多個TD-LTE無線通信系統產品上,為產品的升級維護帶來了便利。