基于超低電壓的片上分組交換路由器設計

丁一歡,何衛鋒

(上海交通大學微納電子學系,上海 200240)

0 引言

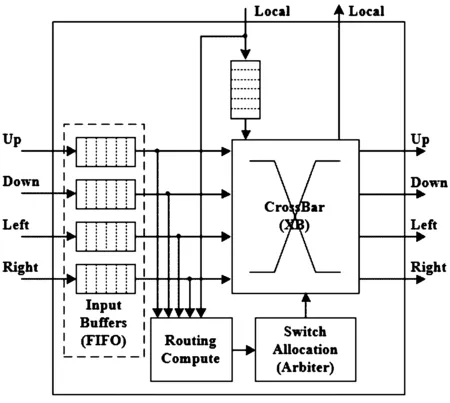

隨著多核、眾核技術的發展,越來越多的處理器核被集成到一起,因此也對片上多個處理器核的互連機制提出了更高的要求。NOC通過多個路由器組成特定的拓撲結構,實現了并行化處理數據通信,因此具有高帶寬、高利用率和良好的擴展性[1]。目前NOC中最常用的數據交換方式是分組交換方式,即數據從源節點以分組的形式在路由器間進行存儲、轉發,直至到達目的節點,面向這種分組交換方式的路由器即分組交換路由器。圖1展示了一個應用于2D Mesh網絡的分組交換路由器,可以同時處理來自四個方向和本地處理器核心的數據包,并通過路由計算、仲裁等操作,將數據發往各自目標方向的輸出端口。

圖1 2D Mesh結構NOC中的Router

在NOC中,路由器是構成整個網絡的核心部件,也占據了整個網絡大部分的功耗開銷。從硬件層面來說,為了降低電路的功耗,最常見的做法是將電路電壓降低到晶體管近閾值或亞閾值區域,以顯著減小動態翻轉功耗[2]。

低電壓電路的功耗比正常電壓電路小很多,但會對PVT波動(Process,Voltage,Temperature variations)更加敏感。當發生制造工藝偏差、電壓波動和外界溫度變化時,電路的延時會受到嚴重的影響,甚至會導致功能錯誤。因此相較于正常電壓電路,低電壓下的電路設計需要有更多的時間裕度,這限制了低電壓電路的最高工作頻率。

在此背景下,錯誤檢測與糾正(EDAC:Error Detection and Correction)技術[3-4]能夠有效減小PVT variations的影響,放松對電路設計裕度的要求。EDAC技術通過在部分電路節點插入EDAC單元,來對電路中出現的時序錯誤進行檢測和糾正,使得電路可以在較高的頻率下保持功能正確。由于EDAC技術可以提高低電壓電路的最高運行頻率,因此也可以得到能耗的收益。

因此本文設計了一種可以工作在超低電壓下的片上分組交換路由器,首先完成路由器的6級流水線結構后,將傳統的REG時序單元替換為LATCH單元,并在部分關鍵路徑終點插入了EDAC單元進行檢錯和糾錯,最后基于一個4×4的2D Mesh NOC系統驗證了此路由器的性能。

1 Router結構設計1.1 路由器基本結構

路由器的基本結構包括輸入緩沖區、路由計算、端口仲裁和交叉開關模塊,如圖2。設計中的數據包設定為32比特,其中有8比特代表了此數據的源地址和目的地址(見表1)。因此輸入緩沖區采用了位寬為32比特的異步FIFO。本文選擇的路由算法為二維XY路由,Switch Allocation模塊根據優先級輪詢的結果對前級的輸入端口申請進行仲裁,仲裁失敗或下級已滿時,會暫停部分流水線恢復數據。

表1 數據包格式

圖2 Router基本結構

考慮到仲裁失敗時數據恢復的需要,在計算路由前增加了一級流水線FO。由于FIFO讀取和寫入為2級,因此一共為6級流水線。Router的6級流水線結構如圖3。

圖3 Router流水線結構圖

在以上描述的路由器流水線結構基礎上,采用正沿觸發LATCH(即PLATCH)作為主要時序單元實現了6級流水線。相較于傳統的REG單元來說,由于LATCH對電平敏感,具有時間借用的特性,因此具有更強的容錯性,也非常適合結合EDAC技術進一步提高電路的性能。

完成RTL代碼后,將TSMC28nmHPC標準單元庫在0.4V下重新特征化提取,并用于Design Compiler綜合,然后在Prime Time中分析綜合后網表的關鍵路徑分布。根據路徑分布結果,Router中的關鍵路徑都集中于少數的Endpoints,因此可以運用EDAC技術進行優化,即在這些關鍵Endpoints處插入EDAC單元進行檢錯,從而提高電路的運行頻率。由于關鍵Endpoints數量適中,因此不會導致EDAC單元插入開銷過大。

1.2 路由器中的EDAC設計

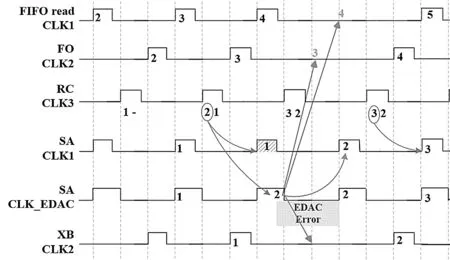

在本設計中采用的EDAC單元結構如圖4a),由一個CLK_edac控制的Shadow LATCH和一個異或門來實現檢錯。CLK_edac頻率和CLK相同,但高電平時間比CLK更長一些。EDAC單元的檢錯過程的波形示意圖見圖4 b)。在圖4 b)最后一個周期,正確數據D在CLK的下降沿到來后才翻轉,發生了時序錯誤,導致Error信號為高,此時的Q_edac的值才是正確值。EDAC單元的檢測窗口大小約為CLK_edac與CLK的高電平時間之差。

圖4 a)EDAC單元結構圖;b)EDAC單元糾錯過程波形示意圖

在Router電路中,根據Primer Time分析的路徑分布,最易發生時序錯誤的關鍵路徑集中在計算arbiterfail信號和仲裁結果arbiter信號的路徑上。因此在這兩類信號后插入EDAC單元進行檢錯,具體的方法是將圖4 a)中的EDAC CELL接到相應的數據端,通過相應的Error信號判斷是否發生時序錯誤。所插入EDAC單元的數量為20個。

插入EDAC單元進行檢錯后,糾錯機制可以有兩種:

(1)若后級路徑為短路徑,通過Error信號選擇 Q_edac 作為正確的輸出,送到后級運算即可。

(2)若后級路徑也為長路徑,則必須立即將前后級的流水線暫停,同時通過Error選擇Q_edac作為本級輸入,下一個周期就可以正確運算。

圖5 EDAC糾錯機制圖解

其中第1種方式可以進一步簡化為直接將Q_edac作為正確的輸出。如圖6所示,在本設計中,當檢測到SA級出現時序錯誤,會立即暫停FIFO、FO、XB級流水線,并將EDAC CELL中的正確值恢復到SA級相應的輸入端。

圖6 EDAC糾錯波形圖

插入EDAC單元后的Router流水線結構圖如圖7所示。

圖7 插入EDAC單元后的Router流水線結構圖

1.3 時鐘設計

由于所提出的Router設計采用了LATCH為時序單元,采用的時鐘會與傳統REG單元有所差別,此處簡單介紹本設計中采用的時鐘和時鐘產生模塊。基于PLATCH結構的流水線一般采用兩相時鐘控制,相鄰兩級的時鐘高電平不會重疊。但與此同時,如果采用PLATCH設計,兩相時鐘的周期需要變成REG電路時鐘周期的兩倍,才能確保功能正確。

針對這一點,本文創新性地采用了三相時鐘控制,時鐘周期理論上只需要變成REG電路的3/2倍,既保持了不需要進行短路徑填充的優點,也減小了對運行頻率的影響。需要注意的是,采用三相時鐘控制后,各級數據不再是同步更新。因此當STALL信號觸發時,也不需要立即暫停前級流水線。可以將相關控制信號傳到前級打拍再處理,這也進一步簡化了數據恢復的控制邏輯。

在本文提出的Router設計中,由CLK1控制FIFO級讀數據操作和SA級,由CLK2控制FO級和XB級,由CLK3控制RC級和FIFO級寫數據操作。設計中的三相時鐘和clk_edac的產生電路[5]如圖8。設計中采用的CLK_edac占空比為1/3。

圖8 a)時鐘產生模塊電路圖 b)時鐘產生模塊波形圖

2 版圖實現與仿真分析2.1 版圖實現

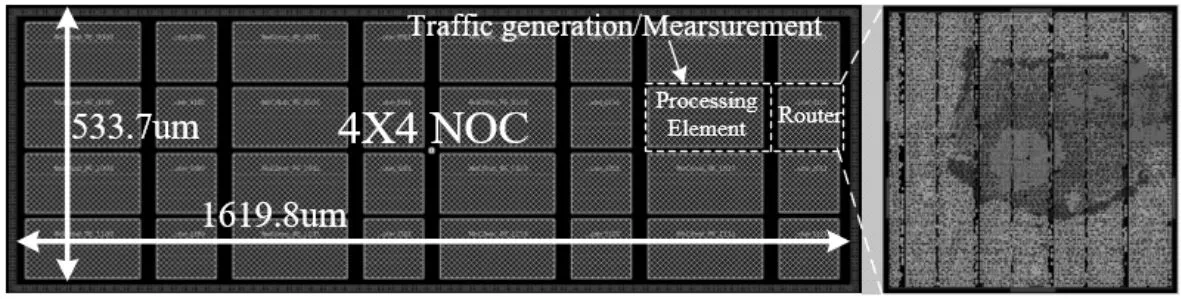

將前文描述的綜合網表基于IC Compiler布局布線,得到了最終的4×4 2D Mesh NOC版圖,如圖9所示。版圖面積為1619.8um×533.74um,包含16個路由節點。每個節點包括一個面積為114.1um×113.4um的Router和一個等高的數據處理單元。

圖9 4×4 2D Mesh NOC版圖

2.2 仿真設置

為了驗證所設計的路由器的性能,搭建了一個4×4的2D Mesh NOC作為testbench。此網絡中含有16個按照設定的數據包格式收發數據的處理單元,16個所設計的路由器,以及前文所描述的時鐘產生模塊。數據處理單元具有收發數據和計數的功能。數據處理單元發送數據可以有兩種模式:輪詢模式和用戶配置模式。我們采用的是輪詢模式,即按照0000~1111的順序依次向其他地址發送數據。另外為了比較EDAC設計的優勢,將不具備檢錯糾錯功能的Router作為Baseline電路,在同樣的testbench和輸入激勵下也進行仿真。

2.3 性能分析

仿真關注的性能指標包括NOC網絡的最高工作頻率、丟包率、吞吐率以及Router模塊的功耗開銷等。

本文設計的Router在測試中得到的正常運行最小時鐘周期為16.2ns,即整個NOC網絡最高工作頻率為61.73MHz。在時鐘周期小于16.2ns時,發生時序錯誤,導致出現丟包,對不同周期下同樣時間內的丟包數和接收數進行統計,得到曲線如圖。圖10的橫坐標為仿真設置的時鐘周期大小,縱坐標為丟包數與接收數,由圖可見,隨著時鐘周期減小,丟包越來越頻繁,接收到的數據包越來越少。由于每次丟包后會請求重傳一次數據,因此這會導致網絡的總運行時間迅速增加。

圖10 網絡丟包數與接收數隨周期變化曲線

由丟包數和接收數可以計算得到丟包率隨周期變化曲線,對不具有檢錯糾錯功能的Router也進行了同樣的仿真后,將兩者丟包率曲線進行對比。由圖11所示,可以看到采用EDAC設計的Router丟包率始終小于Baseline電路,且在16.2ns時丟包率已經降為0,而Baseline電路直到17.4ns時才不再丟包。因此采用EDAC設計可以提高Router對時序錯誤的容忍能力,并使Router的工作頻率提高了7.4%。

圖11 網絡丟包率隨周期變化曲線

此外隨時鐘周期減小,電路丟包率的增長趨勢也有所不同。在圖11的A區域,兩種Router的丟包率都隨周期減小而保持緩慢的增長,且丟包率數值接近,基本在10%以內。當時鐘周期繼續減小時,如B區域所示,Baseline電路的丟包率開始迅速增大,此時采用EDAC設計的Router丟包率曲線仍維持A區域的趨勢不變,曲線斜率明顯更小。注意到在時鐘周期為13.2ns時,Baseline電路的丟包率達45%,此時采用EDAC設計的丟包率僅為15%。當時鐘周期小于13.2ns時,即為圖11的C區域,Baseline電路丟包率的增長趨勢又趨于平緩,而采用EDAC設計的電路丟包率隨周期減小開始迅速增大。因此整體而言在圖11的B區域內,采用EDAC設計的優勢最明顯。

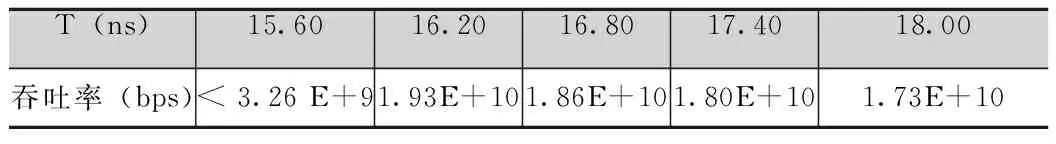

當以最小周期16.2ns運行時,整個NOC網絡吞吐率為1.93E+10 bps。由于不出錯時發送完所有數據需要的周期數固定,當運行周期大于16.2ns時,運行時間會變長,網絡吞吐率隨之下降;當運行周期小于16.2ns,由于出現大量丟包,需要大量的重傳數據導致時鐘周期數增大,吞吐率也會迅速下降。因此網絡最大吞吐率為1.93E+10bps,而Baseline電路的最大吞吐率在17.4ns處得到,為1.80E+10bps。

表2 網絡吞吐率與時鐘周期

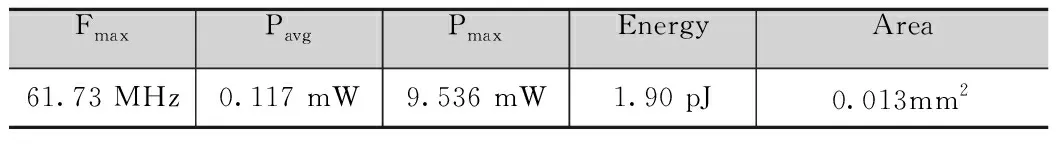

除了網絡運行頻率和吞吐率有所提升以外,由于采用了超低電壓設計,NOC中路由器的整體功耗也很小。對于單個路由器設計,以Router_0000的各指標為例。

表3 Router_0000性能指標

根據PrimeTime中的功耗報告得到Router_0000中各類型功耗分布圖和各個子模塊的功耗分布圖,分別為圖12 a)和圖12 b)。由圖12 a)可以看到時鐘網絡造成的功耗開銷占了50%左右,同時所有單元的靜態功耗也占了約50%。這一點也符合最小能量點(MEP)的特征。

圖12 a)Router_0000中各類型功耗分布圖;b)Router_0000子模塊功耗分布圖

由圖12 b)可以看到在子模塊中,輸入緩沖區的FIFO功耗開銷最大,RC模塊和SA模塊次之。顯然頻繁的數據讀寫會導致FIFO相對于其他模塊消耗更多的能量,此外由于RC模塊進行了優化設計,添加了備份數據的存儲,SA模塊增加了EDAC單元和更多的控制邏輯,因此也會有較多的功耗開銷。

Router_0000的峰值功耗為9.54mW,電路功耗隨時間的變化曲線呈現周期性的規律。

圖13 Router_0000瞬時功耗變化曲線

對NOC網絡中16個Router的功耗信息進行了統計,結果如圖14,圖中每個點代表一個Router的Pavg。

圖14 16個Router的平均功耗

由圖14可見,在4×4的NOC網絡中,功耗最低的是處于4個角處的Router(即Router 6、7、10、11),其次是邊緣上的Router(即Router 2、3、5、8、9、12、14、15),功耗最大的是網絡中心位置的Router(即Router 1、4、13、16)。這是由于處于中心位置的Router需要處理更多方向的數據,因此中心位置的Router也是最容易發生堵塞的。將這16個Router的Pavg結果取平均后,可以得到:所設計的Router采用TSMC 28nmHPC工藝實現,在0.4V,61.73 MHz下運行時,平均每周期能耗僅為2.07 pJ。

3 結語

本文結合低電壓EDAC(Error Detection and Correction)技術和三相時鐘流水線設計的優點,提出了一種面向低電壓的片上分組交換路由器,并在一個4×4的2D Mesh網絡中驗證了性能。基于TSMC28HPC工藝的后仿結果表明,在0.4V下該路由器最高工作頻率達到61.73MHz,比Baseline電路相比提高了7.4%,且每個路由器一個周期的平均能耗僅為2.07 pJ。