基于SWD協議的ISP技術研究與應用*

王 宇,劉浪華

(中國電子科技集團公司第三十研究所,四川 成都 610041)

0 引 言

目前嵌入式領域的主流產品在研發階段主要通過仿真器對微處理器進行程序的仿真驗證,生產階段通過專用聯合測試工作組(Joint Test Action Group,JTAG)燒錄器完成芯片固件燒錄,基本不涉及后期固件的升級維護。一旦固件程序在應用上存在漏洞,只能將設備返廠維修,導致產品后期維護費用居高不下。通過結合串行調試(Serial Wire Debug,SWD)串行調試技術和在線系統編程(In-System Programming,ISP)技術,能夠解決設備后期維護不便的問題。

SWD技術支持所有可通過JTAG接口進行調試的ARM Cortex A/R/M系列處理器和具有CoreSight調試架構的ARM芯片[1],包括德州儀器(Texas Instrument,TI)、 恩 智 浦(NXP Semiconductors)、Atmel、Samsung等廠家的芯片,以及意法半導體(STMicroelectronics,STM)公司STM32系列微處理器等。

1 SWD協議原理研究

SWD串行調試由一個雙向數據線和單向時鐘線組成實現數據的同步傳輸,可替代JTAG調試。時鐘頻率為50 MHz時數據傳輸速率可達4 MB/s,較少的印制電路板(Printed Circuit Board,PCB)布局布線資源便可實現低功耗低成本應用[2]。SWD協議實現芯片資源的交互流程如圖1所示。

1.1 SWD接口協議

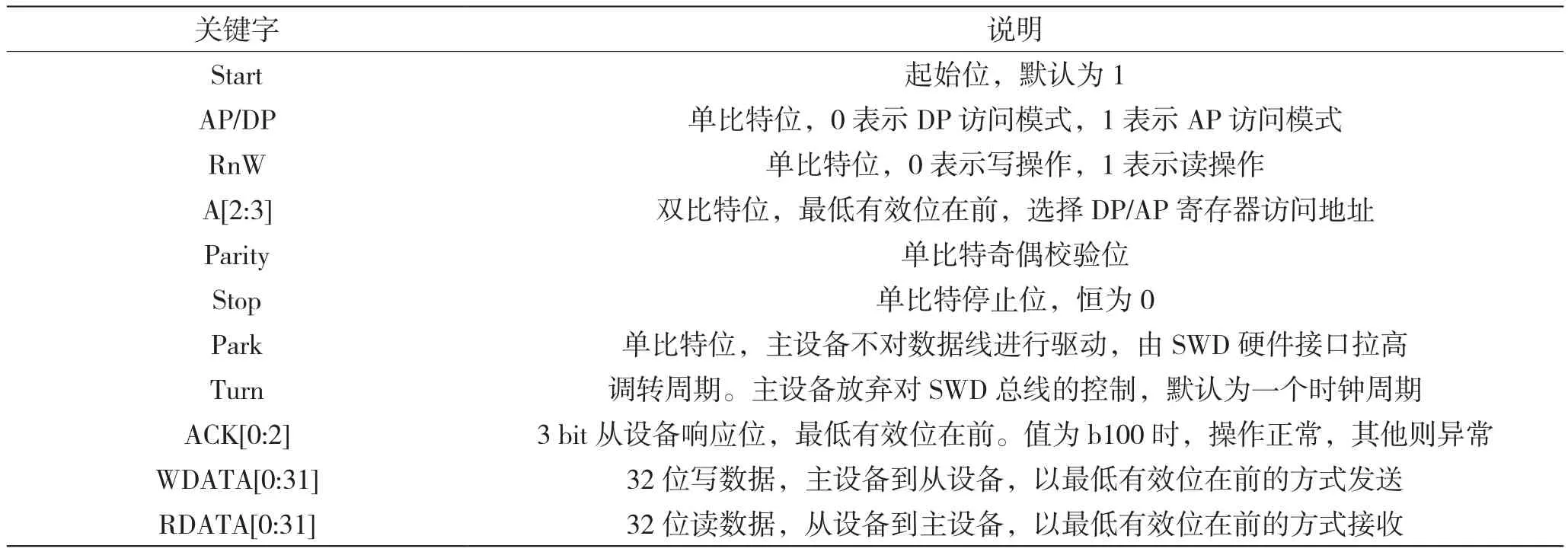

SWD操作流程主要分為3個階段:數據請求包REQ、應答數據包ACK與數據讀寫傳輸包[3]。表1列舉了SWD接口交互流程的主要關鍵字信息。

表1 SWD協議關鍵詞

SWD的寫操作由1 byte請求包、3 bit應答包與33 bit的寫數據組成,一次完整的寫操作如圖2所示。

SWD的讀操作由1 byte的請求包、3 bit的應答包與33 bit的讀數據組成,應答包與讀數據包間無Turn周期,一次完整的讀操作如圖3所示。

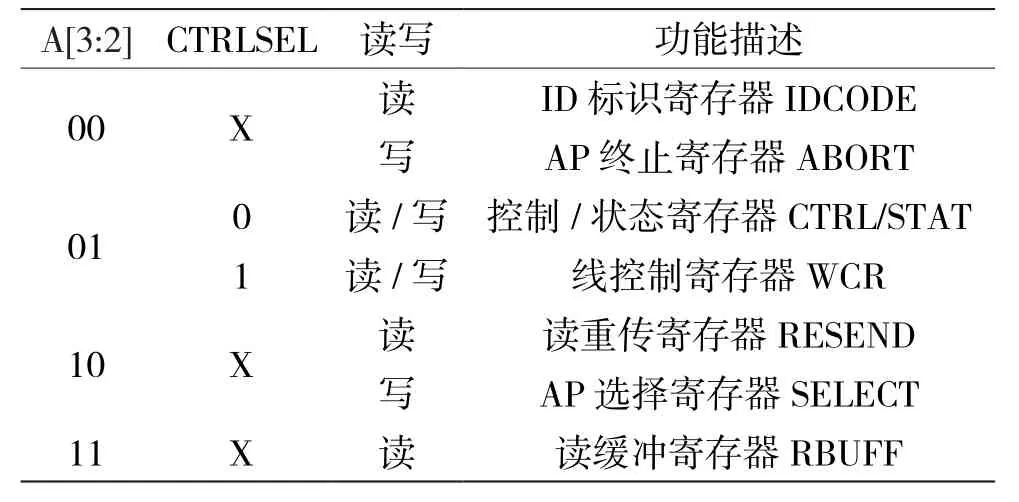

SWD中DP寄存器組成見表2,其中ID標識寄存器用于驗證SWD操作時序,獲取ARM調試接口信息等,低12位固定為0×477,主要構成如圖4所示。

表2 SW-DP寄存器

SELECT寄存器控制AP選擇特定的地址,其最低位為CTRLSEL,其組成見圖5。[31:24]位APSEL值確定當前AP地址的高8 bit;每個AP具有 16個 Bank,[7:4]位 APBANKSEL值(0-F) 用來選擇當前AP的Bank號;每個Bank有4個32 bit寄存器,由數據請求包REQ中的A[3:2]位來確定。

圖6列舉了每組MEM-AP寄存器的信息,其中Bank 0x0中的CSW寄存器、TAR寄存器與DRW寄存器對設備ARM核的數據傳遞起著關鍵作用[4]。

1.2 SWD實現處理器資源傳遞

SWD的數據傳遞通過分級傳遞的方式:第一級通過DP接口選擇進入AP寄存器,然后通過AP接口選擇目的寄存器進行訪問;第二級配置CSW寄存器進行軟件控制與地址模式的選擇,最后通過TAR寄存器與DRW寄存器對處理器目標地址進行讀寫。整個交互流程如圖7所示。

以下是實現的主要函數。

(1)Func0:單32 bit數據寫入,經歷①②③④⑥這5個階段,參數為其③階段的目的地址與④階段的數據,⑥階段僅需執行讀操作。

(2)Func1:連續32 bit數據寫入,SWD協議中支持連續寫入,目的地址會在寫入完成后自加1,大致流程與Func0一致,經歷①②③④…④(n個④)⑥階段,其中④階段的個數n由寫入數據數量來確定。

(3)Func2:單32 bit數據讀取,經歷①②③⑤⑥這5個階段,參數為其③階段的目的地址與接收⑥階段的數據緩存。

(4)Func3:連續32 bit數據讀取,SWD協議中目的地址會在讀取完成后自加1,大致流程Func2一致,經歷①②③⑤⑥…⑥(n個⑥)階段,其中⑥階段的個數n由讀取數據數量來確定。

2 STM32F103核心資源

為了利用SWD接口完成對ARM-Cortex M3/M4等芯片固件的擦除與燒寫,實現固件的更新。本節以ST公司的STM32F103x系列芯片作為說明,對芯片內部資源架構進行基本介紹[5]。

如圖8所示,STM32F103x采用ARM Cortex-M3核,采用32位RISC精簡指令集,時鐘頻率最高72 MHz。Flash容量最大512 kB、SRAM最大64 kB,STM32F103x芯片內部存儲資源如圖8所示,其中Flash區存儲了芯片的BootLoader與主程序。DAP燒錄器、J-link編程器進行芯片固件燒錄也是在該區域完成。

通過SWD接口可實現STM32F103x芯片SRAM區域存取訪問,控制Cortex-M3內部資源中調試寄存器,讀取Flash區的數據。Flash區不能直接進行數據擦寫,必須通過特定方法,本文研究的主要目的就是通過SWD與芯片Flash算法文件FLM相結合的方式實現芯片固件更新。

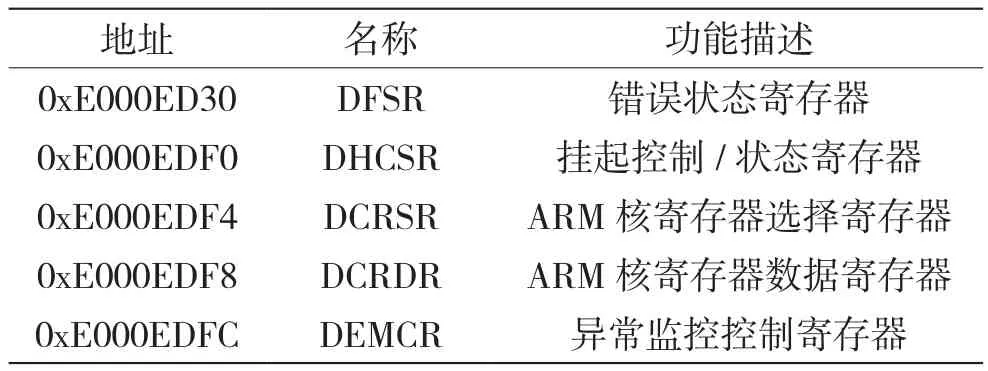

Cortex-M3/M4的ARM核調試寄存器地址完全相同,寄存器相關描述如表3所示。DFSR寄存器用來獲取ARM核運行錯誤狀態,DHCSR與DEMCR可以控制ARM核的運轉狀態,操作SRAM區域或者Flash資源時都應將ARM核掛起,以免影響數據正確性。DCRSR寄存器用來選擇ARM核心寄存器,DCRDR寄存器用來管理ARM核心寄存器值[6]。

表3 Cortex-M3/M4調試寄存器說明

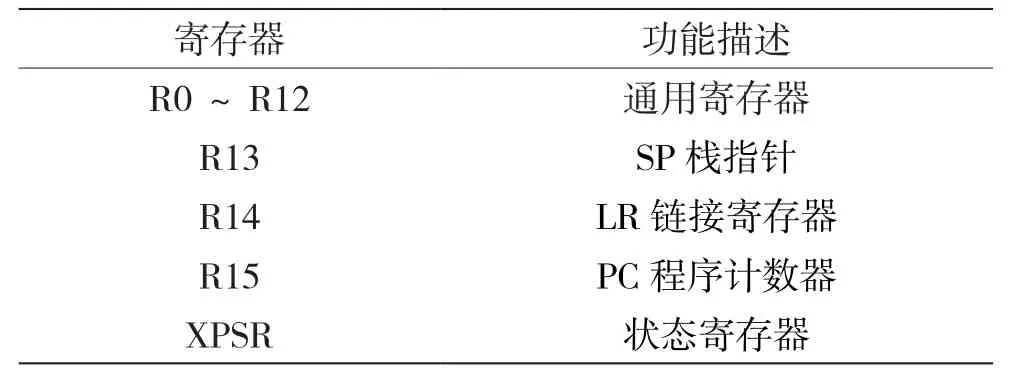

ARM核心寄存器組成如表4所示,其中R0~R12為32位通用目的寄存器,R13可對堆棧空間進行存取操作,R14鏈接寄存器用于存儲子程序或者函數調用的返回地址,R15程序計數器讀操作返回當前正在執行的指令加上4,寫入R15會導致程序跳轉執行。XPSR程序狀態寄存器作為特殊功能寄存器用來判斷ARM核心寄存器執行狀態是否正常。

表4 ARM核心寄存器

匯編可執行程序就是在ARM核心寄存器上進行變量的計算與處理。通過調用Func0、Func2流程可以控制Cortex-M3/M4的所有調試寄存器,經由DCRSR與DCRDR寄存器實現ARM核心寄存器讀取,獲取到ARM核的執行控制權限。

3 SWD實現芯片固件ISP在線編程

通用Flash芯片編程流程包括:初始化、擦除與燒寫。SWD協議調用FLM文件中可執行二進制文件的方式實現Flash的ISP編程。FLM文件從芯片廠家獲取,由Flash擦寫相關函數及變量等組成的通用標準文件格式可執行文件編碼。本文以STM32F103芯片的STM32F10x_128.FLM文件為樣本進行研究與應用,可推廣至所有支持SWD協議芯片進行應用。

3.1 STM32F10x_128算法文件解析

STM32F10x_128.FLM文件可通過elfparser等軟件解析,也可在Linux Ubuntu操作系統下輸入以下命令查看解析文件信息readelf -a STM32F10x_128.FLM。

截取的部分重要信息如圖9所示,其中Prgcode程序代碼段包括Flash的若干函數執行碼,PrgData程序數據段為全局變量/靜態變量區間。SWD所需的核心內容(Prgcode+PrgData)數據段可由地址Addr、偏移Offset與大小Size從FLM件中獲得。

3.2 STM32F10x_128讀取IDCODE

圖10由示波器獲得,下方波形為SWD時鐘,上方波形為SWD數據。以數據線的第一個高電平為Start起始位,對比SWD讀操作原理圖,最終獲取的內容為0x2ba01477。參照1.1節DP寄存器中有關IDCODE的描述,能夠驗證獲取到內容確實為IDCODE的值,進而確認已成功實現對SWD接口控制。

3.3 芯片Flash固件燒寫

通過SWD接口實現ARM核Flash資源燒寫共分為3個步驟:

(1)通過調試寄存器掛起ARM核,停止ARM核的運行,將FLM算法文件提出的可執行數據寫入SRAM的起始地址;

(2)將芯片固件STM32F10x_128.Bin寫入SRAM未用空間,待Flash編程時使用;

(3)將執行函數包括程序入口參數等信息通過調試寄存器寫入ARM核心寄存器,依次調用Flash初始化、片擦除、編程函數,完成ARM核內部Flash的燒錄。整個流程執行如圖11所示。

Flash固件燒寫測試程序由C語言實現,涵蓋了Flash初始化、片擦除、程序燒寫、數據回讀校驗及退出操作,頂層實現代碼如下文所述:

在主設備上執行Flash固件燒寫測試程序swdprogram,穩定地實現了芯片固件ISP更新,程序運行結果如圖12所示。

4 結 語

通過SWD接口協議控制芯片ARM核的運行,結合芯片FLM文件解析并在ARM核中實現Flash相關函數資源的恢復與調用,完成了芯片固件的ISP在線編程。針對其它支持SWD接口協議的ARM芯片,除內部資源地址空間與FLM算法文件不同外,ARM核的調試與控制操作完全相同,很容易推廣并應用于主從模式下的微處理器芯片。通過SWD接口實現的ISP在線編程,能夠極大地提高設備的維護性,對于實現設備程序升級與功能更新有較高的應用價值。