一種基于SRAM工藝FPGA的防克隆保護方法*

劉 賀,劉 瑤,楊 競,王小驥,劉星江

(中國電子科技集團公司第三十研究所,四川 成都 610041)

0 引 言

以現場可編程邏輯門陣列(Field-Programmable Gate Array,FPGA)為核心的可編程邏輯器件(Programmable Logic Device,PLD)因具有用戶可編程和在線動態重構的特性,方便了電子產品設計的修改和升級,提高了產品的靈活性和通用能力,縮短了產品的開發和上市時間,在現今的電子系統中得到廣泛的應用和迅速的發展。

在FPGA中使用的設計和配置數據代表了系統中知識產權的重要部分,然而FPGA設計面臨著克隆(Cloning)、反向工程(Reverse Engineering)、篡改(Tampering)和過度構建(Overbuildering)等威脅[1]。其中克隆是指通過復制獲得FPGA設計的相同副本,而不需要理解它是如何工作的,竊取方即可零設計成本仿造、偽造產品,這極大地損害了正品廠商的品牌聲譽和利益,隨著競爭變得越發激烈,FPGA內部設計電路和知識產權的安全性成為產品市場化必須考慮的因素[2]。

基于靜態隨機存取存儲器(Static Random-Access Memory,SRAM)工藝的FPGA具有易失性,每次上電都需由外部進行重新配置,這使得剽竊者可以輕松通過對FPGA的配置數據引腳進行采樣,得到該FPGA的配置數據流,實現對FPGA內部設計電路的克隆。

基于反熔絲等技術的FPGA芯片雖然可以很好地解決防克隆、逆向工程破解、篡改等問題,但限于如規模、成本或技術等各方面的原因,在國內外基于SRAM工藝的FPGA仍處于主流地位。這使得對基于SRAM工藝的FPGA芯片的防克隆研究具有重要現實意義。

為此,本文提出一種由FPGA外置安全電路結合雜湊算法(HMAC方式)和偽隨機序列生成等技術手段進行合法性認證檢測來提高FPGA防克隆的安全設計方法。

1 技術理論支撐

本文綜合運用了雜湊密碼算法的可認證性、FPGA器件本身固有的組合電路因競爭冒險現象而導致信號變化的不確定特性、線性反饋移位寄存器的簡單易于硬件實現特性,構建了FPGA基于密碼的一次一認證防克隆安全保護手段。

1.1 雜湊算法

雜湊算法可以將任意長度的消息壓縮成固定長度的摘要。給定1個消息計算其雜湊值是容易的,但是找到具有相同雜湊值的2個不同消息是困難的。除了數據壓縮、易于計算這兩個基本屬性,雜湊算法還滿足三個安全屬性:單向性(抗原像攻擊)、弱抗碰撞性(抗第二原像攻擊)、強抗碰撞性(抗碰撞攻擊)[3]。哈希信息驗證碼(Keyed-Hashing for Message Authentication,HMAC)用秘密密鑰與雜湊算法結合來產生固定長度消息認證碼,其安全性建立在雜湊算法基礎上,可用來作加密、數字簽名、報文驗證等。

1.2 競爭與冒險

信號在FPGA器件內部通過連線和邏輯門時,都有一定的延時,延時的大小與連線的長短和門單元的數目有關,同時還受器件的制造工藝(片與片間有物理誤差)、工作電壓(供電也有誤差)、溫度等因素的影響。在門電路中,兩個輸入信號同時向兩個相反方向的邏輯狀態轉換,即一個從低電平變為高電平,另一個從高電平變為低電平,或反之,稱為競爭。由于競爭而在電路的輸出端可能產生尖峰脈沖的現象稱為冒險。

數字電路設計中的競爭和冒險現象所導致的不確定性是十分頭疼的問題,本文將利用這種因不確定性而導致的數據采樣不可預測特性來完成保護設計。

1.3 線性反饋移位寄存器

線性反饋移位寄存器是指給定前一狀態的輸出,將該輸出的線性函數再用作輸入的移位寄存器,其結構簡單、容易實現、成本低、性能優,非常適合用于硬件實現[4],在通信系統中常用于構成偽隨機數發生器。其特性通常由移位寄存器級數、初始狀態、反饋邏輯和時鐘周期等共同決定。

2 方案設計

本文在參考文獻[5]和文獻[6]的設計方法和理念基礎上進行方案設計,其中文獻[5]的方法為在CPLD和FPGA中預置8組相同的密鑰表,通過每次傳遞不同的隨機數來同步雙方密鑰選擇,使用M序列(Maximum-length Sequences,最長線性反饋移位寄存器序列)對選定的密鑰加密后由解密方確認雙方選擇的密鑰是否一致來判定FPGA使用是否合法,該方法主要通過M序列算法安全強度來保證FPGA內IP core的合法使用,可選擇的密鑰只有有限組,在M序列算法被破譯后,克隆方可通過截獲、分析線路數據并通過窮舉方式,根據規則重放模擬認證過程。文獻[6]通過外置安全電路對FPGA進行基于雜湊算法和AES算法的身份認證、產權認證的雙重認證保護,雜湊算法僅用于保護數據完整性,其FPGA身份認證過程交互較為復雜,需要兩種算法支撐,從而額外消耗大量硬件資源,并且對外置安全芯片的安全性和性能也具有較高要求。同時其設計中以口令為輸入條件的認證方式,只適用于具備人機接口的設備使用,應用范圍受限。

本文在上述研究基礎上,以不浪費系統資源、不增加系統開銷負擔,同時考慮經濟效益與破譯復雜度間進行平衡為原則,在有限范圍內保證設計安全性,達到防克隆的安全設計方法安全、可用、好用的目的,結合并繼承前述兩種安全設計方法各自的優點,同時進行適當的優化設計。

2.1 系統框圖

方案的設計核心為以增加外置安全保護電路方式配合FPGA完成上電后的合法性單向認證過程,認證由FPGA中保護模塊和外置安全保護電路交互實現。需保護的IP core在上電后不能正常工作,只有對外置安全保護電路的合法性進行認證成功后,IP core才能獲取自身參數完成啟用過程。

同時,不同于前述方案中FPGA合法性認證成功后以單一使能信號啟用IP core的方式,本方案根據IP core的設計特性,提取其中參與完成核心功能的重要參數信息作為IP core啟動鑰匙,在使用合法性認證成功后,內部控制電路將此信息傳遞給IP core以完成啟用過程,同時該參數信息作為密鑰參與認證過程的保護,將保護對象與保護過程一體化融合設計。

認證過程利用可編程邏輯器件在應用設計過程中的競爭與冒險現象并結合線性反饋移位寄存器的簡單易于硬件實現特性,產生隨機特性良好的隨機數作為不可重復的認證變量,利用雜湊算法的HMAC方式良好的基于密碼的認證特性對認證過程加以保護,達到FPGA對外置保護電路的合法性保護。

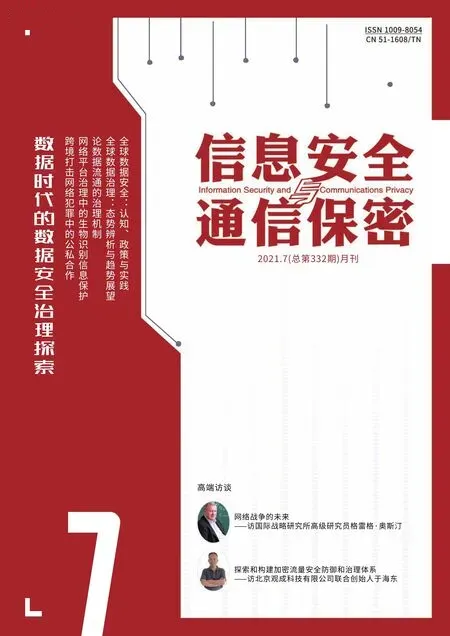

本方案設計的系統框圖如圖1所示。

圖1 系統框圖

安全保護電路作為設計的重要部分,其自身的安全性與整體設計強相關,以達到ASIC的安全水平為目標,綜合考慮設計成本、使用維護方便度以及該電路承載的設計實現復雜度較低的特點,本方案選用上電自啟動且難以通過物理手段進行反向工程的CPLD或小規模反熔絲FGPA進行設計。同時從更經濟角度考慮,也可以與供電電池配合使用小規模SRAM工藝FPGA進行設計,在設備出廠前通過JTAG對其加載配置文件,在其使用生命周期內由電池維護其內部程序,無需重新加載,同樣可具備較好的安全特性。

隨機序列生成模塊實現認證過程隨機數據生成功能,其根據使用環境的電壓、溫度等環境特性結合各類芯片個體固有的物理差異特性,保證每次認證過程中FPGA使用該模塊自主生成不可預測、不重復的隨機數據,防止克隆方采集線路數據重放以仿冒認證過程。

IP core參數存儲模塊對IP core的核心功能要素進行抽象提取,在認證過程充當認證保護密鑰,在認證成功后作為啟用鑰匙輔助完成IP core的功能啟用。

雜湊算法模塊承擔認證過程校驗值計算功能,使用其HMAC方式,以IP core中抽取的核心參數作為密鑰,進行認證數據的完整性及可認證性保護,以基于密碼的安全特性保證安全保護電路的合法性。在設計驗證時使用國家密碼管理局發布的SM3雜湊算法,其安全性和效率與SHA-256相當,實際使用時可根據情況簡化設計,在一定安全范圍內降低算法的實現規模。

安全保護電路內部的隨機序列檢測模塊,在內部保存多組已認證過的隨機數,對新啟用的隨機數進行重復性檢測,檢測到重放數據則終止認證過程。

FPGA內部的合法性驗證模塊將FPGA計算生成的校驗碼與安全保護電路生成的校驗碼進行一致性校驗比對,通過后由安全控制電路提取IP core參數,使能IP core的全部功能。

2.2 工作流程

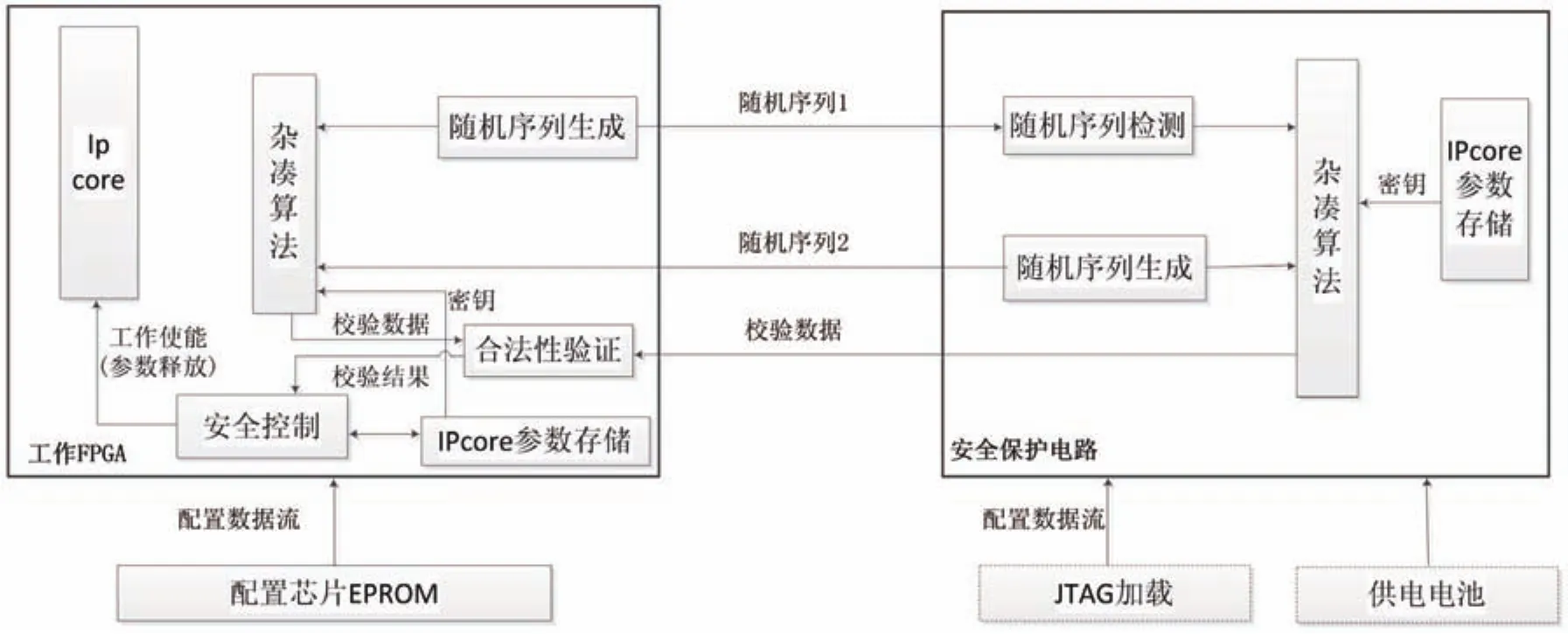

本方案的工作流程如圖2所示。

圖2 工作流程

認證交互流程:

(1)FPGA上電后,通過隨機序列生成模塊發送隨機序列1。

(2)安全保護電路檢測隨機數是否重復,如不重復使用自身的隨機序列生成模塊生成隨機序列2,使用IP core參數和雜湊算法的HMAC方式計算序列1、2的雜湊值,將隨機序列2與雜湊值發送給FPGA。

(3)FPGA接收隨機序列2后,以同樣方式計算序列1、2的雜湊值與安全保護電路雜湊值進行比對。

(4)校驗成功,則FPGA釋放IP core參數,使能IP core。

3 關鍵模塊的設計實現

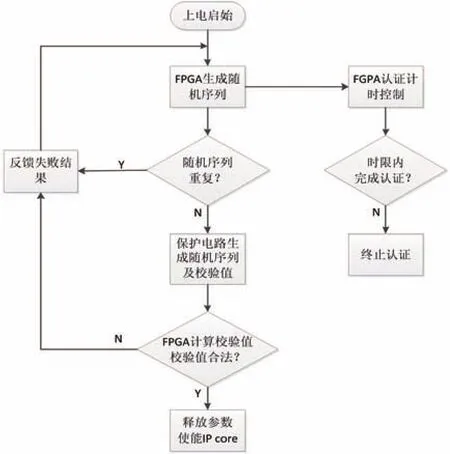

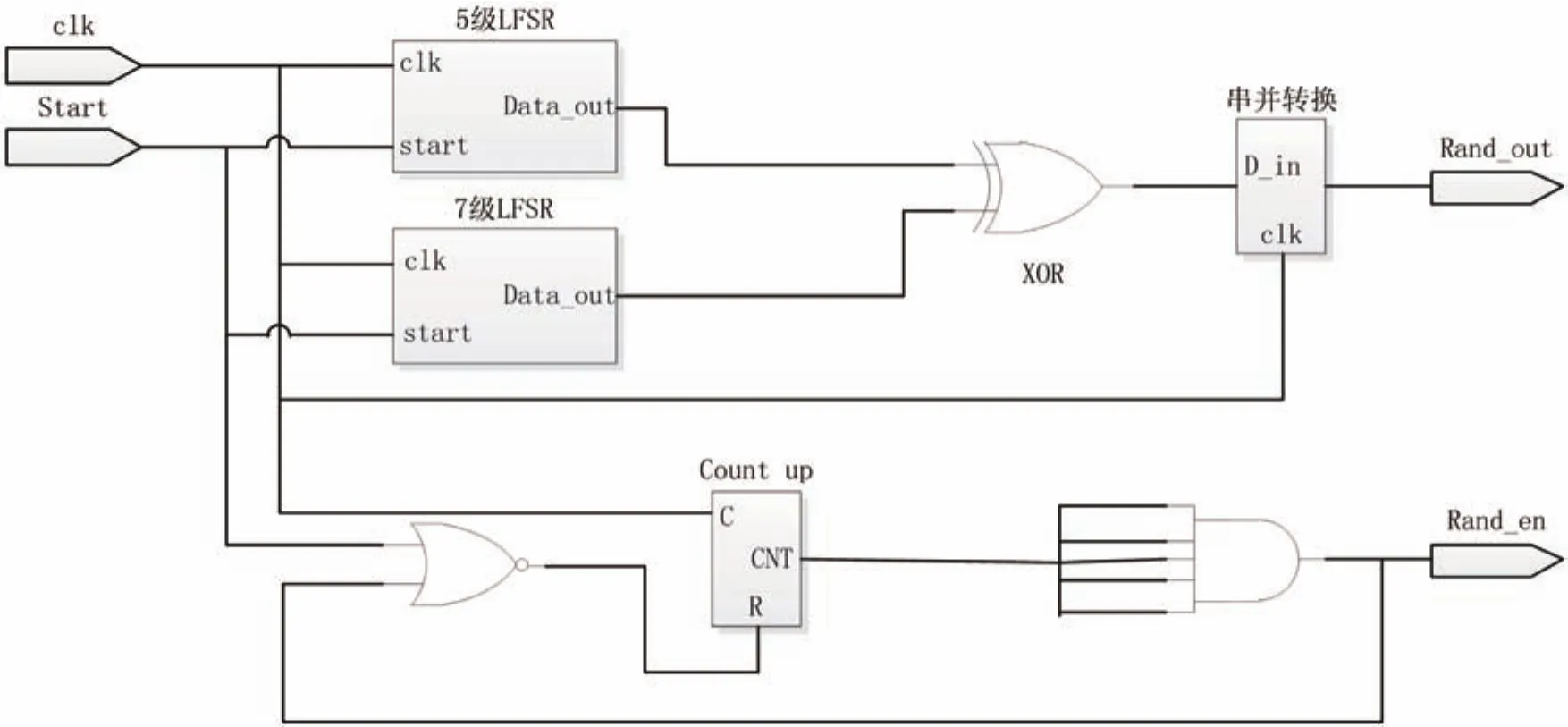

本方案中由FPGA內部電路產生良好隨機性的隨機數,設計簡單、易于實現,不占用過多的硬件資源,是該安全保護方法安全性保障及設計可用性的重要一環。本方案設計的隨機數由一個5級和一個7級的純組合邏輯實現的LFSR抽頭異或后由外部時鐘采樣生成,利用了組合電路的競爭冒險現象,并結合電子器件信號受外界環境影響和自身固有物理差異,對單FPGA芯片而言,每次上電時,因FPGA芯片所處環境的溫度、氣壓等因素都會有所波動,導致門電路的延時特性在每次上電時都有些微差異,而單LFSR模塊為完全由門電路組成的組合電路,其抽頭輸出數據與門電路的時延特性密切相關,因此在確定的時鐘域上具有不可預測性,隨著反饋級數的增加,這種不可預測性更加明顯,當由固定時鐘對生成的數據采樣時,因被采樣數據與該時鐘對應的頻率和相位均具有不確定性,因此產生了一個難以預測的序列,當兩種不同級數LFSR產生的隨機序列通過異或門電路使用后將放大這種不確定性,確保了每次上電生成的隨機數具有不重復的特性,而對不同型號FPGA或同一型號內的不同個體而言,因工藝水平和制作工藝本身的誤差,導致不同FPGA芯片內部電路物理特性不一致,確保了FPGA個體間生成的隨機序列具有不重復特性。隨機序列生成模塊電路設計如圖3、圖4所示。

圖3 組合邏輯實現5級LFSR模塊

圖4 隨機序列生成模塊

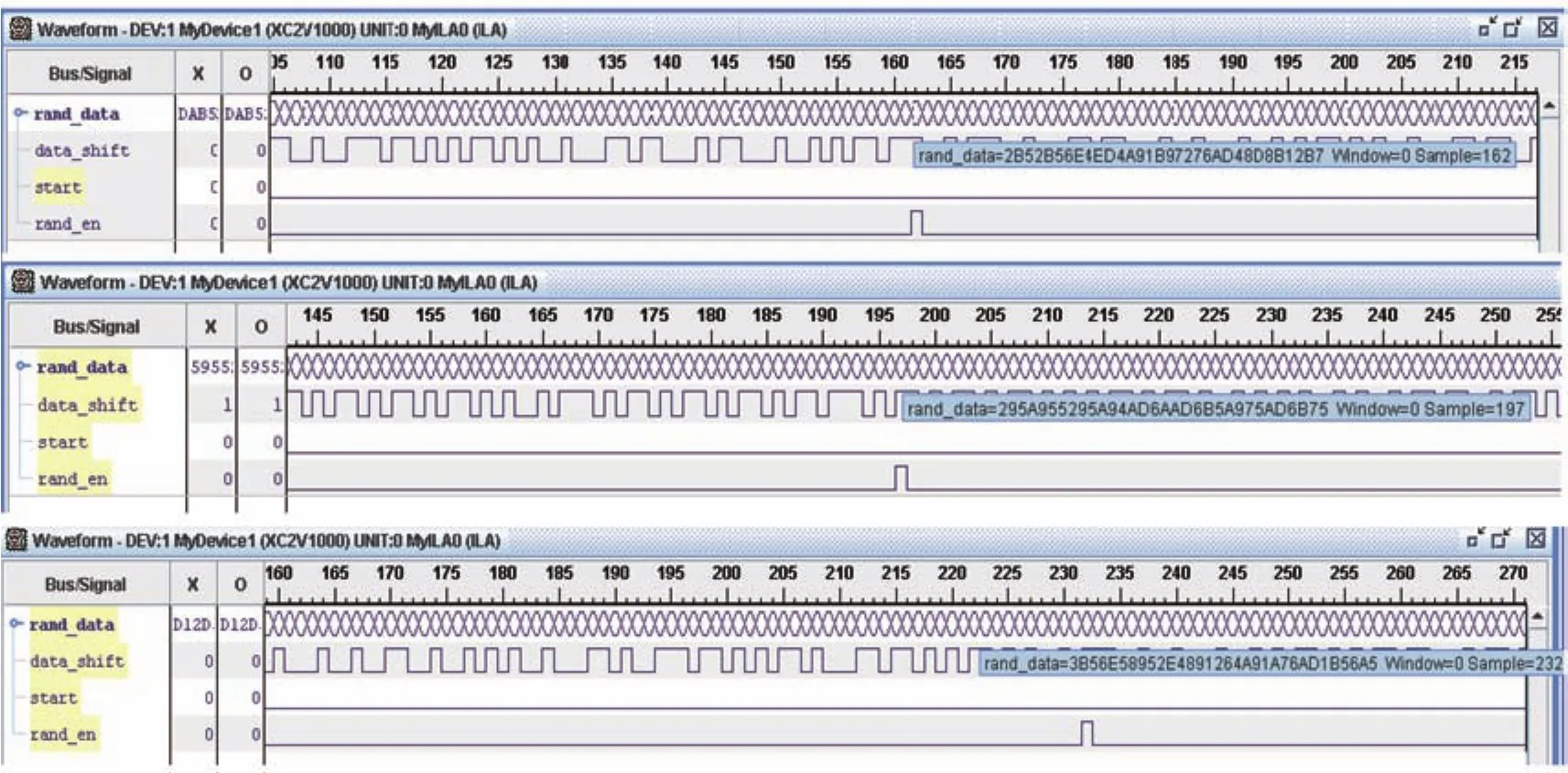

本設計在Xilinx公司xc2v1000器件環境下,利用其輔助ChipScope工具多次抓取的隨機數生成實測結果,如圖5所示,生成的隨機數符合一次一變不重復的特性。

圖5 隨機序列采集結果

4 安全性分析

(1)防仿冒攻擊。FPGA對外置保護電路實行單向身份合法性認證,通過雙方共享的IP core參數作為保護密鑰,用于認證數據生成,第三方在不能獲取密鑰數據的情況下,依據雜湊算法HMAC方式的密碼保護特性,其無法通過偽造認證數據方式通過FPGA的合法性認證判斷。

(2)抗重放攻擊。FPGA每次認證開始時根據應用環境特點由內部電路產生隨機數,第三方無法控制FPGA生成隨機數的隨機特性或掌握其生成規律,因而認證數據具有一次一變特性,任何對線路上截取的過往認證數據的重放都與FPGA當前產生的隨機數據不一致,FPGA對非當前使用隨機數生成的認證數據均判定為非法數據,導致認證失敗。同時外置保護電路也以同樣機制產生新隨機數參與認證計算,并對FPGA產生的隨機數進行重復性檢測,輔助增強了設計的抗攻擊能力。

(3)防窮舉攻擊。認證過程中由FPGA內部電路生成的隨機數長度以4字節為例,其變化量達到232=4294967296,多種可能的變化使得第三方無法通過窮舉截取線路數據的方式來偽造認證過程,同時通過適當調整隨機數長度可達到更高的保護效能。

(4)防篡改攻擊。消息認證碼基于密碼算法生成,其保護范圍為FPGA和外置保護電路各自產生的隨機數據,對線路傳輸的任何數據的改動都將導致認證過程失敗。

(5)可用性。本方案設計的認證過程簡單、實用、高效,通過二次握手即可完成FPGA對外置保護電路的合法性認證;雙方交互的數據量小,在滿足安全性需求的條件下,隨機序列長度取4字節,消息認證碼取8字節,則一次認證過程的通信開銷只有16字節;代碼實現簡單,綜合考慮破譯難度和經濟成本間的平衡,保護方案只使用易于硬件實現的LFSR以及實現復雜度較低的雜湊算法,在滿足第三方對認證過程的破譯成本與IP core的開發成本相當的前提下,可使用復雜度更低的雜湊算法以降低對硬件資源的開銷,本設計使用簡易、低成本的電路和芯片即可完成外置保護電路的功能。

5 結 語

本文分析了基于SRAM工藝FPGA設計中包含的知識產權存在被克隆風險產生的原因及可能造成的嚴重損失。通過設計外置安全保護電路方式,利用FPGA器件固有的物理差異及環境敏感特性產生一次一變的隨機數據,結合雜湊算法HMAC方式的可認證性,設計了對該類型FPGA的IP core通過一次一密認證成功后才能正常工作的防克隆保護方法。設計僅需額外增加簡易且低成本的外圍電路資源,易于工程實現,安全性較高,具有良好的實用價值。