環形鏈輪詢復用測試端口的高效測試結構

張 玲,鄺繼順

(1.江西財經大學軟件與物聯網工程學院,南昌 330013;2.湖南大學信息科學與工程學院,長沙 410082)

0 引言

測試功耗過高、測試集規模過大和由其引起的測試應用時間過長的問題是數字集成電路成本高的主要原因。如何降低集成電路測試數據規模和測試功耗成為富有挑戰性的研究熱點[1]。好的測試結構能以合理的硬件代價、較短的測試數據移位路徑實現對集成電路(Integrated Circuit,IC)內部結點的“觀察”和“控制”,將電路多個測試需求統一,獲得較好的測試效果。測試結構設計是個老問題,也一直是集成電路測試的關鍵問題。

掃描測試是數字集成電路測試方案的基本手段,它通過將時序電路中的全部或部分時序單元設置成掃描單元來控制和觀察相應電路結點的值。直鏈結構是最早提出的通用掃描結構,單直鏈結構[2]將電路中的觸發器串聯成單獨掃描鏈,由于其測試數據移位路徑較長,移位時間和能耗都比較大;多掃描直鏈結構[3]將單掃描鏈分成多個較短的直鏈,用較多的測試端口換取測試應用時間的減少和測試移位路徑的縮短,但測試數據規模沒有變化。為降低測試功耗和減小測試集規模,針對測試集的優化方法通過低功耗的測試產生算法[4],掃描鏈重排序技術[5]和無關位的填充[6]等來獲得測試功耗的降低和測試集規模的減小;針對直鏈結構的優化主要通過掃描鏈的阻塞和重組[7]或阻隔掃描單元[8]來獲得測試功耗的降低[9]。循環掃描結構[10]在直鏈結構的基礎上首尾相連,其設計初衷是為電路建立自測試結構,實現零存儲測試,它可以獲得傳統線性反饋移位寄存器自測試結構的效果,卻有著普通直鏈相當的硬件代價[11]。循環掃描結構可實現測試數據的重用,因此它不僅可充當移動測試數據的通路實現確定性測試,而且可實現測試響應作為下個測試向量的測試模式[12],但其功耗沒有降低。隨機訪問掃描(Random Access Scan,RAS)結構[13]可像隨機存儲器那樣根據地址隨機訪問電路中的掃描單元,因此它提供了一種理想的可測試結構,理論上其測試時間和功耗問題都能得到較大改善;但電路中觸發器的分布隨機,硬件代價非常大,布線難以實現。針對RAS 的多數工作都是在如何減少硬件代價上[14]。

為改善測試結構本身導致的移位功耗,設計低功耗的測試結構,我們前期提出的代表掃描結構[9]將電路中的觸發器分成多個環形鏈,為每個環形鏈遴選一個“代表”,這些代表組成測試數據的移位路徑,實現對電路的分級管理,降低了測試移位功耗;但由于該結構的環形鏈和代表組成的代表鏈共用測試端口,它最大的缺點就是相對于直鏈結構,測試時間會有所損失,假設電路中有x個環形鏈,則每個測試向量的應用會有x個時鐘周期的時間損失。為克服該缺陷,并進一步降低測試移位功耗,本文提出環形鏈輪詢復用測試端口的測試結構RRR Scan,該結構將電路中的觸發器設計成多個環形鏈,并串聯環形鏈成為測試數據通路,實現測試端口的輪詢復用。環形鏈的環形移位模式具有測試數據重用的特性,可以減小測試數據規模;而其輪詢復用則縮短了測試數據的移位路徑,具有低功耗的特性。該結構除具有通用掃描結構的所有性質外,本身還具有低功耗、數據重用的特性,靈活性大大增加。

1 環形鏈輪詢復用測試端口的測試結構

1.1 環形鏈輪詢復用測試端口的結構原理

圖1 給出環形鏈輪詢復用測試端口的結構示意圖,該結構包含n個環形鏈,測試時,環形鏈可工作于三種模式:直鏈掃描模式、隱身模式和環形移位模式。當為第i個環形鏈傳輸測試數據時,則該環形鏈處于直鏈掃描模式,其他環形鏈處于隱身模式(數據流向見圖中虛線)。相對于傳統直鏈來說,該結構較大地縮短了測試數據的移位路徑,因此降低了測試移位功耗。對于每個環形鏈來說,可工作于環形移位模式,因此可實現測試響應作為下個測試向量的測試模式,實現了測試數據的重用。該結構根據電路觸發器的物理分布布線,將物理上相近的觸發器設置在一個環形鏈中,并根據測試端口個數將這些環形鏈串聯成多個測試數據通路,不會產生較大的布線代價。但是,如何實現該結構,并以較小的硬件代價對該結構的工作過程進行準確控制是關鍵,也是難點。

圖1 環形鏈輪詢復用測試端口結構的示意圖Fig.1 Schematic diagram of RRR Scan architecture

1.2 結構的實現

為以較小的硬件實現該結構,本文將電路中的觸發器設計成同樣結構的環,見圖2,設該結構包含n個環形鏈,每個環形鏈包含x個觸發器,還剩下m個掃描單元(m<x),環形鏈i包含的觸發器編號依次為FFi1,FFi2,…,FFix,對應的時鐘信號表示為CLOCKi,測試主路徑(Main path,Mp)在圖中用虛線給出。環形鏈中的掃描單元與傳統掃描單元一樣,由Scan_Enable(SE)使能,只需在環形鏈i的入口掃描單元FFi1上增加一個二選一選擇器,用來選擇來自外部的測試數據(Mp上的數據)和來自掃描鏈本身的測試數據,在出口掃描單元FFix上增加一個二選一選擇器,用來選擇來自環形鏈的測試數據或來自外部的測試數據(Mp的測試數據)。

表1 給出了環形鏈輪詢復用端口的測試結構的工作模式(圖中X 表示無關位,其值可以為0 或為1)。如表1 所示,SE=0 時,該電路工作于功能模式(Functional mode),如表中第一行所示。SE=1時,電路處于測試模式,以圖2中的環i來說明,Ci1=0,Ci2=1,則FFi1選擇來自Main path(Mp)上的數據,即Oi1=Mp=Scan_in;而對于FFix來說,Ci2=1,它被Main path 選擇,即Oi3=Oi2,此時環i工作于直鏈掃描模式(Linear scan mode),如表中第二行所示。Ci1=1,Ci2=1,則FFi1選擇來自FFix的數據,即Oi1=Oi2;而對于FFix來說,Ci2=1,它被Main path選擇,即Oi3=Oi2,此時環i工作于循環移位模式(Ring shift scan mode),實現了測試響應作為下個測試向量的測試模式,如表中第三行所示。Ci2=0,對于FFix來說,Oi3=Scan_in,所以Ci1無論為什么值(用x表示),環形鏈均被隱藏,此時環i工作于隱身模式(Stealth scan mode),實現了測試數據移位路徑的縮短,如表中第四行所示。

圖2 環形鏈輪詢復用測試端口的一個測試通路結構Fig.2 Architecture of one test access of RRR Scan

表1 工作和掃描模式的控制Tab.1 Control of work and scan modes

圖3 給出包含11 個觸發器的掃描通路的例子,11 個觸發器被分到3 個環形鏈中,其中每個環形鏈包含3 個觸發器,觸發器編號如圖3 所示,從右到左分別為第0 個環形鏈(由觸發器FF01、FF02、FF03組成)、第1 個觸發器(F11、FF12、FF13組成)和第2個環形鏈(由觸發器FF21、FF22、FF23組成)。作為通用掃描結構,假設其任意兩個相鄰測試向量為V1和V2,對應測試響應為R1,R2,其中:V2對應的測試數據為(V21,V22,V23,V11,V12,V13,V01,V02,V03,V0),它們分別對應觸發器FF21,FF22,FF23,FF11,FF12,FF13,FF01,FF02,FF03的測試數據;V1對應測試響應數據為(R21,R22,R23,R11,R12,R13,R01,R02,R03,R0),分別對應觸發器為FF21,FF22,FF23,FF11,FF12,FF13,FF01,FF02,FF03的測試響應。其具體工作過程在表2中給出。

圖3 環形鏈輪詢復用測試端口結構的例子Fig.3 Example of RRR Scan

如表2 所示:第一列表示測試時間,單位為時鐘周期;第二、三、四列分別表示三個環形鏈的掃描模式;最后一列為測試數據的應用過程。如表1 所示,在第一個時鐘周期,為了將直鏈上的測試數據送入,并將測試響應移出,三個環的第3 個掃描單元的選擇器C22、C12、C02均為0,即都選擇來自數據通路Mp上的數據,處于隱身模式,它們的時鐘CLOCK 均為0,處于維持狀態,此時完成掃描單元F0的測試數據R0的移出和V0的移入,如表中第二行所示。

表2 環形鏈輪詢復用測試端口結構工作過程的一個例子Tab.2 One operation example of RRR Scan

在第2~4 個時鐘周期,對于環形鏈0 來說,它的第1 個掃描單元的選擇器的控制信號C01=0,所以選擇器輸出O01=Scan_in;它的第3 個掃描單元選擇器的控制信號C02=1,因此輸出O03=O02,即該環被展開,并串到鏈上;對應時鐘CLOCK0等于掃描時鐘clk,環0工作于直鏈模式;C22、C12均為0,因此環1 和環2 依舊工作于隱身模式,保持數據。這3 個時鐘周期為環0傳輸測試數據,完成測試響應R01、R02、R03移出和測試向量V01、V02、V03的移入,如表第三行所示。

在第5~7個時鐘,環形鏈1的第一個掃描觸發器的選擇器控制信號C11=0,對應輸出O11=Scan_in;第三個掃描單元控制信號O12=1,對應輸出O13=O12;對應時鐘CLOCK1等于掃描時鐘clk,環1 工作在直鏈模式;C22,C02均為0,因此環0 和環2 工作于隱身模式,此3 個周期為環1 傳送測試數據,完成測試響應R11、R12、R13移出和測試向量V11、V12、V13的移入,如表中第四行所示。

在第8~10 個時鐘周期,第2 個環形鏈第一個掃描單元的選擇器控制信號C21=0,對應輸出O21=Scan_in;第三個掃描單元控制信號C22=1,對應輸出O23=O22;對應時鐘CLOCK2等于掃描時鐘clk,環2 工作于直鏈模式;C12、C02均為0,環1 和環0 工作于隱身模式,此3 個周期為環2 傳送測試數據,完成測試響應R21、R22、R23的移出和測試向量V21、V22、V23的移入,如表中第五行所示。

除可用于通用測試結構外,由于每個環形鏈可工作于環形移位模式,該結構還可用于數據壓縮場合。用于數據壓縮時,環形鏈工作于環形移位模式,測試響應在移出掃描鏈的同時,還傳送給掃描鏈作為下個測試向量使用。另外,該結構將物理上相近的觸發器設置在同一個環形鏈中,再將這些環形鏈根據測試端口個數分配到不同的測試通路中去,不會增加較多的布線代價,但布線問題和測試壓縮的具體應用不屬于本文討論范圍,本文主要討論具有數據重用和低功耗性質的通用測試結構。

2 環形鏈輪詢復用測試端口結構的分析

2.1 控制方式和實施方式

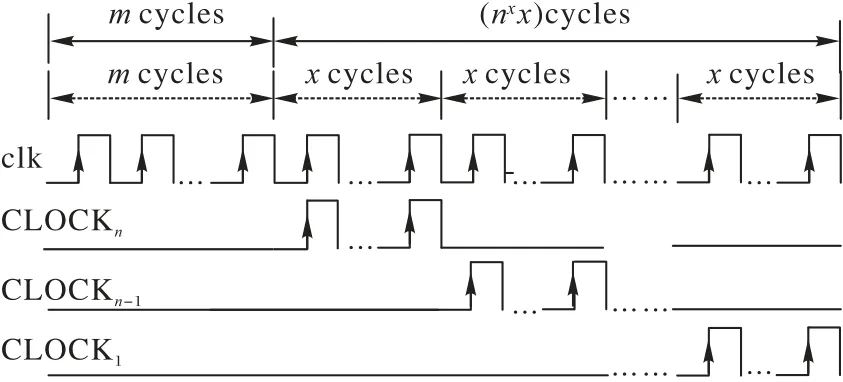

設該結構包含n個環形鏈,每個環形鏈具有x個掃描單元,還剩m(m<x)個掃描單元直接設置于Mp 上,則這n個環形鏈輪詢地使用測試端口(test pin),而其他環形鏈工作于保持模式,其時序控制在圖4中給出。圖4給出了一個測試向量的移入和其上個測試響應的移出過程,其中clk 為掃描時鐘,CLOCKn,CLOCKn-1,…,CLOCK1分別為第n個環形鏈、第n-1個環形鏈,…,第1個環形鏈的時鐘。

如圖4 所示,其具體時序描述如下:經過m個時鐘,將直鏈上的測試數據移入和移出;在下x個周期內,為環形鏈n移入測試數據,并移出測試響應,此時,環形鏈n的時鐘CLOCKn=clk,其工作于直鏈模式,而其他環形鏈的時鐘控制信號為0,工作于隱身模式;在下x個周期內,再以同樣的方式為環形鏈(n-1)分配測試數據和移出測試響應,直到完成n個環形鏈的測試數據的分配和移出,即完成了一個測試向量的應用和測試響應的移出。從該時序圖中可以看出,該結構中的每個環形鏈的時鐘控制信號CLOCKi是一組完全相同的信號,它們很容易從掃描時鐘信號clk 中獲得,而無須增加額外的測試端口。

圖4 環形鏈輪詢復用測試端口測試結構控制時序圖Fig.4 Control sequence diagram of RRR Scan

2.2 測試功耗和代價分析

與代表掃描結構[9]不同,該結構直接將不參與移位的環形鏈屏蔽掉,因此移位功耗的降低與屏蔽掉的路徑的長度有關,屏蔽掉的掃描單元越多,則測試數據移位時產生的功耗越低。與文獻[9]一樣,先假設任意兩個掃描單元之間的測試向量和測試響應均存在跳變,則可反映任意位置可能發生的跳變,并用Matlab對此關系進行了分析,其中所有電路均被設置成一個測試通路(多個測試通路的分析方法相同)。

圖5 給出針對電路S5378 和S9234 的分析結果,其中橫軸x表示環形鏈的大小,縱軸表示總的移位功耗(用總的跳變數WTC 計算[9]),圖中給出了掃描直鏈(Pcon)、代表掃描鏈結構(Prp)和本文提出環形鏈輪詢復用測試端口的測試結構(Prtm)的功耗結果。

圖5 移位功耗曲線圖Fig.5 Curve of shifting power consumption

從圖5可以看出,傳統直鏈的功耗與x無關,為固定值;對于代表掃描鏈,其功耗隨環形鏈x的增大呈先降低后升高的趨勢,因此存在功耗最低點;對于本文提出的環形鏈輪詢復用測試端口的測試結構,其功耗隨著x的增大而升高,一個極端情況,掃描通路中的所有掃描單元組成一個環形鏈,這時該結構就成了著名的循環掃描結構[10];而另一個極端,x=1,即每個掃描單元本身就是一個環形鏈,每個掃描單元都能被隨機訪問,該結構就成了隨機掃描結構(RAS)[13]。而在所有情況下,相對于傳統掃描直鏈結構和代表掃描結構,環形鏈輪詢復用測試結構都能獲得較低的測試功耗。除此之外,所有環形鏈均可工作在環形移位工作模式,可以實現測試響應作為下個測試向量的測試模式,實現了測試數據的重用。

實際上,我們對所有的ISCAS89 大時序電路以及ITC99電路進行了分析,所有移位功耗都是隨著環形鏈x的增大而增大,且它們的移位功耗曲線變化的規律完全相同,這是因為本結構中環形鏈大小的變化均是由1 到其最大值。當環形鏈為1 時,可隨機訪問每個掃描單元,功耗最小,但其布線較復雜,所需的選擇器較多;而當環形鏈達到其最大值時,即測試通路成為一個大的環形鏈,其移位路徑最長,相應的移位功耗也最大。而其他的移位功耗均位于兩個極端條件之間,在假設條件一致的情況下,它們的變化規律也會完全一致。從硬件結構上來看,相對于傳統的直鏈結構,環形鏈輪詢復用測試端口的測試結構在硬件代價有所增加,其硬件代價在于每增加一個環形鏈,會增加兩個二選一選擇器;相對于代表掃描結構[9]每個掃描單元都增加一個選擇器來說,其硬件代價大大減小。布線代價上來看,該結構可將物理上相近的掃描單元設置于一個環形鏈,可結合電路本身掃描單元的布局獲得優化的布線結構。從時延上來看,由于屏蔽了部分環形鏈,因此測試數據的移位路徑長度有所縮短,即其掃描鏈長度有所減小,時延有所減小。測試時間上來看,環形鏈輪詢復用測試端口的測試應用時間與傳統掃描直鏈一樣,而對于代表掃描結構,假設測試數據通路包含n個環形鏈,則每個測試向量多出n個時鐘周期的損耗。

由此可見,相對于傳統直鏈掃描結構和循環掃描結構,該結構提供了更大的靈活性。該結構可以通過環形鏈的大小來平衡硬件代價和移位功耗之間的約束,在對面積要求比較高的電路中,可以將環形鏈大小x設置得較大,從而在獲得較低測試功耗的同時,減小硬件代價;而在對功耗要求比較高的電路中,可以將環形鏈大小x設置得較小,從而在合理的硬件代價下獲得較高的測試功耗的節約。而相對于代表掃描結構,相同條件下,該結構均可通過較低的硬件代價減少更多的測試功耗。

3 實驗和分析

本文對傳統掃描直鏈、代表掃描結構[9]及本文提出的代表掃描鏈在Intel Pentium 2.13 Hz CPU,2.93 GB 內存的Linux C 環境下進行了對比。對比實驗主要是對ISCAS89 時序電路的mintest 測試集[15]進行了測試,假設單個測試端口(多個測試端口分析相同)從移位寄存器大小為1 到大小為N(N為掃描直鏈的所有掃描單元的個數)之間進行計算,功耗比較結果如表3 所示。其中:第一列和第二列分別為電路名稱和其包含的觸發器個數(FF),假設電路僅一個測試端口,因此被設置為全掃描的單個測試通路;第三列給出了掃描直鏈結構的總移位功耗P_sa;第四、五、六列分別給出代表掃描結構[9]的功耗最低點對應的x的值、最優功耗R_sa 和其相對于傳統直鏈所降低的移位功耗的比率sag1,其中sag1=(P_sa-R_sa)/P_sa;第七、八列給出了環形鏈復用測試端口測試結構的功耗結果,其中第七列給出該結構對應于代表掃描結構的功耗最低點x的功耗,第八列為其相對傳統直鏈所減少的移位功耗比率sag2,其中sag2=(P_sa-M_sa)/P_sa;最后一列為本文提出的環形鏈輪詢復用測試端口的測試結構的功耗M_sa相對代表掃描結構的功耗R_sa降低的移位功耗比率,其中sag=(M_sa-R_sa)/M_sa。

從表3 中可以看出,相對于傳統掃描直鏈,代表掃描結構和環形鏈輪詢復用測試端口的測試結構均較大程度地降低了功耗,對于S13207 來說,其環形鏈輪詢復用測試端口的測試功耗降低比率為99.58%;另一方面可以看出,代表掃描結構的功耗最低點,環形鏈輪詢復用測試端口的測試結構都獲得了較低的移位功耗,對于S38584 電路來說,其功耗最低點的減少比率為47.30%。

表3 測試移位功耗比較Tab.3 Comparison of test shifting power consumption

4 結語

測試集規模過大和測試功耗過高是數字集成電路測試的巨大挑戰,優化的通用測試結構不僅可以獲得較好的測試效果,而且可以減小功耗和測試集規模。本文提出環形鏈輪詢復用測試端口的測試結構,該結構將掃描單元設置到多個環形移位寄存器中,環形移位寄存器可工作于直鏈模式、環形移位模式和隱身模式,縮短測試數據的移位路徑,可實現測試響應作為下個測試向量的測試模式,降低了測試移位功耗,同時可用于測試壓縮,因此是一種本身具有低功耗和測試集重用的通用測試結構。理論和實驗均表明,該結構克服了代表掃描測試時間增大的缺陷,是一種低端口、低功耗、可測試數據重用的通用測試結構,不會增加額外的測試端口,布線代價合理。本文下一步工作是將該結構用于測試壓縮中,獲得較小的測試集規模。