基于FPGA的梳狀譜干擾技術(shù)研究及實(shí)現(xiàn)

高佳旭,趙立鵬

(哈爾濱工程大學(xué) 信息與通信工程學(xué)院,黑龍江哈爾濱,150001)

0 引言

隨著信息技術(shù)的迅猛發(fā)展, 電子系統(tǒng)在性能不斷提高的同時(shí)也變得越來(lái)越復(fù)雜。對(duì)電子對(duì)抗而言, 其最終目的是干擾敵方的無(wú)線電通信、制導(dǎo)、指令、引信以及雷達(dá)等系統(tǒng)。因此, 構(gòu)建干擾信號(hào)有著重要意義[1]。

現(xiàn)有的梳狀譜信號(hào)發(fā)生器大多數(shù)為模擬梳狀譜發(fā)生器,模擬梳狀譜發(fā)生器具有一定的使用局限性,如實(shí)際調(diào)試工作復(fù)雜,移植性差,工作頻率范圍有限,各次諧波幅度不一致,譜間隔不可調(diào)等[2]。

而利用FPGA等數(shù)字器件來(lái)產(chǎn)生滿足要求的窄脈沖就可以很好地解決了模擬電路實(shí)際調(diào)試工作復(fù)雜,移植性差的問(wèn)題[3]。所以本文采用FPGA結(jié)合DDS核來(lái)產(chǎn)生梳狀譜干擾信號(hào),可根據(jù)實(shí)際系統(tǒng)需求實(shí)現(xiàn)可變中心頻率及帶寬、可變頻點(diǎn)數(shù)的高性能梳狀譜信號(hào)輸出,極大克服了現(xiàn)有梳狀譜發(fā)生器的缺點(diǎn),提升了梳狀譜發(fā)生器的性能。

1 梳狀譜干擾技術(shù)研究

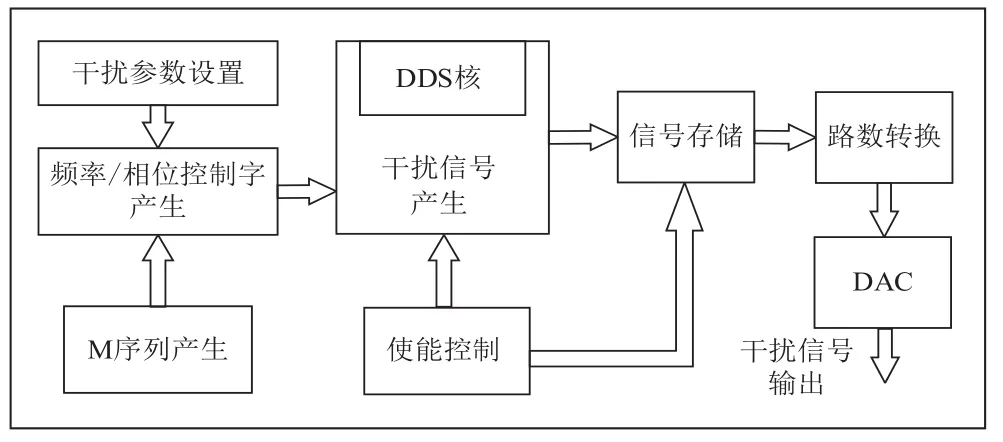

梳狀譜干擾是一種在一定帶寬內(nèi),一系列窄帶干擾信號(hào)的疊加,其表達(dá)式為:

式中:Jk(t)是第Ak(t)個(gè)窄帶干擾信號(hào);Ak(t)是第k個(gè)窄帶干擾信號(hào)的包絡(luò);?k(t)是第k個(gè)窄帶干擾信號(hào)的相位;ωk是第k個(gè)窄帶干擾信號(hào)載波頻率。

式(1)中的梳狀頻譜干擾信號(hào)表達(dá)式是L個(gè)窄帶干擾信號(hào)的疊加組成的。它的幾個(gè)主要參數(shù)均可以靈活選擇。例如,頻率間隔可以是等間隔也可以是不等間隔的;每個(gè)干擾頻段的調(diào)制方式既可以相同也可以不同;每個(gè)窄帶干擾的帶寬可以相等或不相等。每個(gè)窄帶干擾信號(hào)的幅度可以相同也可以不同;其干擾頻率也可以靈活設(shè)置。

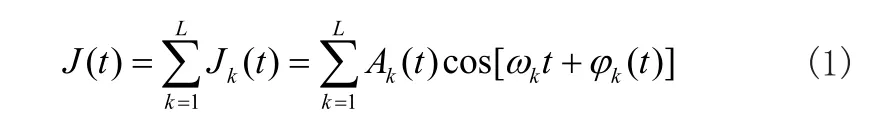

2 梳狀譜干擾信號(hào)的FPGA實(shí)現(xiàn)

梳狀譜干擾信號(hào)實(shí)現(xiàn)的主要流程如圖1所示。

圖1 梳狀譜干擾信號(hào)FPGA實(shí)現(xiàn)流程圖

本文的設(shè)計(jì)中DAC芯片采用AD9739,所以需通過(guò)路數(shù)轉(zhuǎn)換模塊來(lái)將一路梳狀譜干擾信號(hào)轉(zhuǎn)換成8路在送到DAC進(jìn)行最后的梳狀譜干擾信號(hào)輸出。

2.1 相位控制字的產(chǎn)生

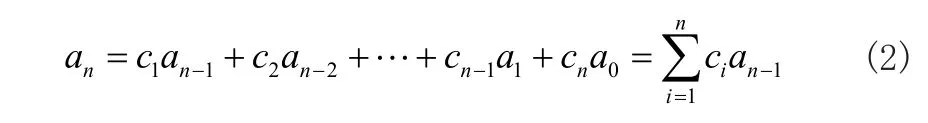

本文的梳狀譜干擾的隨機(jī)相位采用m序列為最常用的一種偽隨機(jī)序列, 是最長(zhǎng)線性反饋移位寄存器序列的簡(jiǎn)稱,也是由帶線性反饋的移位寄存器產(chǎn)生的序列, 并且具有最長(zhǎng)的周期。帶線性反饋邏輯的移位寄存器設(shè)定各級(jí)移位寄存器的初始狀態(tài)后, 在時(shí)鐘的觸發(fā)下, 每次移位后各級(jí)寄存器的狀態(tài)會(huì)發(fā)生變化, 觀察其中一級(jí)寄存器的輸出, 隨著移位節(jié)拍的推移會(huì)產(chǎn)生一個(gè)序列, 稱為移位寄存器序列。

假設(shè)n級(jí)移位寄存器的初始狀態(tài)為:a?1,a?2…a?n,經(jīng)過(guò)一個(gè)移位后,狀態(tài)變?yōu)閍0,a?1,a?2…a?n+1。經(jīng)過(guò)n次移位后,狀態(tài)為an?1,an?2…a1,a0,再一次移位時(shí)移位寄存器新得到的輸入an可以寫為

其中,ci的取值決定了移位寄存器的反饋連接和序列的結(jié)構(gòu),故ci是一個(gè)很重要的參量。用特征方程表示為

本文采用的M序列為FPGA生成的長(zhǎng)度為128的M序列,并將其存放在數(shù)組中。將M序列映射到控制字位寬上得到隨機(jī)相位控制字。

2.2 頻率控制字的產(chǎn)生

首先將中心頻率與帶寬映射映射到控制字位寬上變換為相應(yīng)的控制字,接下來(lái)用中心頻率控制字減去帶寬控制字的一半得到起始頻率控制字。再將帶寬控制字除以梳狀譜頻點(diǎn)數(shù),即把帶寬控制字進(jìn)行均分,將均分后的帶寬控制字分別與n(1≤n≤N,N為設(shè)定的梳狀譜頻點(diǎn)總數(shù))相乘并與起始頻率控制字求和得到最終的頻率控制字。

本文采用DDS核結(jié)合2.1及本小節(jié)產(chǎn)生的相位、頻率控制字來(lái)產(chǎn)生梳狀譜干擾信號(hào)。

2.3 使能控制模塊

設(shè)計(jì)思路是循環(huán)使用1個(gè)DDS產(chǎn)生所需頻點(diǎn)個(gè)數(shù)的信號(hào),因此需要控制DDS的工作,還需要將產(chǎn)生的每一路數(shù)據(jù)存儲(chǔ)在RAM,因此產(chǎn)生DDS和RAM的控制使能。

使能控制模塊中使用計(jì)數(shù)器區(qū)分所處的各個(gè)階段。首先,計(jì)算每個(gè)時(shí)間節(jié)點(diǎn)的計(jì)數(shù)器的值;第二步,根據(jù)這些節(jié)點(diǎn),在計(jì)數(shù)器計(jì)數(shù)中得到使能信號(hào);對(duì)DDS工作使能進(jìn)行處理,得到DDS剛開始工作的使能信號(hào)(1個(gè)時(shí)鐘周期的高電平)。

2.4 信號(hào)存儲(chǔ)求和模塊

先將第1個(gè)頻點(diǎn)產(chǎn)生的信號(hào)存儲(chǔ)到RAM中(邊生成邊存儲(chǔ)),等到第2個(gè)頻點(diǎn)產(chǎn)生的信號(hào)到來(lái)時(shí),將RAM中數(shù)據(jù)讀取出來(lái)和第2個(gè)頻點(diǎn)產(chǎn)生信號(hào)相加,并將結(jié)果存儲(chǔ)到RAM中,這樣存儲(chǔ)到RAM中的結(jié)果就是第1個(gè)頻點(diǎn)和第2個(gè)頻點(diǎn)信號(hào)的;循環(huán)操作,最終存儲(chǔ)到RAM中的數(shù)據(jù),就是N個(gè)頻點(diǎn)信號(hào)的和,即最終所需的梳狀譜干擾信號(hào)。本文設(shè)定梳狀譜頻點(diǎn)數(shù)為4點(diǎn)、8點(diǎn)、16點(diǎn)可調(diào)。

2.5 路數(shù)轉(zhuǎn)換模塊

首先,AD9739采集數(shù)據(jù)使用的是DDR模式,即使用數(shù)據(jù)輸入時(shí)鐘的上升沿和下降沿同時(shí)采集數(shù)據(jù),這樣數(shù)據(jù)時(shí)鐘的頻率是芯片時(shí)鐘的1/4。對(duì)于數(shù)據(jù)輸入來(lái)說(shuō),一片AD9739具有兩組差分輸入接口,而本文設(shè)計(jì)使用兩片AD9739分別用來(lái)輸出I、Q路信號(hào),故DAC共需8路輸入信號(hào)。在本文設(shè)計(jì)中,一路梳狀譜干擾信號(hào)在FPGA中是以150MHz時(shí)鐘生成的,而本文設(shè)計(jì)中配置的DAC芯片時(shí)鐘為1.2GHz,故DAC的數(shù)據(jù)輸入時(shí)鐘為300MHz。綜上,路數(shù)轉(zhuǎn)換模塊的個(gè)是將150MHz下生成的1路梳狀譜干擾信號(hào),處理為300MHz下的8路信號(hào),用以最后的輸出。處理方法為,首先將150MHz下的1路信號(hào),轉(zhuǎn)化為150MHz下的16路信號(hào),實(shí)現(xiàn)方法是:將信號(hào)每隔16個(gè)點(diǎn)存儲(chǔ)在一個(gè)RAM中,這樣16路信號(hào)就分別存在于16個(gè)RAM中了,然后同時(shí)從16個(gè)RAM中讀取這些信號(hào),就構(gòu)成了150Mhz×16路的信號(hào)。下一步,使用一個(gè)FIFO,將150MHz下16路信號(hào)轉(zhuǎn)化為300MHz下8路信號(hào),完成最終輸出。

3 測(cè)試結(jié)果

本文采用賽靈思公司的vivado平臺(tái)對(duì)干擾程序進(jìn)行事項(xiàng)。測(cè)試的方法是使用vivado中自帶的仿真軟件對(duì)干擾程序進(jìn)行仿真,將仿真得到的干擾信號(hào)時(shí)域數(shù)據(jù)導(dǎo)出并對(duì)其進(jìn)行頻域分析得到干擾信號(hào)的頻域數(shù)據(jù),最后將頻域數(shù)據(jù)繪圖得到干擾信號(hào)的頻域波形。

在仿真中中分別設(shè)置不同的干擾參數(shù)來(lái)生成梳狀譜干擾信號(hào)。

首先設(shè)置中心頻率為150MHz,帶寬40MHz,頻點(diǎn)數(shù)為4,頻域分析結(jié)果如圖2所示。

圖2 4頻點(diǎn)梳狀譜信號(hào)頻譜

接下來(lái)設(shè)置中心頻率為165MHz,帶寬80MHz,頻點(diǎn)數(shù)為8,頻域分析結(jié)果如圖3所示。

圖3 8頻點(diǎn)梳狀譜信號(hào)頻譜

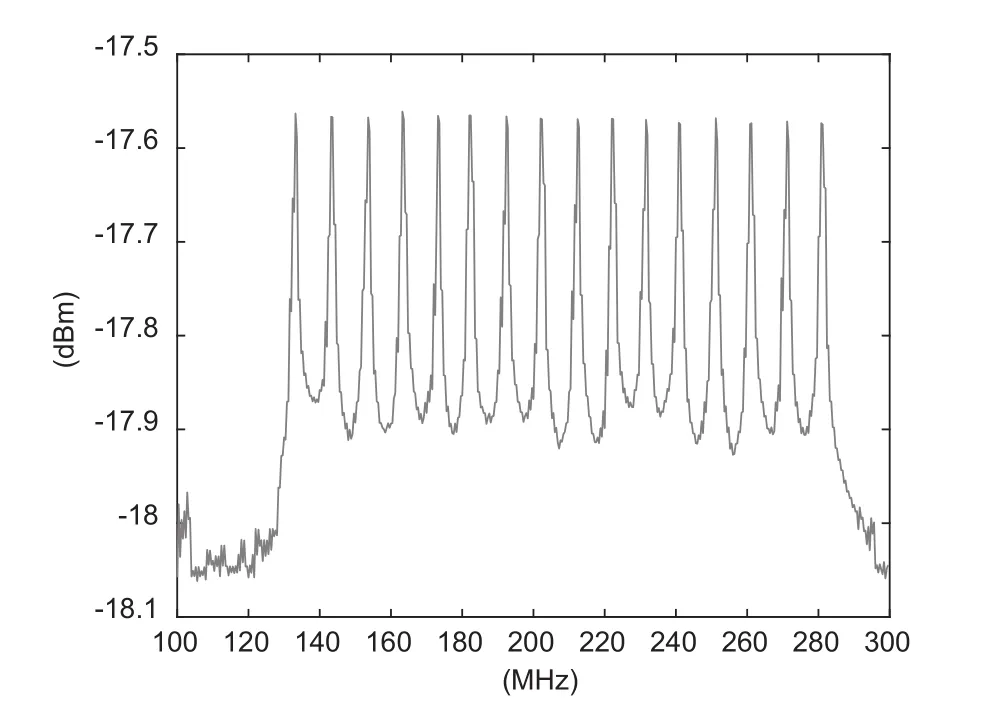

最后設(shè)置中心頻率為200MHz,帶寬160MHz,頻點(diǎn)數(shù)為16,頻域分析結(jié)果如圖4所示。

圖4 16頻點(diǎn)梳狀譜信號(hào)頻譜

4 結(jié)束語(yǔ)

本文提出一種基于FPGA的梳狀譜干擾信號(hào)實(shí)現(xiàn)方法,在FPGA中產(chǎn)生隨機(jī)相位控制字及頻率控制字,并由DDS核產(chǎn)生相應(yīng)的梳狀譜干擾信號(hào)。通過(guò)參數(shù)設(shè)置及控制相應(yīng)使能信號(hào),可以形成不同中心頻率、帶寬以及頻點(diǎn)數(shù)的梳狀譜干擾信號(hào),最終實(shí)現(xiàn)梳狀譜干擾。