基于FPGA并行+拆分查找表分布式高階FIR的設計與實現

柴乾隆

(航空工業蘭州萬里航空機電有限責任公司 航空機電研究院,甘肅 蘭州 730070)

濾波器主要用于頻率選擇和運算處理,以起到濾除噪聲和分離信號的作用。根據濾波器系統輸入、輸出信號的處理方式,可分為模擬濾波器和數字濾波器兩種。模擬濾波器在設計時可通過查詢大量圖表予以實現,簡捷明了,但因相位的非線性,其應用受到了很大的限制。而數字濾波器因其相位線性度高,幅度特性[1-3]任意可變,而被廣泛應用于語音和圖像處理、HDTV、模式識別、譜分析等領域。單位抽樣響應的長度直接影響著有限長單位沖激響應(Finite Impulse Response,FIR)數字濾波器的穩定性,當抽樣響應的長度有限時,系統的極點均在原點處,因此FIR濾波器是一個穩定的線性系統。同時,快速傅里葉變換(Fast Fourier Transfor,FFT)能夠在很大程度上提高FIR濾波器的運算速率[4],以有助于FIR濾波器對信號的有效過濾。

大多數傳統的FIR濾波器都是采用TI公司的TMS320CXX系列數字信號處理器(DSP)芯片[5]來實現系統設計。根據輸入序列的乘累加[6]編寫軟件,以硬件為平臺,結合軟件算法,實現濾波器的設計。但DSP芯片的馮·諾依曼體系架構使得數據的處理速度和容量都受到了限制,而FPGA因其豐富的連線資源和龐大的邏輯陣列,為實現并行度極高的FIR濾波器搭建了高效的運作平臺,同時具有優良的可擴展性。通過采用分布式算法,FIR濾波器可以克服濾波器階數對運算速率的影響,使兩者不呈正相關性。因此,分布式算法可廣泛應用于高階FIR濾波器的設計。

傳統分布式算法大多數采用串行處理輸入序列的數據,獲取輸出序列值。采用傳統分布式算法易于實現低階濾波器,而高階濾波器的實現則較為困難。目前,利用分布式算法實現的高階FIR濾波器,大多數都采用串行分布式結構、并行分布式結構或拆分查找表結構。3種分布式結構在存儲器占用和時鐘周期利用方面都各有優缺點,因此對3種結構的算法進行整合,可有效提高存儲占用和時鐘周期利用,有效化解了兩者之間的矛盾。

本文以國產FPGA為硬件平臺,綜合利用各算法的優勢,提出了一種基于FPGA并行+拆分查找表分布式結構高階FIR的設計與實現,以中國電科58所的JS1032系列FPGA為核心器件,利用100%國產化元器件搭建硬件電路,比較研究了3種分布式算法,對FIR濾波器進行了硬件實現和軟件仿真,同時利用惠普網絡分析儀對所設計的FIR濾波器進行了幅頻特性的測試,驗證了該算法的有效性和實時性。

1 FIR濾波器傳統算法及其改進

1.1 FIR濾波器概念與方法介紹

線性時不變性[7]是FIR濾波器最大的系統特征,N階FIR數字濾波器的輸入序列x(n)與單位沖激響應h(n)經卷積運算可得輸出序列y(n):

(1)

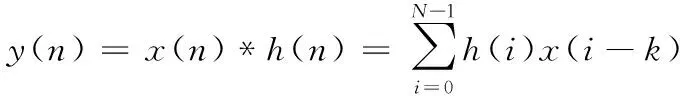

FIR濾波器典型的設計結構主要由延時單元、乘法器、抽頭系數、加法器等部分組成,FIR濾波器典型的設計結構如圖1所示。輸入樣本x(n)通過緩沖區實現Z-1延時,并在數據寄存器中,開設n個用于存放最新輸入樣本的滑窗。最新的數據采樣乘以抽頭系數,得到的乘積再與上一次的加法器結果進行求和,依次遞進運算,改變抽頭數目和抽頭系數可獲得不同幅頻特性的FIR濾波器。

圖1 FIR濾波器典型的設計結構

龐大的乘法和加法運算非常消耗FPGA的資源,同時FPGA的設計效率和邏輯單元的占用量都非常高,因而使用傳統方法實現FIR濾波器,濾波器的階數很難提高,因此必須對經典實現方法進行優化改進。

1.2 分布式算法

分布式算法[8]是Croisier于1973年提出的,但由于計算資源的客觀限制,發展較為緩慢,直到FPGA的出現,才使得分布式算法得到了廣泛應用。

分布式算法通過將n個數據的相同序號的位在移位寄存器中進行操作,在查找表中獲取相應的部分積,然后通過二次冪加權對已獲取的部分積進行累加,完成加法運算后,獲得最終結果。而傳統經典算法的乘法運算和加法運算是分離的,是在完成所有乘積之后,再對乘積結果進行累加。分布式算法與傳統算法相比,實現濾波器設計的硬件電路規模大為減小,并以流水線式的處理模式,使得計算速度大幅提高。FPGA因其能高速完成移位和加法運算使得分布式算法的應用更為廣泛[9],也拓寬了FPGA芯片的應用領域。為了便于分析,將濾波器輸出序列的表達式改為

(2)

假設h(n)均為常數,x(n)是變量,無符號數x(n)的表達式為

(3)

式中,n為第n個采樣值;b為x(n)的第b位。則y(n)可以表示為

(4)

變換求和次序,重新求和得:

y(n)=h(0)[xB-1(0)×2B-1+xB-2(0)×2B-2+

x0(0)×20]+h(1)[xB-1(1)×2B-1+xB-2(1)×2B-2+

x0(1)×20]+…+h(N-1)[xB-1(N-1)×2B-1+

xB-2(N-1)×2B-2+x0(N-1)×20]

=h(0)xB-1(0)+h(1)xB-1(1)+…+

h(N-1)xB-1(N-1)]2B-1+…+[h(0)x0(0)+

h(1)x0(1)+…+h(N-1)x0(N-1)]20

(5)

化簡成如下形式:

(6)

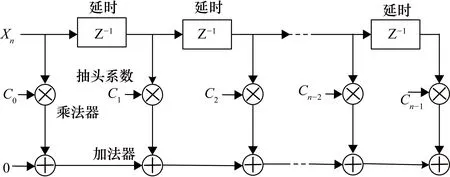

式中,xb(n)為第n個數據的第b位。x(n)為取值[0,1]的有限位數據。分布式算法的原理框圖如圖2所示。

圖2 分布式算法原理框圖

求得濾波器系數后,根據濾波器輸入數據位寬,對系數進行合適的放大,在實現過程中對累加值進行右移,得到系統的輸出結果。

1.3 并行+拆分查找表分布式結構

分布式算法以序列運算處理的方式劃分,可分為串行分布式結構、并行分布式結構和拆分查找表結構。

串行分布式結構需要大量的ROM進行尋址,同時一次運算需要多個時鐘周期,使得成本和存儲時間都急劇增加。當FIR濾波器的階數很高時,使用串行分布式結構很難實現。例如,設計一個階數為64、位寬12的FIR濾波器,需要12×264bit的存儲空間,而FPGA根本沒法提供高達12 Gbit的內部存儲空間。

拆分查找表結構相較串行分布式結構而言,很大程度上減小了存儲器的數量,但拆分查找表結構和串行分布式結構同樣需要很多個時鐘周期來實現乘加運算。輸入數據的位寬決定了串行分布式結構和拆分查找表結構兩種算法實現FIR濾波器輸出速率的快慢,每輸入一個數據,輸出一定要延遲相應位寬個數的周期,才能輸出一個數據,極大地影響了數據處理速度。

并行分布式結構在同一周期內同時尋址已存入ROM表的輸入數據,占用的存儲器資源也較多,但與串行分布式結構相比較,其占用的存儲器資源個數少之又少,同時在處理高速信號時,并行分布式結構以其較高的數據吞吐率顯現出很大的優勢。

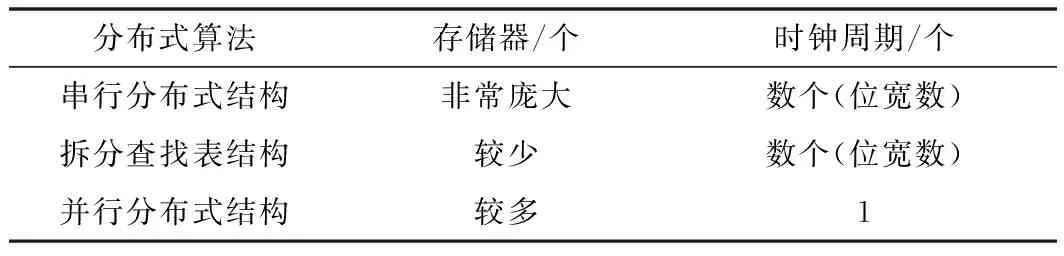

根據以上對3種分布式算法優缺點的分析說明,串行分布式結構、拆分查找表結構和并行分布式結構在占用存儲器資源和時鐘周期方面的對比如表1所示。

表1 3種分布式算法的對比

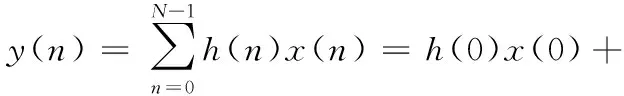

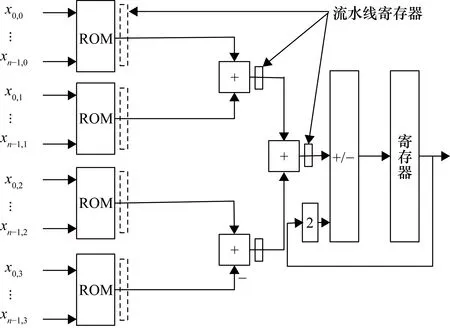

為了克服3種分布式結構在存儲器占用和時鐘周期利用方面的矛盾,對并行結構和拆分查找表結構進行了整合,使得輸入數據在同一周期同時進行取值,提高運算速率,并將查找表拆分成若干個小的查找表,減小存儲器的占用,提出并行+拆分查找表結構的分布式算法。并行+拆分查找表分布式結構如圖3所示。下面舉例說明并行+拆分查找表結構的分布式算法在計算規模和時鐘周期數兩個方面的優勢。例如本文256階的FIR濾波器使用傳統模式查找表,位寬達2256,通過拆分查找表,其規模可降為16×216=1048576,并在一周期內對輸入數據同時進行尋址,一方面提升了系統的運算效率,另一方面減小了系統的設計規模。

圖3 并行+拆分查找表分布式結構

2 并行+拆分查找表分布式算法的實現

2.1 硬件設計

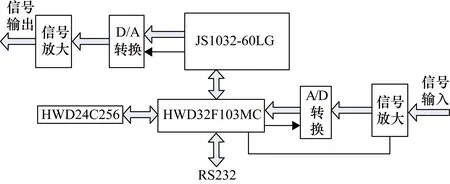

FIR濾波器的實現需建立在一定的硬件平臺基礎上,其硬件電路系統框圖如圖4所示。在本文的硬件電路中,時序信號和控制信號是由FPGA來完成,同時FPGA處理FIR濾波器系統的輸入數據,是實現系統要求的核心器件。FPGA的配置是通過STM32來完成的。每次系統通電后,STM32將事先存入到只讀存儲器HWD24C256中的配置文件下載到FPGA 中,下載完畢后,FPGA便開始工作。若需要修改濾波器的參數,只需存入不同的配置文件,而無須改動硬件電路,增強了硬件電路的通用性。采用STM32芯片自身的A/D口,其轉化精度為12位,分辨率高,轉換速率最大可達1 MHz。

圖4 硬件電路系統框圖

信號輸入后,根據信號幅度的控制要求,對信號進行適應性放大,并傳輸給A/D轉換器進行采樣轉換,之后送到FPGA進行運算處理;FPGA完成對數據的處理之后,將結果進行D/A變換,轉換成模擬信號后,再經過運放調整,最后輸出系統信號。

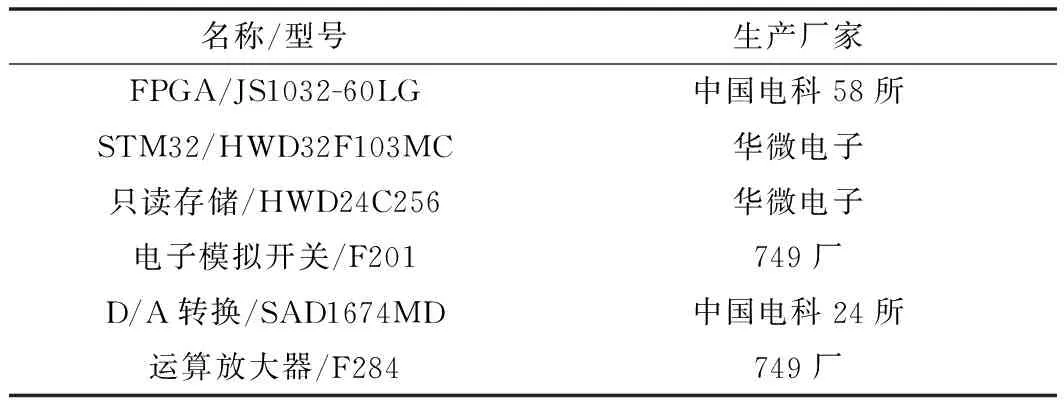

因美國對華大規模的芯片禁購,很多進口原器件已無法使用。本系統所選器件均為國產,元器件國產化數量比、規格比、費用比均為100%,系統主要元器件如表2所示。

表2 主要元器件表

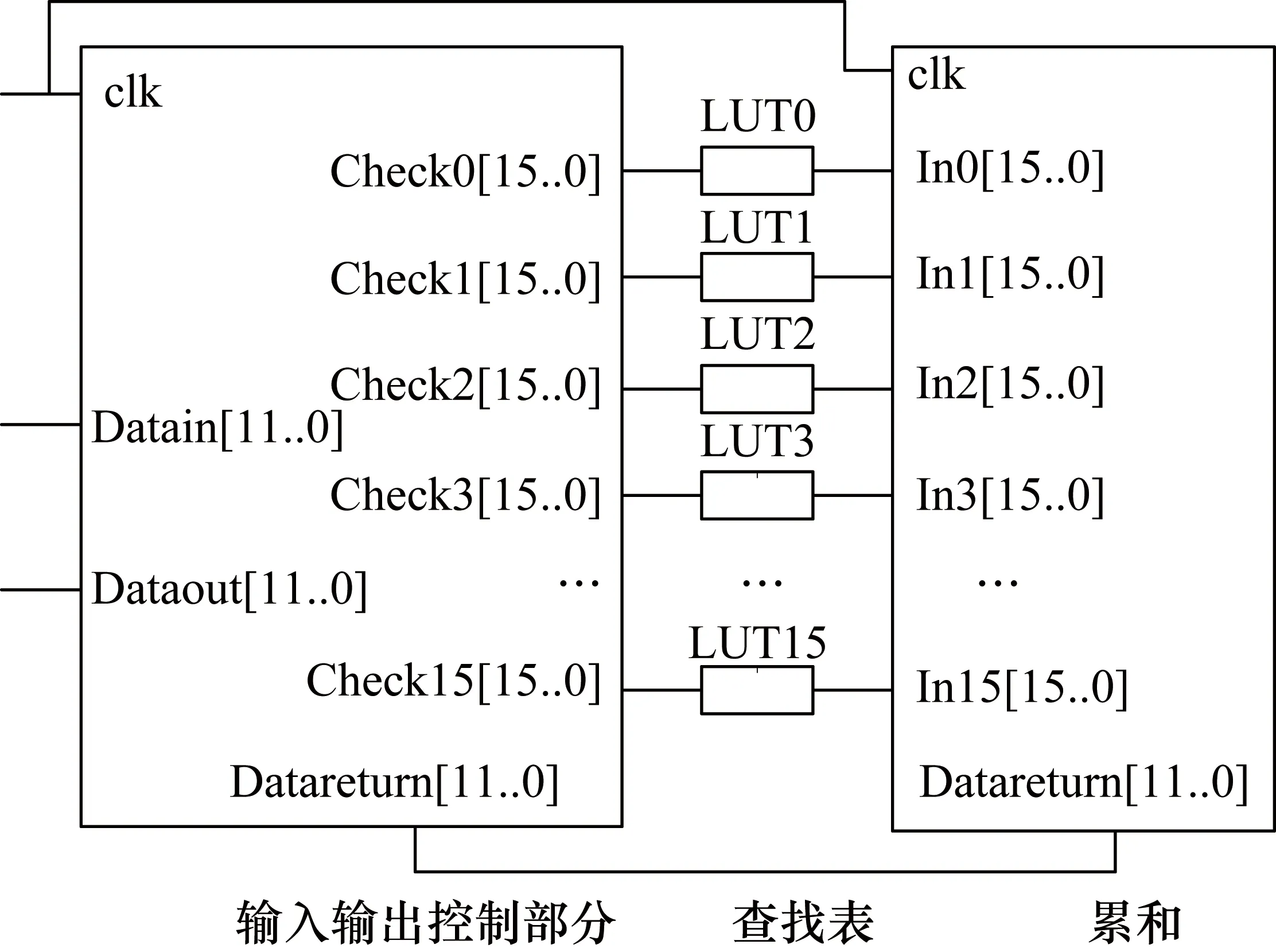

2.2 FPGA程序架構

并行+拆分查找表分布式算法在FPGA上的實現基本可以劃分為三大功能模塊:輸入輸出控制部分、查找表(Look-Up-Table)部分和累和部分。FPGA程序的系統架構如圖5所示。

圖5 FPGA程序的系統架構

其中,輸入輸出控制部分負責完成系統數據的采集并將濾波運算處理的數據輸出給后級數模轉換電路;查找表(Look-Up-Table)部分用于獲取計算輸出序列過程中的部分積;累和部分是對通過查找表所得的部分積進行加法運算。完成以上三部分的內容后,即可進行后續電路的處理,最終得到系統的輸出信號。

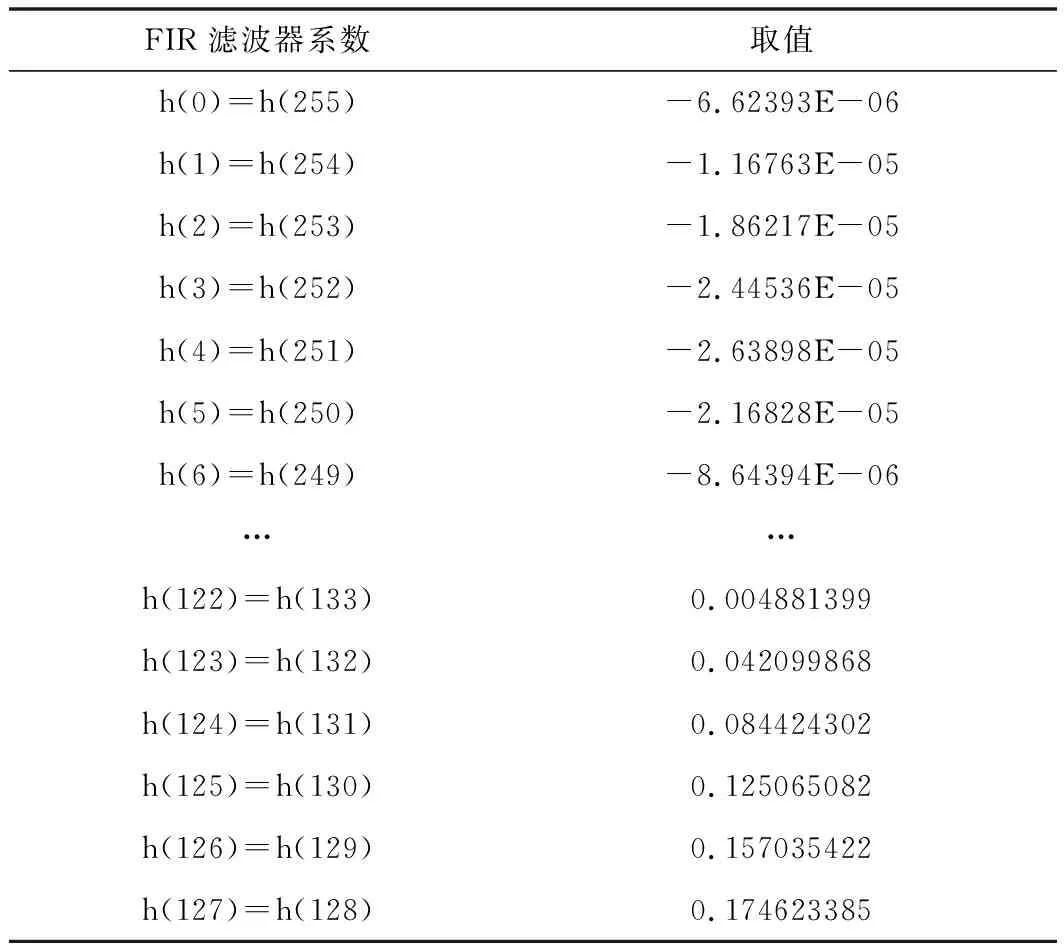

2.3 確定濾波器系數

利用Matlab軟件中的可視化仿真工具Simulink可以求得FIR濾波器的抽頭系數[10],本文FIR濾波器所需系數如表3所示。因FPGA只能處理定點數的乘法,而Matlab生成的系數是分布在[-1,1]區間的浮點數,因此需要將所得的濾波器系數同乘以1024,才能在FPGA中參與運算處理。

表3 FIR濾波器系數

2.4 輸入與輸出

輸入輸出控制部分主要用于模擬信號的采集,完成運算處理后,輸出處理信號用于后級進行D/A轉換。另一方面,系統所需的時序信號也是由輸入輸出控制部分來實現的,通過時序控制輸入數據,依次存入數據緩存區,以待進行查表。

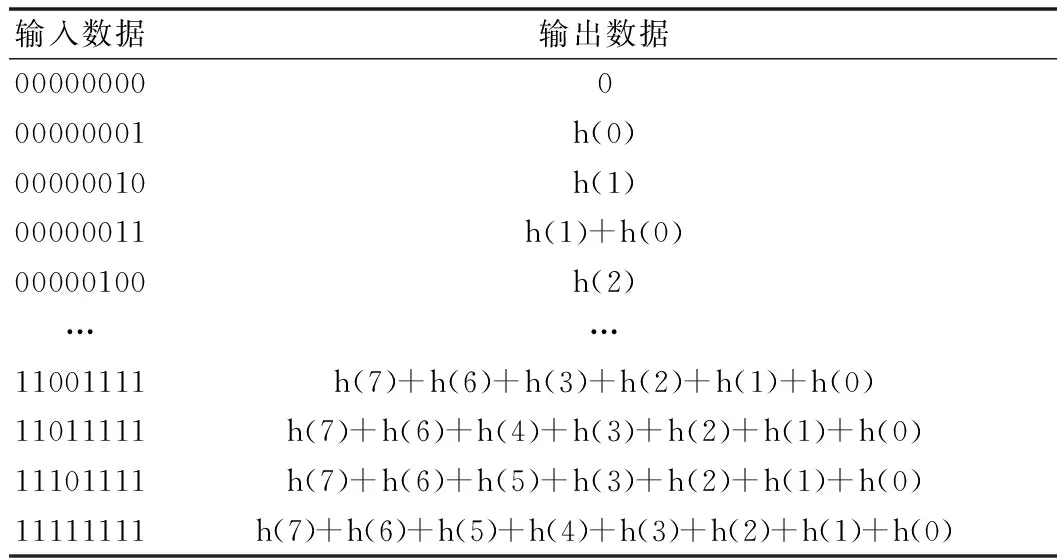

2.5 查找表(Look-Up-Table)

查找表部分主要用于對處理后的輸入數據通過查表快速獲得部分積結果。其中一個查找表的具體內容如表4所示,其他查找表可根據表4同理推出。

2.6 累和

累和部分對通過查找表獲得的部分積進行相加,相加時一定要根據式(6)進行二次冪加權,才能得到系統的內積結果y(n)。獲取內積y(n)后,就可以輸出到后級電路進行D/A轉換,進一步獲取系統輸出信號。

表4 查找表

3 FIR濾波器的理論仿真

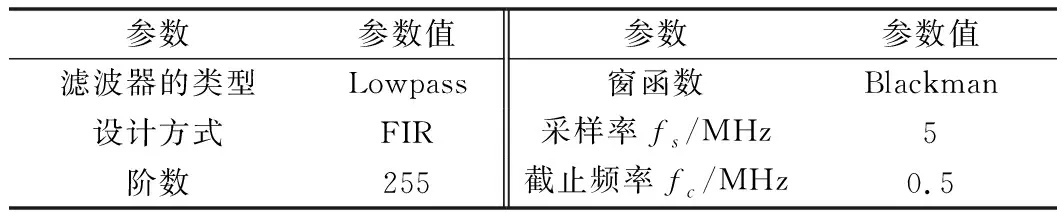

FDATOOL[11](Filter Design & Analysis Tool)是Matlab軟件的Simulink中各種濾波器的專用設計與分析工具。FDATOOL可以設計實現各種常規濾波器,并可將各種算法體現在設計過程中。FDATOOL操作簡單,方便靈活。在使用FDATOOL工具設計FIR濾波器時,濾波器類型、階數、截止頻率、窗函數的選擇是其關鍵所在。其中,窗函數可根據設計需求實現對信號的截斷,減少系統能量的泄露,其中Hamming窗、Blackman窗和Hanning窗最為常見。本文FIR濾波器在FDATOOL中的設計參數如表5所示。

表5 參數表

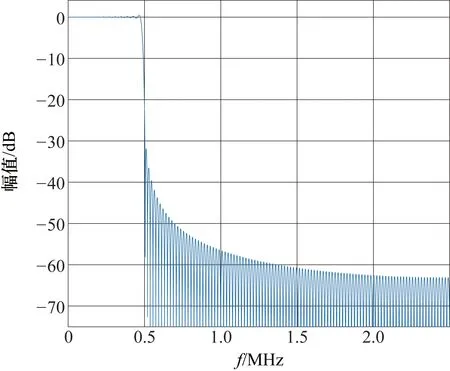

本設計中FIR濾波器的輸入數據為12位有符號二進制數,在Matlab中利用Blackman窗計算FIR濾波器的濾波系數,設置采樣率和截止頻率分別為5 MHz和0.5 MHz。根據既定參數要求,通過Matlab的理論仿真,實現所需的高階FIR濾波器,其幅頻特性如圖6所示。

圖6 幅頻特性(Matlab)

4 實測結果

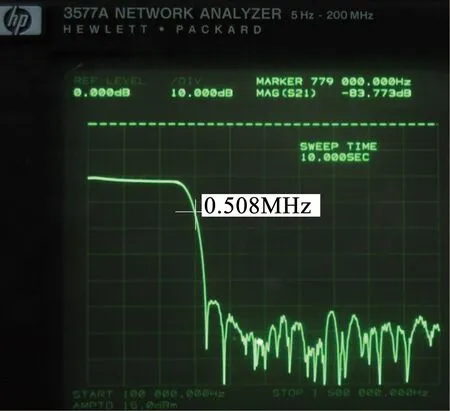

采用中國電科58所JS1032系列FPGA器件,在QuartusⅡ開發軟件下完成并行+拆分查找表分布式FIR濾波器的仿真,其過程包括軟件編程、程序的編譯、調試,并利用網絡分析儀HP3577A對FIR濾波器進行幅頻特性的測試。網絡分析儀測試所得的幅頻特性如圖7所示,可知高階FIR濾波器的截止頻率為0.508 MHz,與原定的設計要求0.5 MHz相比,誤差很小。通過比較Matlab理論仿真與硬件電路實現的結果可知,利用硬件所設計的高階FIR濾波器的幅頻響應與Matlab理論仿真的結果高度吻合,誤差僅為0.008 MHz。

圖7 幅頻特性(網絡分析儀)

5 結束語

由于FIR濾波器傳統實現方法存在局限性,通過對3種分布式算法進行比較,提出了一種基于FPGA并行+拆分查找表分布式結構高階FIR濾波器的實現方法,并且利用中國電科58所JS1032系列FPGA及其他所選國產元器件設計實現了高階FIR濾波器的硬件電路。通過軟件Matlab仿真和硬件實測,表明基于FPGA并行+拆分查找表分布式結構實現的高階FIR濾波器誤差極小,運算速率快,硬件資源占用少,并可根據實際情況調整FIR濾波器的階數,可使其廣泛應用于很多領域。