雷達自適應副瓣對消的FPGA工程實現

王佳鑫

(中國電子科技集團公司 第二十研究所,陜西 西安 710068)

0 引 言

隨著雷達干擾手段的不斷增強,抗干擾能力已經成為重要的雷達技術指標,根據不同雷達分機(天線、發射機、接收機或信號處理等)可采取不同的抗干擾策略[1]。與天線有關的抗干擾技術可分為兩類,一類是盡量避免或減少干擾進入接收機,另一類則是通過對干擾信號的特性進行對應的處理。通常一部分雷達會應用多種抗干擾技術,如使用低副瓣天線降低干擾信號進入,同時通過副瓣消隱(Sidelobe Blanking,SLB)、副瓣對消(Sidelobe cancellation,SLC)、脈沖壓縮以及頻率捷變等去除干擾信號,提取目標。自適應旁瓣對消是通過設計輔助天線陣列采集干擾信號,并與主陣面信號進行計算來實現干擾抑制[2]。

工程實現中,雷達信號處理需要大量的復數和浮點運算,傳統硬件多采用數字信號處理器(Digital Signal Processing,DSP)作為主要處理單元,FPGA作為數據緩存和傳輸接口單元。隨著FPGA性能大幅提升,很多信號處理功能都可由FPGA單獨完成,節省了芯片間數據傳輸的時間,特別在雷達周期小的應用場景中其穩定的時效性具有明顯的優勢。

本文介紹了自適應副瓣對消原理,并根據FPGA計算和IP核特點對公式進行推演,提高處理效率。同時在某型相控陣雷達中進行測試,對比不同測試條件下副瓣對消的結果,給出具體應用的建議。

1 副瓣對消原理

自適應副瓣對消的基本原理是通過輔助天線陣列接收干擾信號,自適應計算干擾的方向和功率,隨后調整天線接收方向圖,將零點置于干擾方向上[2]。輔助陣列可以是獨立的接收天線,也可以是主天線的部分接收單元,但要求輔助陣的方向圖主瓣盡可能寬,幅度應該略大于主天線的第一副瓣,從而獲得更好的干擾抑制效果。圖1是典型的自適應副瓣對消系統原理框圖。

圖1 副瓣對消工作原理框圖

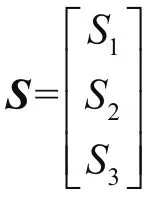

n為輔助天線個數,輔助天線接收到干擾信號和主天線的信號線性組合進行對消,問題是需要尋找到一組合適的權值Wn=[W1,W2,…,WN]來最大限度的對消干擾。由于干擾信號的隨機性以及假設信號為線性組合,采用隨機過程線性預測理論進行分析[1,2]。輔助天線陣列可以用N維矢量Xn=[X1,X2,…,XN]表示。那么干擾信號樣本組可由協方差矩陣M=E[Xn*XnT]表示,主天線信號X與Xn的關系通過協方差矢量S=E[XXn*]表示。最優權值W應使得均方預測誤差為最小的準則確定,即:

式中,Z是系統輸出,使PZ最小時可得到:

式中,μ是任意常量。最終SLC的輸出為:

2 FPGA算法實現

副瓣對消的難點在于求解式(2)的權值時需要實時計算N階矩陣M和S,包含了大量的復數乘法和矩陣轉置求逆等計算,且輔助陣列數N和采樣點數K越大,計算復雜度越高,耗時越長。本文提出的FPGA解決方案在某型有源相控陣雷達中得到了測試和驗證。此雷達主天線有128個T/R組件,通過饋電網絡合成主天線波束。主天線上方設置有3個輔助天線,用于副瓣對消。

2.1 SLC工作流程

副瓣對消的工作流程可分為干擾采樣、計算權值以及加權輸出3個階段。為了獲得穩定天線指向的干擾信號,并盡可能減少自身雷達發射信號產生的強回波對權值計算的影響,干擾采樣時間應該在天線陣面完成布相之后和發射期開始之前。干擾采樣接收完成后立即啟動權值計算,并且在接收期開始前完成,以確保實時地對回波信號加權輸出副瓣對消結果。SLC工作時序如圖2所示。

圖2 SLC工作時序圖

在一個相控陣雷達工作周期T內,天線布相完成,主陣面和輔助陣列的指向穩定后,打開接收機,AD采樣模塊開始對干擾信號進行采樣,經下變頻和抽取得到4路各100點的干擾信號,送入SLC模塊進行權值計算。利用雷達發射期計算權值,并且在接收期到來之前完成計算,隨后在接收期回波采樣時通過式(3)實時加權輸出對消結果。

根據雷達時序設計的不同,留給權值計算的時間可能很短,在設備硬件條件允許的情況下,副瓣對消可直接在接收機的FPGA中進行,AD采樣和下變頻完成后直接進行計算,減少板間數據傳輸時間,提高效率。本文方案由于主陣與輔陣的AD采樣不在同一硬件模塊,故通過高速串口發送給信號預處理模塊進行權值計算和加權輸出。

2.2 SLC權值計算

在FPGA中計算式(2)實現矩陣運算較為復雜,那么輔助天線通道的協方差矩陣M可寫為:

主天線通道與輔助天線通道的互相關矩陣記為:

矩陣求逆最終可轉化為行列式求解問題,且不同行列式是由多個基礎協方差以不同的排列組合構成的,所以只需要運用復數乘法器和累加運算,再通過邏輯時序實現行列式計算得到權值。

第一步,接收干擾信號,存入雙口RAM,接收完成后啟動多個復數乘法器同時計算SiMij(i,j=1、2、3)。

第二步,利用行列式計算公式,復用上一步的復數乘法器計算行列式結果,即得到|S1M|、|S2M|、|S3M|以及|M|的數值,結果為復數。

第三步,將式(6)中的復數除法轉換為復數乘法得到權值W。在雷達接收期,使用3個復數乘法器對回波信號進行流處理,實時輸出副瓣對消結果Z=X-W1X1-W2X2-W3X3。

需要注意的是在副瓣對消時,主瓣回波也會同時對消,為了不減少主瓣增益以保留小目標信號,可以進行主瓣保護。本文利用主天線和輔助天線的方向圖特性做了簡單的主瓣保護,利用干擾采樣數據計算主天線和輔助天線的回波功率,若主天線功率大于輔助天線說明此時天線指向的干擾從天線主瓣進入,不進行對消。反之干擾從天線副瓣進入,進行對消。

根據分析,FPGA性能需求主要在復數運算和邏輯時序控制上,存儲空間需求不大。本文采用Xilinx Kintex系列FPGA,型號為XC7K420T、Logic Cells 416960、DSP Slices 1680以及Block RAM Blocks 30060kb。使用復數乘法器IP核(Complex Multiplier 6.0),選擇Mults構建方式,通過DSP Slices(一個乘法器占用3~4個Slices)實現更高工作頻率下的復數乘法,輸出延時4~6 h。實現3個輔助陣面的副瓣對消運算只需要5%~10%的DSP Slices資源。本文計算方法在FPGA全部使用整型計算,復數乘法之后會有溢出現象。因此在每級的復數乘法器后擴大輸出寄存器位數,并在最終權值計算完成后進行截位,以獲得更高的精度[3]。

3 試驗結果

影響副瓣對消效果的因素包括干擾源數R、輔助陣列數n、干擾采樣數K以及通道相位一致性等,但根據仿真分析整體系統副瓣對消改善因子應不小于25 dB。在某型相控陣雷達的試驗中,使用遠場測試天線方向圖的方法進行測試,在天線法相方位1 km外架設信號源輻射喇叭,天線伺服角度不變,操控天線進行方位電掃,使信號源輻射進入天線主副瓣。經過AD采樣,下變頻,抽取后求得各指向角度上的平均功率而獲得一個“等效方向圖”[4]。試驗使用1個干擾源(R=1),分別對輔助陣列數(n=1,2,3)和干擾采樣點數(K∈[10,100])的對消效果比對,如圖3所示。

圖3 不同K、N值下副瓣對消結果

從圖3可以看出對消增益隨著采樣點數的增多而增大,但在大于20點的增幅有限,對消增益基本可以保證在30 dB以上。小于20點的對消增益下降較多,并且對消后方向圖不平滑,起伏較大。同時,當輔助陣列數等于干擾數時,對消增益不如陣列數大于干擾數的結果。并且陣列數越大,對消增益越大,方向圖越平滑。副瓣對消計算量對比如圖4所示。

圖4 副瓣對消計算量對比

權值計算耗時主要與采樣點數和輔助陣數量有關,在100 MHz的FPGA工作時鐘下,計算3個陣面100點干擾采樣需要大約3.75 μs,可以滿足高重頻下的副瓣對消。根據測試結果,對于干擾源較少,在選擇干擾點數大于等于20,輔助陣數大于等于2時,副瓣對消的效果基本滿足,再增加點數和陣列對結果增益幫助不大。若干擾源較多,可通過增加輔助陣列來提高對消效果,但同時也增加了計算時間。

4 結 論

介紹自適應副瓣對消的原理以及在FPGA中的實現方法,通過試驗驗證了此方法的可靠性和實時性,比較了在不同輔助陣面數和干擾采樣數的副瓣對消結果,均滿足雷達抗干擾要求,同時給出了在FPGA中實現算法的建議。