基于FPGA+ARM的多路光柵數據采集系統設計

張立,李少康,李高益

(西安工業大學,陜西西安,710021)

0 引言

光柵編碼器作為一種重要的高精度位移測量器件,常用于運動伺服系統中,實現對運動位置的精確反饋[1]。隨著光柵編碼器研制技術的發展,其測量精度、速度以及輸出信號帶寬也越來越高,因此,相應的對光柵信號采集及傳輸系統提出了更高的要求,要求采集系統具備采集速率高,傳輸速度快,抗干擾能力強等特點[2]。

傳統的光柵數據采集系統多采用單片機或者專用的采集芯片作為處理器,存在采集速率低和靈活性較差的缺點[3]。在信號傳輸上多采用RS232、RS485或CAN等傳輸方式,存在傳輸速度低的缺點,并且目前電腦已經逐步淘汰這些接口,給測控系統設計及使用帶來較大障礙[4]。隨著“工業4.0”及“互聯網+”的發展,對數據的通信傳輸要求智能化和遠程化[5]。本文提出了一種基于FPGA+ARM的光柵信號采集及傳輸系統,充分發揮了FPGA的并行邏輯控制能力和ARM的數據處理能力,以TCP/IP協議完成了對數據的高速穩定傳輸,使得測控系統接口統一化,實現對數據的遠端測控,具有采集速度快、帶寬高、傳輸速度快和穩定等優點,可以完成對光柵數據高速的采集、處理和傳輸。

1 系統整體結構

基于FPGA+ARM的多路光柵數據采集系統的整體結構如圖1所示。多路光柵的輸出信號經過差分轉換及隔離電路后進入FPGA中,FPGA對多路光柵數據進行數字濾波、同步采集以及數據存儲后通過FSMC總線與ARM端進行數據通信,ARM端再以TCP/IP協議以網口的形式將數據發送至上位機。

圖1 系統的整體結構

2 系統硬件電路設計

2.1 光柵信號預處理電路

光柵信號輸出為RS422差分信號,輸出高電平為5V,FPGA為低電壓邏輯電平,高電平為3.3V,為了便于FPGA對信號進行采集,需要設計相應的信號調理轉換電路將5V的RS422差分信號轉化為LVTTL電平信號。本次設計采用AM26LS32差分接收芯片,實現對測頭差分信號到單端信號的轉換,對信號采用了TLP2362型高速光電耦合器,降低了信號的噪聲干擾的同時實現了邏輯電平的兼容。

2.2 FPGA+ARM設計

FPGA具有高度并行數據處理能力,可以很好的保證對多路光柵數據采集的并行性和實時性,ARM具有強大的數據處理以及靈活的進程運行能力[6]。結合FPGA和ARM的優勢,設計FPGA+ARM的數據采集系統結構,ARM作為主處理器,讀取FPGA采集到的多路光柵數據,通過對LwIP協議棧移植,控制以太網實現數據到PC端上位機的傳輸[7]。FPGA主要負責多路數據的實時采集,將采集數據進行臨時存儲,與ARM進行數據傳輸。

FPGA芯片選用Altera公司的EP4CE22C8芯片,其擁有6272個邏輯單元完全滿足本系統的設計。ARM處理器選用ST公司生產的高性能ARMCortex-M4,其擁有1MB Flash,最高主頻可達到168MHz,并且支持以太網通信。

FPGA和ARM之間通過FSMC總線連接,如圖2所示。FSMC總線接口由16位數據總線、16位地址總線及其它FSMC總線端口。

圖2 STM32與FPGA接口模塊

2.3 網絡接口設計

STM32F407自帶以太網模塊,只需外界PHY芯片即可完成以太網通信實現10M/100Mbit/s的數據傳輸速率,STM32與外部PHY芯片使用RMII接口進行連接,本次設計使用LAN8720A作為PHY芯片。以太網連接器采用HR911105A,其內部集成網絡變壓器,以太網通信電路原理圖如圖3所示。

圖3 以太網通信電路

3 系統的軟件設計

系統的軟件設計主要包括FPGA端對光柵信號采集程序、ARM端數據處理、以太網通信程序以及PC端上位機軟件部分的設計。

3.1 濾波程序設計

光柵的輸出信號可能存在噪聲干擾,需要對毛刺進行濾除,基本思想是在系統時鐘的上升沿對光柵信號進行采樣,穩定的光柵信號在幾個系統時鐘信號邊沿采樣時都維持電平穩定,否則為毛刺信號[8]。圖4所示為兩路光柵信號濾波模塊的RTL圖,A、B信號經過w個觸發器后,如果w個觸發器的每一位輸出均為1時才輸出1,每一位都為0時才輸出0,否則維持上一時鐘信號的采樣值。這樣小于w個時鐘周期寬度的毛刺信號將被濾除。

圖4 光柵信號濾波RTL圖

3.2 光柵信號計數處理程序

光柵在移動過程中,輸出相位相差90°的兩路方波信號A和B,若正方向移動,A超前B信號90°相位,若反方向移動,A滯后B信號90°相位,因此,根據兩信號的相位關系即可確定出光柵尺的位移方向[9]。根據對A、B信號的相位關系進行分析,得出如圖5所示的狀態變化及計數操作關系,當A、B兩信號的電平狀態相對變化為00→10→11→01→00中的一種時,計數器執行加1操作,當電平狀態相對變化為00→01→11→10→00中的一種時,計數器執行減1操作[10]。以此便可實現對光柵信號的四倍頻辨向計數。

圖5 計數操作圖

3.3 以太網通信設計

針對于STM32F407微處理器,選擇輕量級的LwIP作為以太網協議棧,將LwIPTCP/IP協議棧移植在STM32F407上,在應用層實現網絡雙向傳輸的數據傳輸系統。以太網通信函數圖如圖6所示,調用ETH_BSP_Config()和LwIP_Init()用于PHY芯片配置和初始化LwIP協議棧,設置完IP地址、子網掩碼和網關后使用TCP_Client_Init()初始化TCP客戶端,之后便可以進行數據發送與接收。

圖6 以太網通信函數框圖

3.4 上位機軟件設計

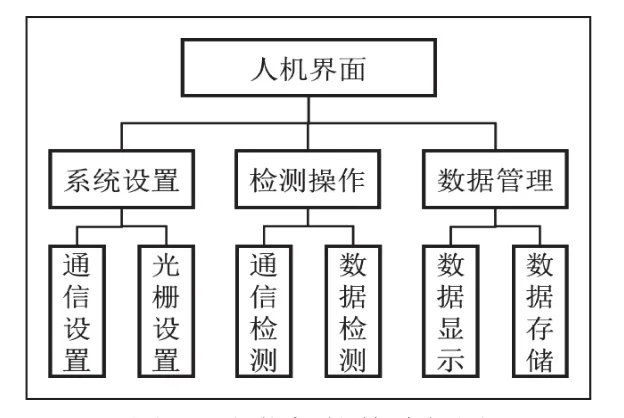

光柵數據采集系統的上位機軟件使用VS2019進行軟件編程,整個上位機功能主要由系統設置、檢測操作和數據管理組成,上位機軟件功能圖如圖7所示。

圖7 上位機軟件功能圖

所設計程序程序界面如圖8所示,在系統設置區對通信以及光柵參數進行設置,上位機與下位機連接成功后在數據接收區即可對各光柵進行置數,并采樣到光柵當前的位移及速度,消息區顯示工作狀態及相應警告。

圖8 上位機系統界面圖

4 實驗驗證

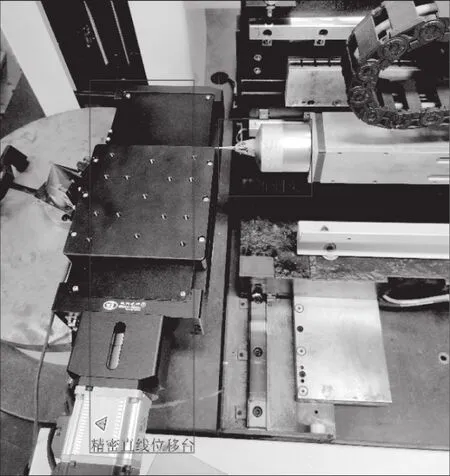

本次設計以安裝有RSF公司生產的AKMS15TTL×100型號光柵的直線位移臺為實驗對象,其脈沖當量為0.1,采用設計的光柵信號采集系統進行數據采集傳輸,搭建如圖9所示實驗平臺,將位移臺固定在C40測量機平臺上,使用C40測量機對位移臺的實際位移進行測量,在上位機中監測所設計的多路光柵數據采集系統采集到的位移臺的光柵數據。

圖9 光柵采集系統實驗圖

通過對比上位機數據與C40測量機采集到的位移數據,二者差值如圖10所示。

圖10 測量數據差值

由圖中可得,二者誤差最大值發生在第10個點,差值為0.5,由于測量機存在一定的測量誤差,可以認為設計的光柵數據采集系統測量結果準確無誤。

5 結論

本文設計了一種基于FPGA+ARM的光柵數據采集系統,實現對多路光柵數據的高速采集與傳輸,具有采樣速率高,傳輸速度快,抗干擾性強等優點。通過ARM端對以太網協議棧的移植,實現了高速穩定的以太網通信,實現了整個系統的以太網遠程控制,解決了以往光柵采集系統通信速度以及與PC端互聯通用性方面的不足。