一種基于國產圖形處理器的視頻疊加顯示系統設計

李宇

(中國船舶重工集團公司第七一六研究所 江蘇省連云港市 222061)

1 概述

在工程應用中,為了快速全面地給指揮人員提供信息,需要將雷達和電視視頻進行實時處理,與計算機生成的圖形按照一定的層次疊加顯示在同一個屏幕的不同窗口中,通過數據整合的方式獲得更加全面、精確的信息[1]。以往多采用的DSP 和FPGA 結合的實現方式結構較為復雜,不利于未來的系統升級和移植,為滿足未來更高效、小型化的系統需求,本文針對視頻疊加顯示系統開展了進一步研究。

近年來國產圖形處理器發展迅速,其應用由單純的圖形圖像處理逐步向并行計算、信號處理、VR 顯示、AI 計算等方向發展,并在雷達探測、光電探測、云計算、人工智能等多個領域開始得到應用[2]。本交充分利用了國產圖形處理器JARI G12 的優勢,基于該圖形處理器的特點設計一種視頻疊加顯示系統,兼顧高效性、實時性和小型化,為視頻疊加顯示處理提供了一種新的硬件設計方案,擴展了國產圖形處理器的應用方向。

2 視頻疊加顯示系統設計

2.1 方案設計

JARI G12 是一款國產圖形處理器[3],支持4 個獨立的顯示控制接口單元,每個顯示控制接口單元都支持圖形視頻的疊加顯示。同時JARI G12 提供了4 路獨立的數字視頻輸入端口,支持視頻的高效輸入,基于以上特點,本文設計了一種視頻疊加顯示系統,具體思路為將雷達、電視視頻通過FPGA 進行預處理,然后通過圖形處理器的視頻輸入端口直接送入圖形處理器內部,在圖形處理器內部完成視頻疊加處理,最后通過圖形處理器的視頻輸出端口進行顯示輸出。該系統最多可支持4 路雷達或電視視頻的同時處理,在實時處理效率上具有顯著優勢。

2.2 核心元件選型

該系統的核心元件主要有國產圖形處理器、FPGA、內存模塊和電源管理單元等,其中采用的國產圖形處理器JARI G12 是由中國船舶集團第七一六研究所研發的一款高性能圖形處理器,其功能特點如下:

(1)支持 OpenCL2.0,提供1.5TFlops 峰值單精度浮點計算能力;

(2)支持 OpenGL4.5,且兼容 OpenGLES3.0;

(3)支持2 路H.264、H.265 編解碼,每路解碼通道支持3840×2160@60Hz,每路編碼通道支持3840×2160@30Hz;

(4)支持4 路數字輸出,每路數字通道顯示分辨率可達3840x2160@60Hz;

(5)支持PCIe3.0/2.0/1.0 標準,支持x16、x8、x4、x1 鏈路;

(6)支持DP、eDP、HDMI、DVI 等顯示接口;

(7)支持國產x86、龍芯、飛騰等國產處理器,支持銀河麒麟、中標麒麟、Jari-Works 等國產操作系統;

(8)對外提供4 路獨立數字視頻輸入。

該系統的FPGA 擬選用Xilinx 公司的XC7K325T-2FFG900I,利用其豐富的邏輯資源來實現視頻數據的格式轉換[5]。JARI G12圖形處理器共有3 個內存通道,每通道可控制4 片內存顆粒,所以

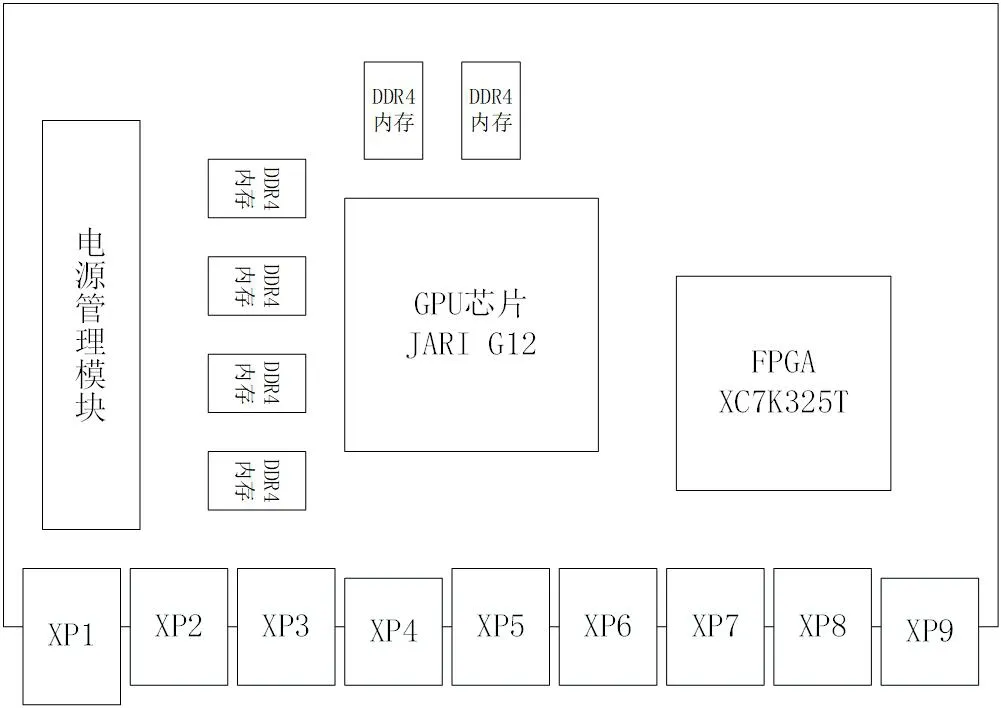

圖1:視頻疊加顯示系統印制板結構圖

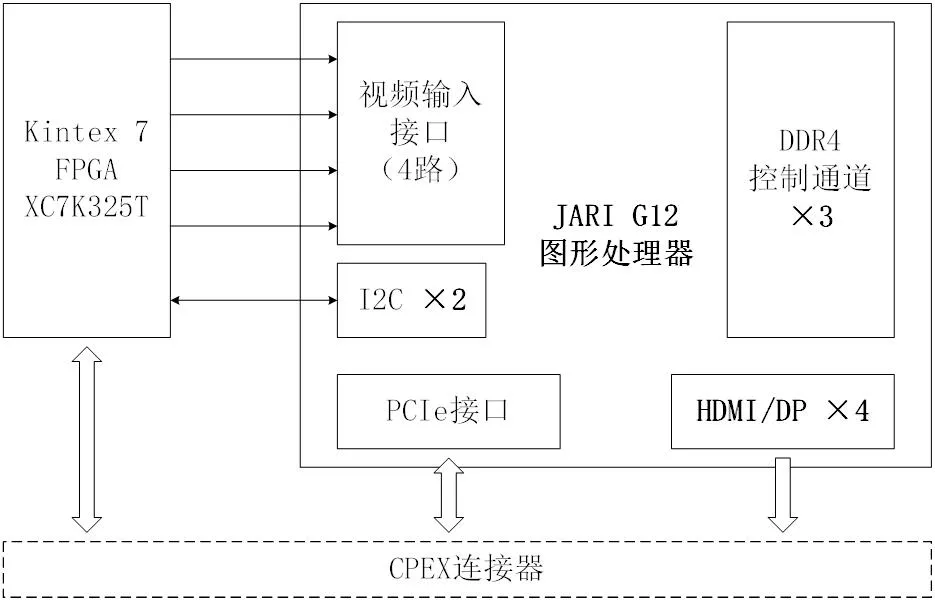

圖2:視頻信號流走向圖

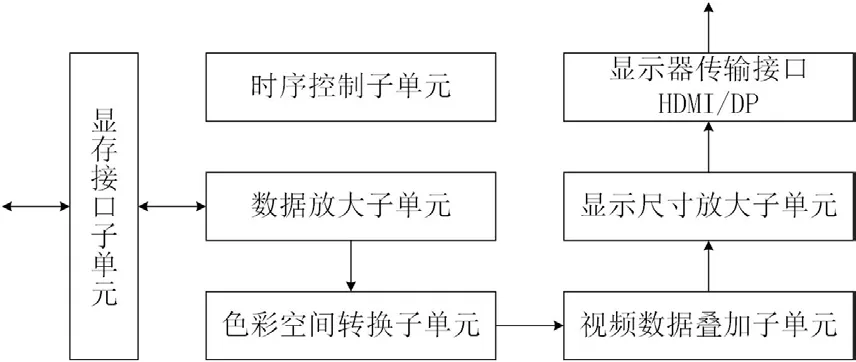

圖3:JARI G12 視頻疊加信號流分析圖

內存模塊擬選用12 片DDR4 SDRAM 內存顆粒,電源管理單元則選用了3 個JCER4630 和2 個JCER4644 電源集成芯片來實現。

2.3 結構設計

該系統在設計時遵循通用化、系列化和模塊化的設計要求,并參考有關規定的6U CPEX[6]結構以及下列要求進行設計:

(1)GPU 芯片放置于PCB 板中間;

(2)DDR4 內存顆粒放置在GPU 芯片旁邊,且在PCB 板正反面對貼放置;

(3)視需求情況放置FPGA、電源等器件。

該視頻疊加顯示系統的布局如圖1 所示。

3 視頻信號流分析

該系統支持4 路雷達或電視視頻的同時輸入,以一路雷達或者電視視頻為例分析該系統的主要信號流走向。如圖2 所示,外部的雷達或電視視頻以差分對的形式通過PCIe 總線傳輸到FPGA,經過格式轉換后通過圖形處理器的視頻輸入端口直接送入圖形處理器內部,存儲在顯存中。視頻輸入端口還包括2 路I2C 總線,用于與圖形處理器的外部進行數據交互。

JARI G12 圖形處理器內部包含了4 個獨立的顯示控制接口單元,每個顯示控制接口單元包含多個子單元,如圖3 所示,以一個顯示控制接口單元為例分析圖形處理器內部視頻疊加處理過程的信號走向。顯示控制接口單元是通過顯存接口子單元從顯存中抓取圖形和視頻數據等信息,再依次經過數據放大和彩色空間轉換子單元,然后以任意指定次序互相疊加在一起。某些特定應用對圖形數據窗口尺寸有固定的大小要求,為了適應不同的顯示器分辨率,疊加完成后的圖形和視頻數據可以通過顯示尺寸放大子單元一起放大到顯示器滿屏幕。最后,疊加后的圖形、視頻數據編碼成HDMI 或DP等標準數據流,通過PCIe 總線送達傳輸接口,送到顯示器進行顯示。數據放大子單元的作用是將數據窗口尺寸任意放大,直至滿屏幕,彩色空間轉換子單元的作用則是將RGB 數據和YUV(YCbCr)數據互相轉換[4],以適應后續數據處理或顯示需要。每個顯示接口控制單元都含有獨立的時序控制子單元,產生顯示器的掃描、同步時序,并協調其它子模塊進行顯存讀寫和顯示器的同步機制。

4 總結

本文介紹了一種基于國產圖形處理器的視頻疊加顯示系統設計,基于國產圖形處理器 JARI G12 的功能特點實現雷達或電視視頻的高效疊加顯示,該系統能夠滿足海軍特色應用需求,且視頻傳輸快捷高效,同時拓展了國產圖形處理器的應用方向,應用前景十分廣闊。疊加效果圖如圖4 所示。

圖4:疊加效果圖