封裝抗輻射加固技術研究

李靖旸,趙鶴然

(中國電子科技集團公司第四十七研究所,沈陽110000)

1 引 言

衛星等航天器在空間運行時,不再受大氣層的保護,電子器件直接受到空間環境中的太空輻射和高能粒子沖擊,進而引發出各種輻射效應,導致異常工作狀態。根據數據統計,國內外發生的航天事故中,約40%是由空間輻射引發的故障[1]。因此,使用航天器件前,對其進行專門的抗輻射加固處理非常必要。設計加固、工藝加固和封裝加固是三種典型的抗輻射加固路徑。設計加固和工藝加固是芯片被輻射后采取的應對措施,皆在消除輻射效應的影響[2]。而封裝加固具有本質上的不同,是通過屏蔽空間輻射的方式,避免芯片受到輻射的直接影響。為實現理想的封裝加固效果,有必要對空間輻射環境、輻射效應影響,以及各種不同封裝材料及封裝方法有全面深入的理解與把握。

2 空間輻射及輻射效應

2.1 空間輻射環境

空間輻射環境中存在著大量的粒子,其中包括電子、中子、質子、光子以及各種重離子。在地球軌道附近的空間輻射粒子,其主要來源有太陽宇宙射線、銀河宇宙射線和地球輻射帶[3]。

太陽輻射是空間輻射環境主要的因素,在太陽耀斑大爆發期間,大量帶電粒子流與高能射線進入空間。爆發強烈時,地球軌道上的質子及氦離子通量將成倍增加,可達4 個量級;相對銀河宇宙射線高能重粒子增加50%。這些高能質子會對地球軌道衛星上的電子設備有極強的破壞性[4]。

銀河宇宙射線來源于太陽系之外,主要組成包含氦離子、質子及高能重離子。其離子密度極小、能量極高且各向同性。這些離子的通量峰值能量最小在100 MeV,最高達到1000 MeV。

地球輻射帶,又名范艾倫帶,分為內外兩層,輻射粒子主要包含電子和質子。其中,帶電粒子在高層大氣和宇宙線的作用下形成高能粒子,經過地磁場不斷作用形成電離輻射。

2.2 輻射效應

輻射效應,是輻射粒子與器件相互作用而引發的器件電性能退化。輻射粒子對太空衛星及航天器的電子系統所造成的損傷主要包括總劑量效應、單粒子效應、瞬時劑量率效應及中子效應。

總劑量效應:屬于積累效應,是輻射引起的氧化物中的電荷累積。其中,氧化物包含隔離氧化層、柵氧化層和絕緣埋層。當電離輻射作用于器件時,會在這些氧化層中產生電子空穴對,少部分會很快復合移走,而未復合的會進而產生正電荷和界面態電荷,將對器件產生不利影響。電荷長期積累會導致內部漏電流增加,運算放大器輸入失調變大,造成材料內部損傷、性能漂移,最終令器件永久損壞。

單粒子效應:作為一種瞬態效應,其產生機理是宇宙中的高能粒子入射到半導體器件中后產生電子空穴對,這些空穴對會引發電路邏輯狀態翻轉,可能還會產生閂鎖。情況嚴重的將出現永久損傷,甚至導致電路燒毀[5]。

瞬時劑量率效應:該效應的產生通常是在一些特定情況下,如核爆炸產生大量高能射線,在短時間內沉積在半導體器件內,電離出大量的電子空穴對,引發器件內部產生較大的瞬時光電流。這種瞬時光電流會引發器件工作發生故障,例如出現閂鎖、邏輯混亂等。

中子輻射效應:中子不帶電,但穿透能力極強,如果入射中子的能量足夠大,可使晶格內大量的原子產生位移,形成大的缺陷群。在半導體材料內,這些缺陷群在原子的禁帶內部引入附加能級,令少數載流子與多數載流子的復合率增加,導致少數載流子壽命減少,從而影響到器件的電學性能。

3 宇航級器件封裝加固

宇航器件不僅僅要應對空間環境帶來的熱、應力問題,更要考慮抗輻射性能,甚至在必要時,犧牲一部分計算性能和存儲空間。由于設計加固、工藝加固都需要針對芯片進行專用的研制和開發,其設計周期、流片周期、測試周期都較長,成本也較高。

20 世紀70 年代,國外研究人員們開始重視CMOS 器件的抗輻射加固封裝技術,核心是將集成電路芯片與空間輻射環境進行適當的屏蔽和物理隔離。試驗證明,封裝加固技術對于屏蔽中子和伽瑪射線較困難, 但對于屏蔽空間輻射環境的高能電子和質子相對有效,尤其對地球輻射帶的電子和質子來說,屏蔽效果明顯。因此,對于宇航器件,封裝加固是一種擴展使用壽命的直接而有效的途徑[6-7]。

4 封裝加固研究進展

4.1 金屬層屏蔽

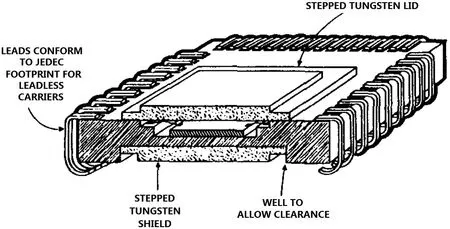

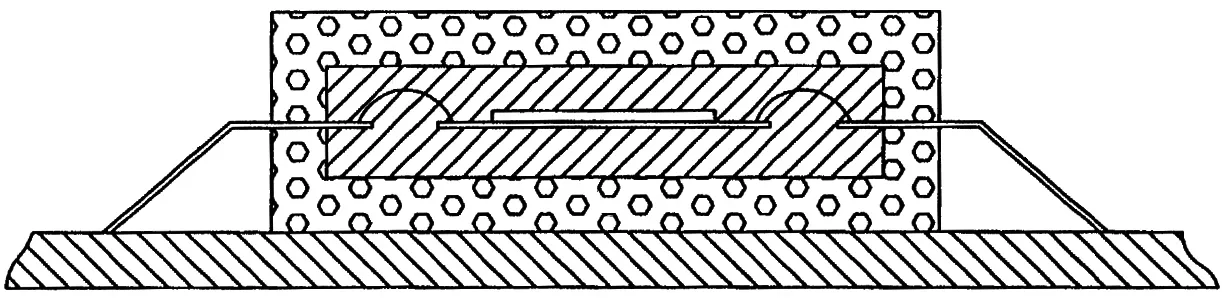

20 世紀70 年代,美國開始研究封裝在輻射方面的各項性能,封裝方式包括金屬封裝和陶瓷封裝,采用重金屬做屏蔽層的封裝級屏蔽方法在半導體器件中開始大量采用。來自美國Maxwell 公司的D.G.Millward 和D.J.Strobel 設計了一種名為Rad-Pak的IC 封裝結構,如圖1 所示,將高Z 屏蔽金屬鎢層設計到封裝結構中,上下采用階梯狀的屏蔽板,總劑量達到 100 krad(Si)[8]。

圖1 Rad-Pak IC 封裝結構圖

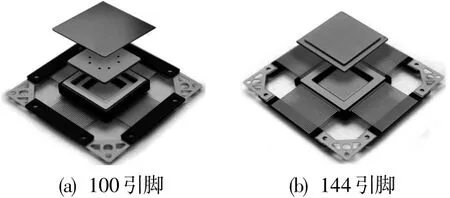

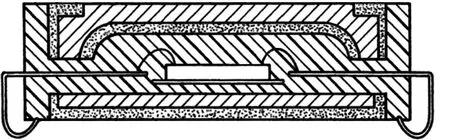

俄羅斯的JSC TESTPRIBOR 設計了專用的帶有鎢銅合金(85%W 和15%Cu)屏蔽蓋的100 引腳和144 引腳陶瓷封裝,用于太空抗輻射,如圖2 所示。頂蓋和底蓋的厚度均為1.2 毫米,100 引線封裝頂蓋上有8 個孔,最上端為可伐蓋板,厚度0.25 毫米[9]。

奧肯思北京科技有限公司公開了一種實用新型專利(CN 206558498 U),為一種基于抗輻照加固的芯片封裝體,在芯片封裝體中設計并安裝上下抗輻照加固材料,厚度為0.3~2 mm 的鉭片,用于抵擋來自芯片上下方的外太空高能輻射[10]。

圖2 集成鎢銅合金的抗輻射陶瓷封裝體

中國航天科技集團公司第九研究院第七七一研究所發明了一種高密度系統集成計算機模塊抗輻照封裝結構(CN 202495444 U),采用多層材料復合的上蓋板和底板,疊層釬焊鎢銅板與可伐框架和蓋板,得到高Z 值材料和低Z 值材料的疊層封裝結構,形成IC 芯片與空間輻射環境的屏蔽和物理隔離,有效屏蔽輻射[11]。

諸如此類在封裝體上下加裝金屬層的方法的缺陷也很明顯:增加了器件的厚度和重量。重量的增加極大地提高了運載火箭發射時的成本。除此之外,屏蔽層與集成電路管芯相距較遠,沒有實現全方向屏蔽,器件側面可能仍會受到輻射。

4.2 薄膜屏蔽

隨著膜材料技術的發展,人們發現了具有輻射抵抗作用的薄膜,僅僅需要幾十個微米厚度,就可以有效降低輻射劑量。

1987 年,日本專利62-125651 闡述了一種名為spotshielding 的抗輻照屏蔽方法。該方法是將一種雙層屏蔽膜分別貼在已封裝的半導體器件的上、下表面。雙層屏蔽膜中的一層主要為高Z 材料,另一層主要為低 Z 材料[12]。

上海航天設備制造總廠發明了一種電子器件抗輻射加固封裝結構(CN 103456719 A),包括含鉛雙馬來酞亞胺基體、輕金屬薄膜和重金屬薄膜。輕金屬薄膜的材質是鋁,厚度為10μm 或者50μm;重金屬薄膜的材質是鎢,厚度為20μm,可實現平均抗輻射總劑量大于100 krad(Si),抗輻射效果良好[13]。

薄膜屏蔽在一定程度上提高了芯片的抗輻照能力,相對金屬片,增重和增厚顯著降低,但仍存在缺點:第一,器件側面同樣會受到輻射,沒有實現全方向屏蔽;第二,屏蔽膜可以有效屏蔽電磁干擾輻射,對高能粒子產生的單粒子效應屏蔽效果不佳;第三,宇航級電子器件必須承受太空飛行時加速度產生的較大應力,雙層膜容易產生撕裂或翹起。

4.3 陶瓷材料屏蔽

高溫共燒陶瓷工藝(HTCC)應用于抗輻照屏蔽的最大亮點在于該工藝能夠將鎢漿料和生瓷帶共燒成具有屏蔽功能的多層陶瓷板。屏蔽功能和鎢銅相當,但密度較小,能夠有效減輕產品的整體重量。

中國電子科技集團公司第十三研究所發明了一種能夠增強輻照屏蔽的陶瓷外殼(CN 102361023B),包括由五層氧化鋁陶瓷層構成的陶瓷外殼本體,在其上下表面各增加一層氧化鋁陶瓷層,在各個氧化鋁陶瓷層的上表面設有采用金屬化漿料印刷的起布線作用的線條和起輻照屏蔽作用的圖形。相比常規陶瓷外殼,使用此種設計,對空間電離總劑量的輻照屏蔽效果被提高了10 倍以上[14]。

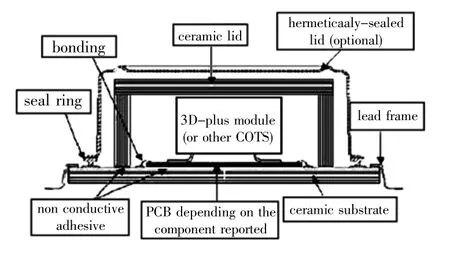

2005 年,法國3D PLUS 公司研制出一種名為WALOPACK 的新型抗輻照封裝結構,采用抗輻照高溫共燒陶瓷外殼,如圖3 所示。其采用HTCC 工藝將多層鎢漿料和氧化鋁陶瓷制作成陶瓷板,再以該陶瓷板構成密閉封裝腔體。3D PLUS 公司已經采用這種結構封裝了16 Mb SRAM 器件和8 Mb EEPROM器件,實現了3D 抗輻射屏蔽,可承受的電離總劑量(TID)達到 200 krad(Si)[15]。

圖3 3D PLUS 公司的WALOPACK 封裝結構

HTCC 封裝的半導體器件能夠實現3D 全方位屏蔽,組裝工藝也簡單易行,缺點在于需要針對不同型號尺寸的芯片、不同的組裝工藝定制不同的專用陶瓷外殼和蓋板。

4.4 包封料屏蔽

利用具有屏蔽功能的膠體將芯片包封起來,也可達到屏蔽效果,實現抗輻照。這種屏蔽膠是將屏蔽粉料以很高的密度填充在樹脂中,再添加調節劑控制膠體黏度。

James W.Sloan 等人公開了一種這一類的保護集成電路管芯的方法[16]。封裝前,將液態聚酰胺前體化合物沉積在管芯的有源表面上,待初始沉積物固化后,即可在其頂部上層疊相同材料的其他沉積物,從而增加保護材料的厚度。足夠厚的聚酰胺涂層可為封裝提供α 粒子防護。這一方法的缺點是用于容納聚酰胺層的空間非常有限,所提供用來保護芯片免受輻射所需的保護材料的厚度可能不足。

采用芯片包封方式進行抗輻照屏蔽的難點在于制備高性能的屏蔽膠體。高填充密度的膠體與裸芯片接觸時,其中的金屬顆粒可能接觸到鍵合絲或者基板的表面走線,臨近顆粒間若發生接觸就有可能具有導電性并導致短路。只有利用絕緣強度很高的樹脂結合劑將金屬顆粒完全浸潤并使其始終處于懸浮狀態,才能避免短路發生。

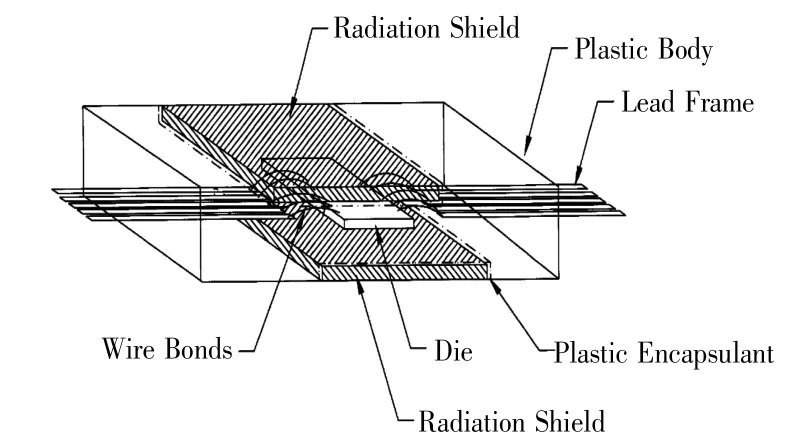

Michael Featherby 等人發明了一種屏蔽膠(US 6455864 B1),將屏蔽顆粒分散在粘接劑中[17]。其主要成含有鎢粉,環氧混料和其他增補劑。應用于封裝屏蔽的結構如圖4 所示。這種屏蔽具有高效、經濟的優點,其使用方式靈活,可采用模塑、填充、噴涂、包覆等,不僅能夠用于封裝抗輻射,還可作為人類太空防輻射涂料使人體免受輻射影響。

屏蔽膠優點為使用簡便靈活,可局部器件屏蔽,也可以對整個產品屏蔽,且填充過程不占用過多的組裝空間。

圖4 采用屏蔽膠的封裝結構示意圖

4.5 塑料封裝屏蔽

Joseph J.Dlugokecki 等發明了塑料封裝重構方法(US5406117A)[18]。該方法將屏蔽材料嵌入組裝前的塑料封裝體用來提供輻射屏蔽,屏蔽結構如圖5所示。采用機械研磨法將塑封后的芯片頂部底部的包封料去除,之后貼裝屏蔽材料,最后用附加的包封材料完成密封。

圖5 塑料封裝重構的剖面示意圖

大部分常規塑封器件都可采用這種方法進行重構,重構后的塑封器件外形尺寸變化不大,不影響表面貼裝工藝。其缺點是研磨工藝復雜,容易破壞器件內部鍵合引線,重構后器件厚度略有增加。另外,附加的包封材料需要與原包封料相匹配,同時需具備較強的抵抗水汽滲透的能力。

David J.Strobel 等人發明的塑料封裝重構方法(US5889316)[19],結構更加簡化。它是通過提供一種新的和改進的工藝來實現的,結構如圖6 所示。通過該工藝,有選擇地除去形成集成電路的塑料體封裝的塑料并用具有特定配方的輻射屏蔽材料代替,即可以根據空間應用需求,定制屏蔽材料。

圖6 一種抗輻射塑封結構示意圖

5 封裝加固技術展望

雖然各國科研工作者長期致力于封裝加固技術的研究,但是目前在技術層面仍面臨諸多挑戰。對于“寸土寸金”的航天應用來說,增重是不得不考慮的關鍵問題之一。針對這方面問題,未來研究的重點,主要可能集中在以下幾個方面:

1) 提高器件有效屏蔽面積比率。封裝加固保護的對象是芯片,但是,實際投入的屏蔽材料的面積往往是芯片的數倍之多。因此,封裝設計師要盡量減少封裝屏蔽的尺寸,從而減少器件的增重。

2) 提高相同質量密度下材料的抗輻射性能。高、低原子序數的金屬材料在屏蔽中發揮著不同的作用,新型高分子材料也是研究的熱門,如何發揮各材料的特點,制備高性能復合抗輻射材料,是提高相同質量密度下材料的抗輻射性能的重要途徑。

3) 開發高性能新材料。近年來,高分子材料、納米材料等新型材料技術的逐漸成熟,為輻射屏蔽注入了新的活力,研究新型高性能材料的屏蔽機理對指導封裝加固的實際工作有重要意義。

除了增重問題,長期服役可靠性仍然是空間應用中的基本要求。不論是一體化屏蔽封裝,還是后期涂覆、制備的抗輻射涂層,都應通過元器件的環境測試,屏蔽材料不損壞、脫落,屏蔽性能不退化。

6 結 束 語

對空間輻射帶環境以及輻射效應的影響有正確的理解,才能夠在確定封裝材料與方法時作出正確的選擇,確保外太空嚴酷環境下的器材的正常使用。上述闡述主要從理論層面而言,而在實際應用中,可制造性決定封裝加固器件能否實際應用,故此在提升抗輻射指標和確保器件的氣密性、絕緣性、耐腐蝕性不降低的同時,還應充分考慮不同批次加固器件的一致性等,這也將在后續研究中作進一步探討。