BCD工藝下光電集成的單光子雪崩光電二極管及前端電路的研制

史曉鳳,龐 雪,朱麗君,張新宇,張 媛,韓 波,李佩君,郭 博,程 翔*

(1.阜陽師范大學計算機與信息工程院,安徽阜陽236037;2.廈門大學航空航天學院,福建廈門361102)

1 引 言

隨著工業儀器的智能化及人臉識別等技術的興起,二維圖像由于缺失深度信息存在無法甄別合成圖像手段的風險。三維(Three-Dimensional,3D)信息能更加客觀全面的重構實物,獲得許多人眼所不能直接獲取的量化參數,有效彌補二維圖像的缺點,因此成為視覺傳感的研究熱點。主流的3D傳感技術有雙目視覺、結構光技術和時間飛行法(Time Of Flight,TOF)技術[1]。TOF技術通過計算傳感器收發紅外光的時間差來測量距離,具有響應速度快、深度精確度高(可達微米級)、功耗低,不需要復雜軟件支撐等特點,因此得到了廣泛的應用。TOF主要由蓋革模式-單光子雪崩光電二極管(Gage Mode-Single Photon Avalanche Photodiode,GM-SAPD)探測陣列、淬滅復位電路以及時間數字轉換器組成[2-3]。其中,淬滅復位電路用來控制雪崩脈沖,以方便光子計數。TOF對探測器陣列性能和相關電路的精確度的要求較高。隨著CMOS工藝的不斷進步,硅基SPAD器件的性能逐漸提高,高性能SPAD器件可以顯著提高TOF系統的性能指標,因此其設計具有重要意義[4-6]。

GM-SPAD是基于雪崩效應的單光子探測器,主要用于探測微弱光信號。為了實現器件的高度集成化,探測單元面積應盡可能的小,并且結合淬滅電路可實現大規模陣列集成,用于量子通信、生物醫學檢測、熒光測溫等領域。經過幾十年的研究,GM-SPAD經歷了從臺式到平面的演變[7]。近年來,很多基于標準工藝的GMSPAD研究都提到了保護環的重要性,這是因為在深亞微米制造工藝中注入和擴散步驟難以避免在邊緣區域形成彎曲的PN結,有研究表明彎曲結角處的電場比平面結電場高得多,所以容易導致邊緣提早擊穿,影響探測器的性能[8]。研究表明,通過設計保護環能夠有效防止邊緣提前擊穿,比如低摻雜阱保護環結構,中心淺層P+的邊緣注入輕摻雜的Pwell,具有消除突變的邊緣摻雜曲線和角效應的作用,降低了電場強度,從而避免邊緣提前擊穿[9]。保護環的結構會顯著影響器件的暗計數率(Dark Count Rate,DCR)[10-12]。理查森等人采用130 nm CMOS工藝實現了一種虛擬深阱保護環SP-AD結構。與常規Pwell保護環相比,虛擬深阱保護環顯著降低了SPAD的DCR[13]。

BCD是一種有多層金屬,N埋層和P外延層的雙極型CMOS混合信號工藝。眾所周知,P外延層與P襯底相比晶格缺陷和點缺陷少很多,金屬雜質的濃度更低,在半導體器件制造中更為理想。本次設計的探測器主要針對600~900 nm波段的光子,由文獻[14]可知1μm深的耗盡層處650 nm光的吸收率能達到30%左右,對于更長波長的光則需要更深的耗盡層。同傳統CMOS工藝相比,BCD工藝的PN結深更深,可以提供30 V的高壓,更符合本次設計的需求。

本文基于BCD工藝設計了一種用于檢測微弱光信號的SPAD及前端淬滅-復位電路(QAC),該圓形P+/Nwell/Deep Nwell結構SPAD與傳統的P+/Nwell結構以及P+/Nwell/BNwell結構相比,在擊穿電壓和響應度等關鍵指標上具有顯著優勢。,

2 SPAD結構設計與優化

2.1 結構設計

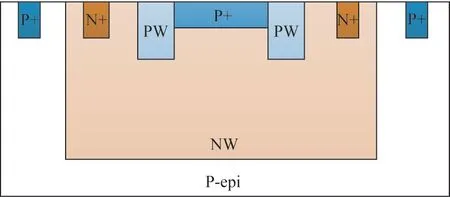

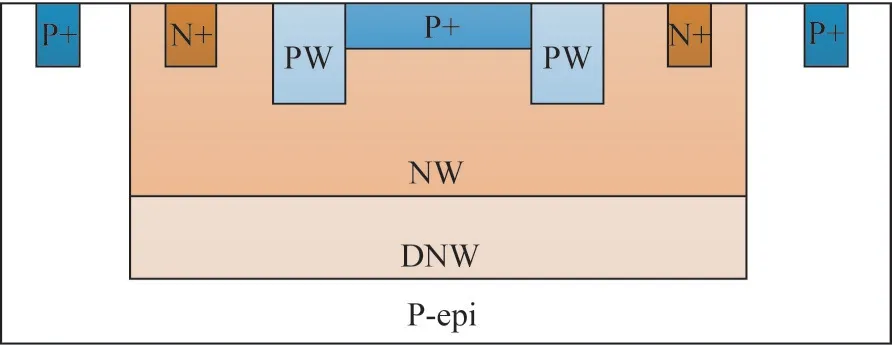

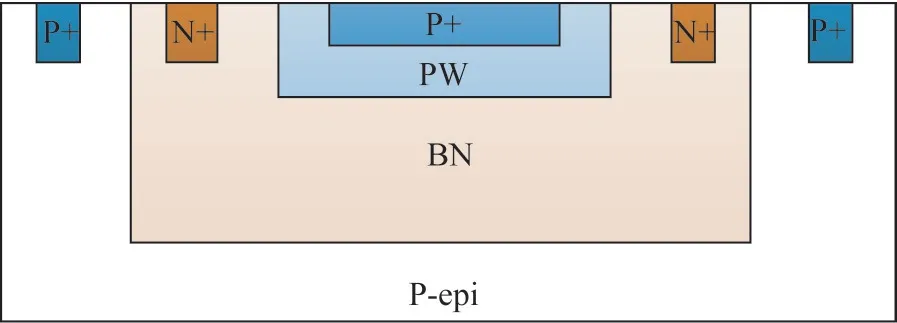

圖1 為傳統CMOS工藝中的P+/Nwell結構SPAD,記作PD1。該結構以P-epi為襯底,P+為中心有源區,P+附近的輕摻雜Pwell形成保護環,防止發生邊緣提前擊穿,P+與Nwell接觸的地方為倍增區,從P+引出陽極金屬接觸,N+引出陰極金屬接觸。為了提高光譜響應,降低DRC,本文在結構P+/Nwell結構的基礎上添加了DNwell,如圖2所示,記作PD2。由于DNwell的濃度梯度呈逆向分布,即靠近表面的濃度更低,使形成的PN結能承受更高的電壓,不易被擊穿。同時,利用DNWell將器件與襯底有效隔離開,能減少噪聲和閂鎖效應。為與P+/Pwell/DNWell結構做比較,設計了P+/Pwell/Buried-Nwell結構,記作PD3,如圖3所示。同樣以P-epi為襯底,P+為中心有源區,利用Pwell增大了與Buried-Nwell的接觸面積,同時避免了普通P/N阱高摻雜雪崩結引起的帶帶隧穿,有效降低DCR,兩端的Pwell和Buried Nwell構成雙重保護環,使電場分布更加均勻,能夠有效阻止邊緣提前擊穿。

2.2 電場分布

圖1 P+/Nwell結構(PD1)Fig.1 P+/Nwell structure(PD1)

圖2 P+/Nwell/Deep-Nwell結構(PD2)Fig.2 P+/Nwell/Deep-Nwell structure(PD2)

圖3 P+/Pwell/Buried-Nwell結構(PD3)Fig.3 P+/Nwell/Buried-Nwell structure(PD3)

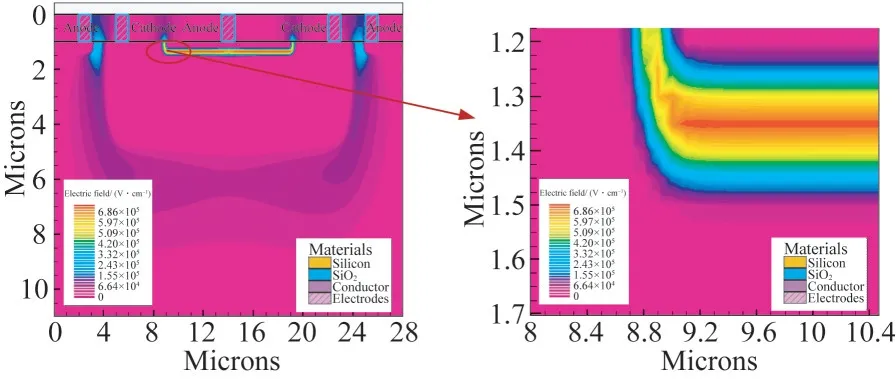

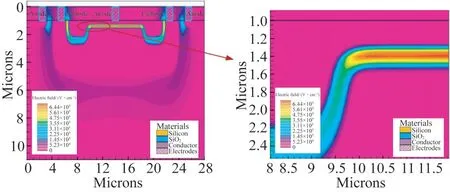

基于Silvaco對3種結構的探測器進行仿真設計。結合工藝設計規則,為了盡可能地減小探測器的整體面積同時增加探測器的填充系數,采用28μm長的襯底,以光敏直徑為10μm進行仿真。圖4為PD1無P阱保護環的電場分布,電場集中在P+注入區,且電場較強,從局部放大圖可以清晰地看到拐角處電場高達6.6×105V/cm,在此高電場條件下容易發生角效應,引起邊緣提前擊穿。圖5為PD1有保護環的電場分布,可看到電場主要分布在兩個P阱和P+注入區的外緣線,P+注入區中間電場較高,兩端邊緣處電場較低,拐角處電場約為4.0×105V/cm,能防止提前擊穿。從有無保護環兩種結構的電場仿真可知,添加保護環結構能有效預防角效應引起的邊緣提前擊穿。

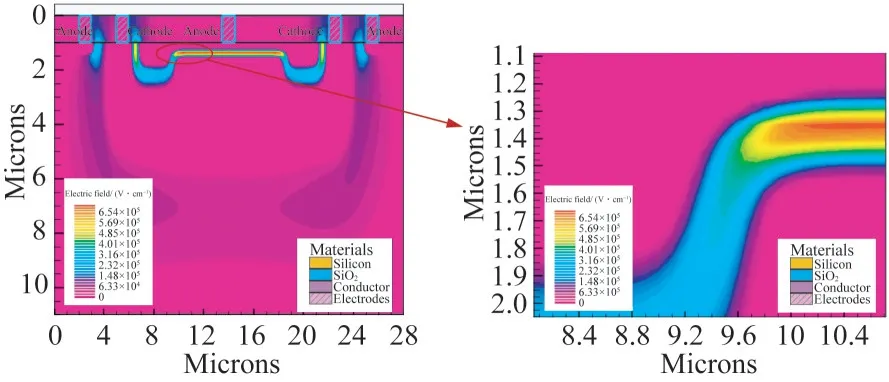

PD2的電場分布如圖6所示。電場集中在P+區,兩邊的P阱上也承擔了部分電壓,從圖6的局部放大圖可以看出P+區兩端邊緣處電場明顯降低,減少了邊緣擊穿的風險。

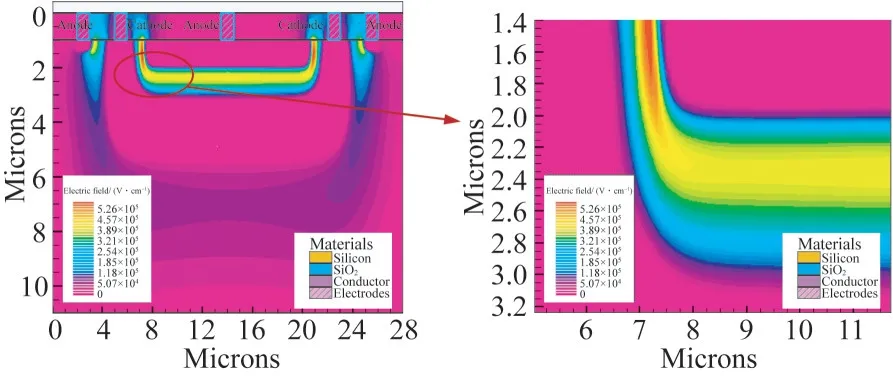

PD3結構的電場分布如圖7所示。電場集中在Pwell上形成環狀,電場分布均勻,拐角處電場約為4.4×105V/cm。由局部放大圖可知,拐角處電場明顯比其他區域電場小,證明此結構可以預防角效應導致的邊緣提前擊穿。

圖4 PD1無保護環時的電場分布Fig.4 Electric field distribution of PD1 without protection ring

圖5 PD1有保護環時的電場分布Fig.5 Electric field distribution of PD1 with protection ring

圖6 PD2的電場分布Fig.6 Electric field distribution of PD2

從3種探測器的電場分布上看,他們均能有效地防止角效應帶來的邊緣提前擊穿,前兩種結構在P阱與P+注入連接處附近的電場變化更為明顯,PD3的電場分布更均勻,數值也更高。

圖7 PD3的電場分布Fig.7 Electric field distribution of PD3

2.3 I-V特性

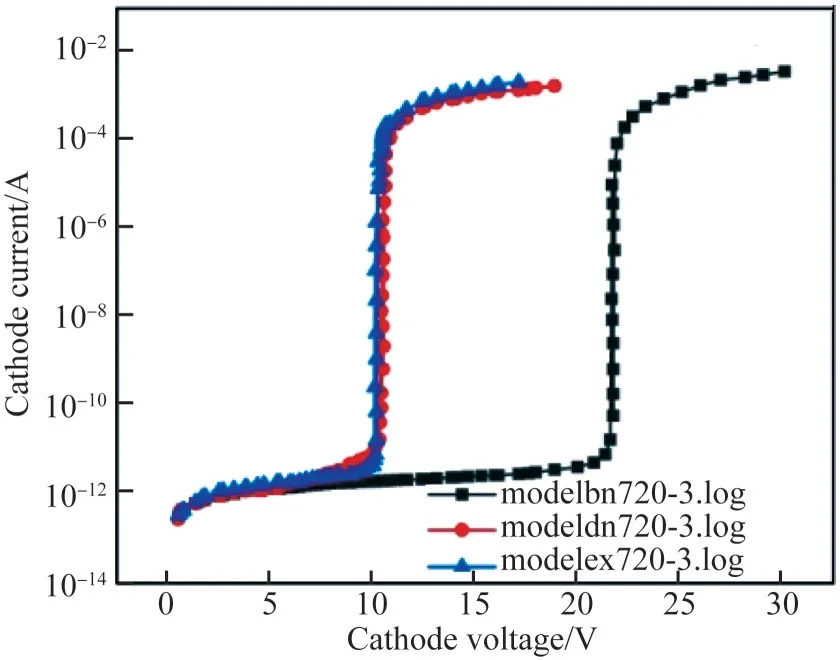

反向電壓增加到一定值,使PN結的電流急劇增加的現象被稱為擊穿現象,此時對應的電壓為擊穿電壓。PD1的I-V曲線如圖8中modelex720-3.log所示,反偏電壓較小時,電流約為1.0×10-12A,且隨著反偏電壓的增大變化不大,電壓增至10.2 V時電流陡增至1.0×10-2A,隨后的電流增長趨于飽和。GM-APD的特性曲線表明,當電壓小于10.2 V時,探測器工作在反偏線性區,擊穿電壓為10.2 V,電壓大于10.2 V時處于蓋革狀態。PD2的擊穿特性曲線如圖8中modeldn720-3.log所示,電流在反偏電壓為10.5 V處陡增至1.0×10-2A,擊穿電壓相比前一種結構增加了0.3 V,所以此種結構能承受更高的電壓。

PD3的擊穿特性如圖8中modelbn720-3.log所示,擊穿點約為21.6 V,比前兩種結構都要高。這是由于形成的PN結位于Pwell和BNwell之間,結深較前兩種結構大很多,P阱相比P+的濃度要低很多,導致空穴的濃度較小,形成的耗盡層寬度較大,所以需要提供更高的反向偏壓才能擊穿。顯然,PD1和PD2的擊穿電壓較低。

圖8 三種SPAD結構擊穿電壓的仿真曲線比較Fig.8 Comparison of breakdown voltage simulation curves of three SPAD structures

2.4 光譜響應

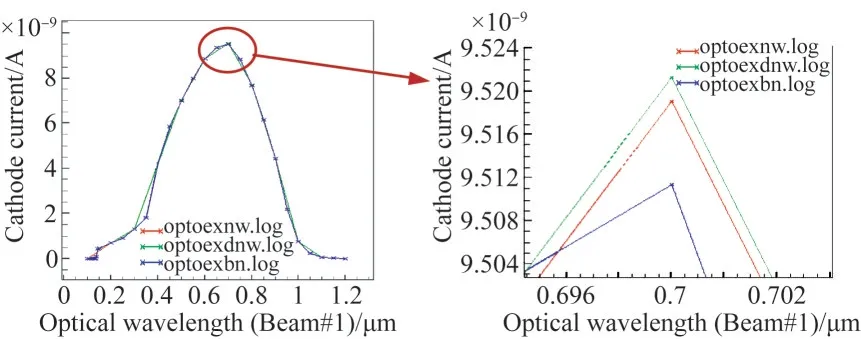

光譜響應反映了光子產生電子空穴對的能力,對于不同波長的光,探測器轉換成光電流的能力也不一樣,設置不同波長的光束照射探測器。3種SPAD結構在反偏電壓相同時入射波長與光電流的關系曲線如圖9所示,0.35~0.7μm波段中光電流隨波長的增加速度更快并在波長約為0.7μm達到峰值,峰值處光電流約為9.5 μA,波譜范圍較寬為0.35~1.2μm。將峰值處放大可見PD2的峰值最大,對應綠色的線條,且整個曲線都在P+/Nwell結構上方(彩圖見期刊電子版)。因此,PD2的光譜響應能力優于另外兩種。

圖9 三種SPAD結構的光譜響應仿真曲線Fig.9 Spectral response simulation curves of three SPAD structures

2.5 有源區尺寸仿真

有源區作為光子探測吸收的主要區域,其尺寸對探測器也有重要的影響。大尺寸的有源區能增加探測面積,提高探測器的填充系數,同時也會引起較高的DRC,探測器整體體積過大等缺點,所以需要研究不同直徑有源區的特性,優化設計以保證流片的效果。本文在有源區直徑分別為6,8,10μm的情況下對3種探測器的I-V特性進行了仿真。

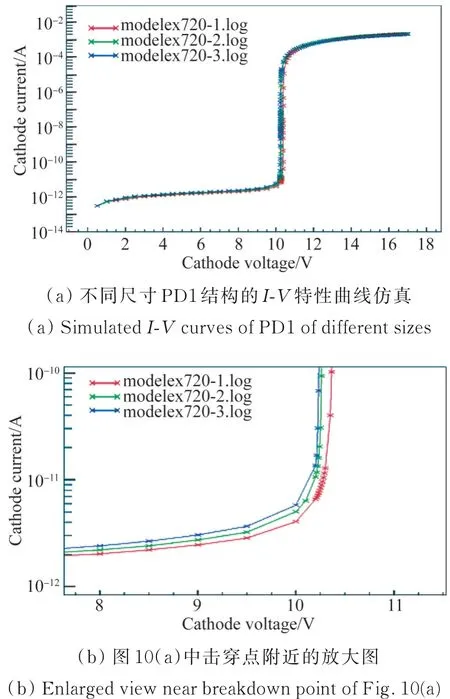

PD1反向偏壓和電流關系的仿真結果如圖10所示,其中modelex720-1.log、modelex720-2.log、modelex 720-3.log分別為有源區直徑為6,8,10μm時的仿真曲線。擊穿點附近的I-V曲線的放大圖如圖10(b)所示,由圖可知有源區直徑為6μm時擊穿電壓最高,10μm時擊穿點電壓最低。

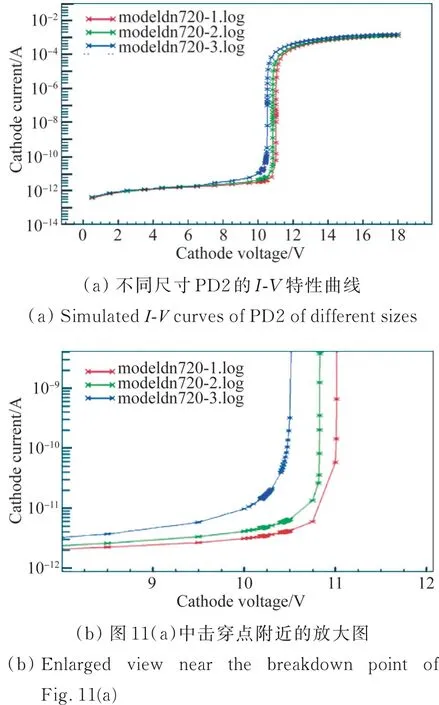

PD2的I-V仿真曲線如圖11(a)所示,modeldn720-1.log、modeldn720-2.log、modeldn720-3.log分別為有源區直徑為6,8,10μm時的仿真結果。擊穿點處的局部放大圖如圖11(b)所示,有源區直徑為6μm時探測器的擊穿電壓約為11 V,8μm時擊穿電壓為10.8 V,直徑增加到10 μm時擊穿電壓為10.5 V。

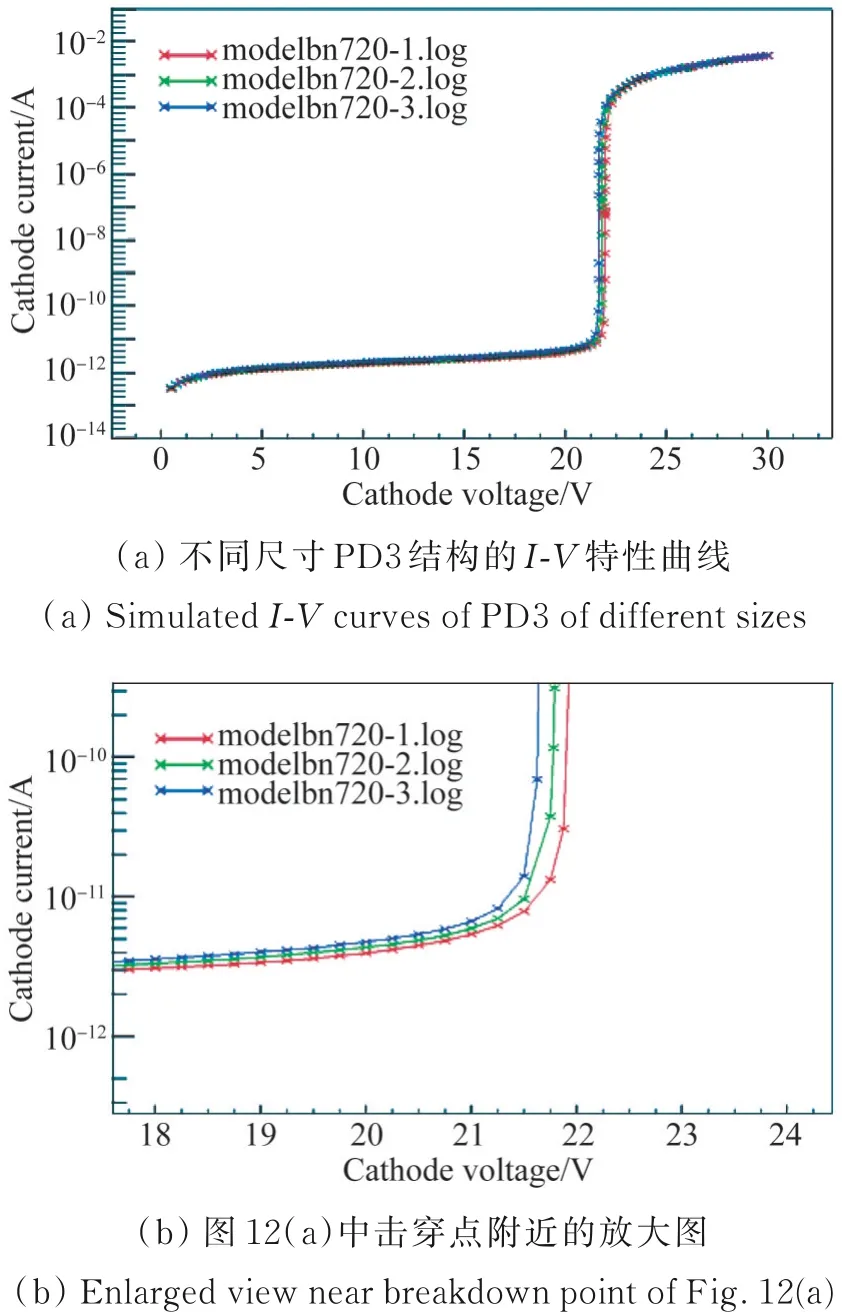

PD3的I-V特性仿真曲線如圖12所示,modelbn720-1.log、modelbn720-2.log、modelbn720-3.log分別為有源區直徑為6,8,10μm時的仿真結果。有源直徑為6μm時擊穿電壓為21.9 V,8 μm時為21.7 V,10μm時為21.6 V。

圖10 不同尺寸的PD1的I-V特性曲線Fig.10 Simulated I-V curves of PD1 of different sizes

通過比較3種光電探測器的仿真圖,可以看出隨著有源區尺寸的增大,3種結構的擊穿電壓的節點均逐漸減小,這跟大面積有源區的探測器中更容易碰到局部高電場區域發生擊穿的情況有關。為了獲得較低的擊穿電壓,較高的響應度,最終選取有源區尺寸為10μm的PD1和PD2進行流片。

3 前端電路的協同設計與仿真

圖11 不同尺寸的PD2的I-V特性曲線Fig.11 Simulated I-V curves of PD2 of different sizes

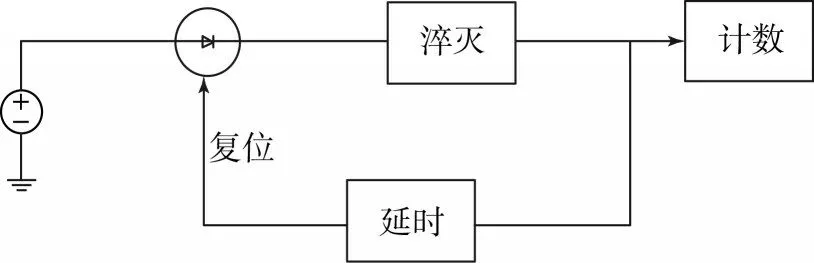

由于探測器雪崩過程不能自主熄滅和發生,因此前端電路對GM-APD的控制和信號讀出發揮著重要的作用。前端電路的工作結構如圖13所示,信號光引發探測器發生雪崩,同時作為TDC(Time Digital Conventor)的計時開始信號,淬滅電路快速淬滅雪崩并經延時復位恢復雪崩準備狀態,產生的雪崩脈沖作為TDC的計時終止信號。

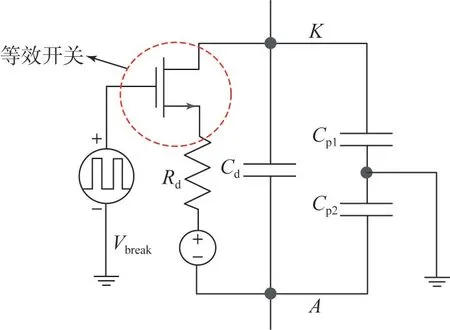

3.1 GM-APD等效模型設計

原始的等效模型結構[14]簡單,能模擬GMAPD的充電特性,在電流源充電時探測器兩端電壓呈線性增長,但是缺乏對體電阻及寄生電容等因素的考慮,只能進行粗略的仿真分析,并不能準確地描述探測器工作時陰陽兩極電壓的變化。在改進探測器結構時應考慮體電阻和寄生電容的影響。如圖14所示,Vbreak是雪崩擊穿電壓,Rd為APD的內電阻,電容Cd為反相偏壓結電容,Cp1和Cp2分別為陽極-襯底結電容和陰極-襯底結電容,通常有Cp1≈Cp2。開關控制雪崩的發生,開關導通時電容放電探測器處于準備探測狀態,開關斷開時電容充電探測器不發生雪崩。仿真中開關采用MOS管代替。

圖12 不同尺寸的PD3的I-V特性曲線Fig.12 Simulated I-V curves of PD3 of different sizes

圖13 外圍電路結構Fig.13 Peripheral circuit structure

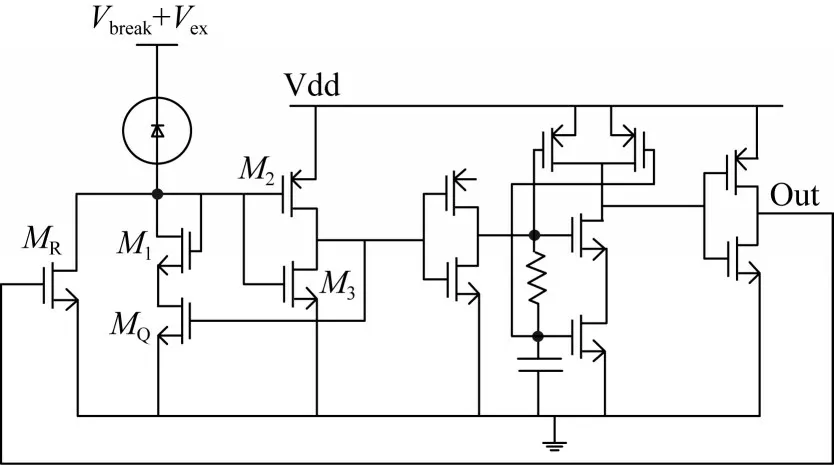

3.2 淬滅電路的設計仿真

APD工作在蓋革模式下意味著一旦觸發雪崩,雪崩電流會持續存在,無法繼續進行檢測,且長時間的大電流通過會導致器件發熱產生較大的功率損耗,載流子被深能級的陷阱捕獲使后脈沖發生的概率增加,因此必須采取措施控制雪崩并恢復原來的狀態。淬滅電路的功能就是中斷雪崩倍增過程,改進的主動淬滅電路拓撲如圖15所示,其中Vex為過偏壓。改進后的電路結構緊湊,沒有比較處理單元和相關多余電阻,不需要選取合適參考電壓,開關切斷電流路徑即可達到淬滅的目的,相比于傳統的淬滅結構響應速度更快。

圖14 仿真電路的模型Fig.14 Model of simulation circuit

當NMOS柵源偏壓大于導通閾值電壓Vgs時管子導通,利用這一性質用NMOS管代替開關,其中MQ為淬滅開關,MR為復位開關。M2和M3為一組由PMOS和NMOS構成的簡單反相器,MQ導通MR截止時,探測器的陽極處接地電壓為低電平,經反相器翻轉輸出高電平信號,此時探測器兩端偏壓大于擊穿電壓,有光子入射時激發雪崩,M1和MQ形成的支路受探測器突增的光電流影響電流增大。同時,M1和M3形成電流鏡結構,電流復制至反相器使二極管陽極處的電壓增加,輸出信號電平減小最終使MQ的柵極電壓低于閾值電壓Vgs,此時的MQ處于截止狀態,相當于一個高阻值電阻使陽極的電壓逐漸上升直至探測器兩端偏壓小于擊穿電壓,探測器成功淬滅。經過后續延時電路處理過的高電平信號作用在MR的柵極上,MR導通并對探測器進行充電。通常為了防止淬滅,充電沒有結束開關就已導通或者淬滅不完全有后脈沖的影響,設置延遲時間大于淬滅時間。

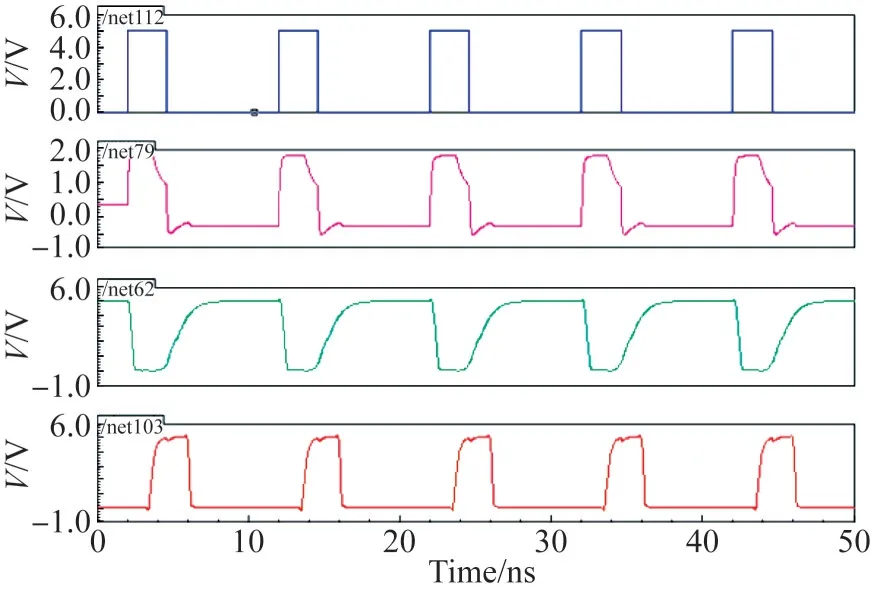

仿真基于cadence/spectre,設置擊穿電壓為10.5 V,二極管陰極處外加電壓為12 V,仿真波形如圖16所示。從上至下依次為模擬光子到來的開關脈沖波形,二極管陽極處的電壓波形,out處電壓波形和reset復位管柵極處波形。其中,開關脈沖延遲時間為2 ns,上升時間為1 ps,下降時間為1 ps,脈沖寬度為3 ns,周期為10 ns。從二極管的陽極電壓波形可以看出,當開關管處于斷開狀態時陽極電壓近乎為零,二極管兩端的反向偏壓大于10.5 V;當開關管閉合光子到來時,二極管發生雪崩擊穿的同時陽極處電壓迅速升高,峰值電壓約為1.9 V,此時二極管的兩端偏壓小于10.5 V的擊穿電壓,二極管被成功淬滅,隨后經復位電路對二極管進行充電使陽極處電壓回落到0 V,二極管再次處于擊穿狀態等待下一次光子的到來。以陽極峰值電壓1.9 V的百分之一為標準,即單個周期內電壓超過19 mV的時間段可作為死時間,此電路的死時間約為2.6 ns,能夠達到快速探測的目的。

圖15 淬滅電路仿真Fig.15 Simulation of quenching integrated circuit

圖16 淬滅電路的仿真波形Fig.16 Simulation waveforms of quenching integrated circuit

4 實驗結果及分析

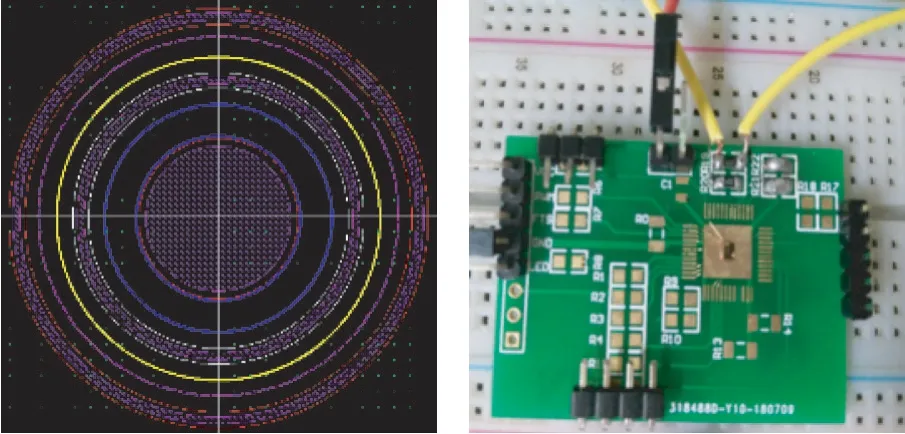

圖17 單個探測器的版圖及芯片打線封裝后的照片Fig.17 Map of individual detectors and test board of chip after drawing package

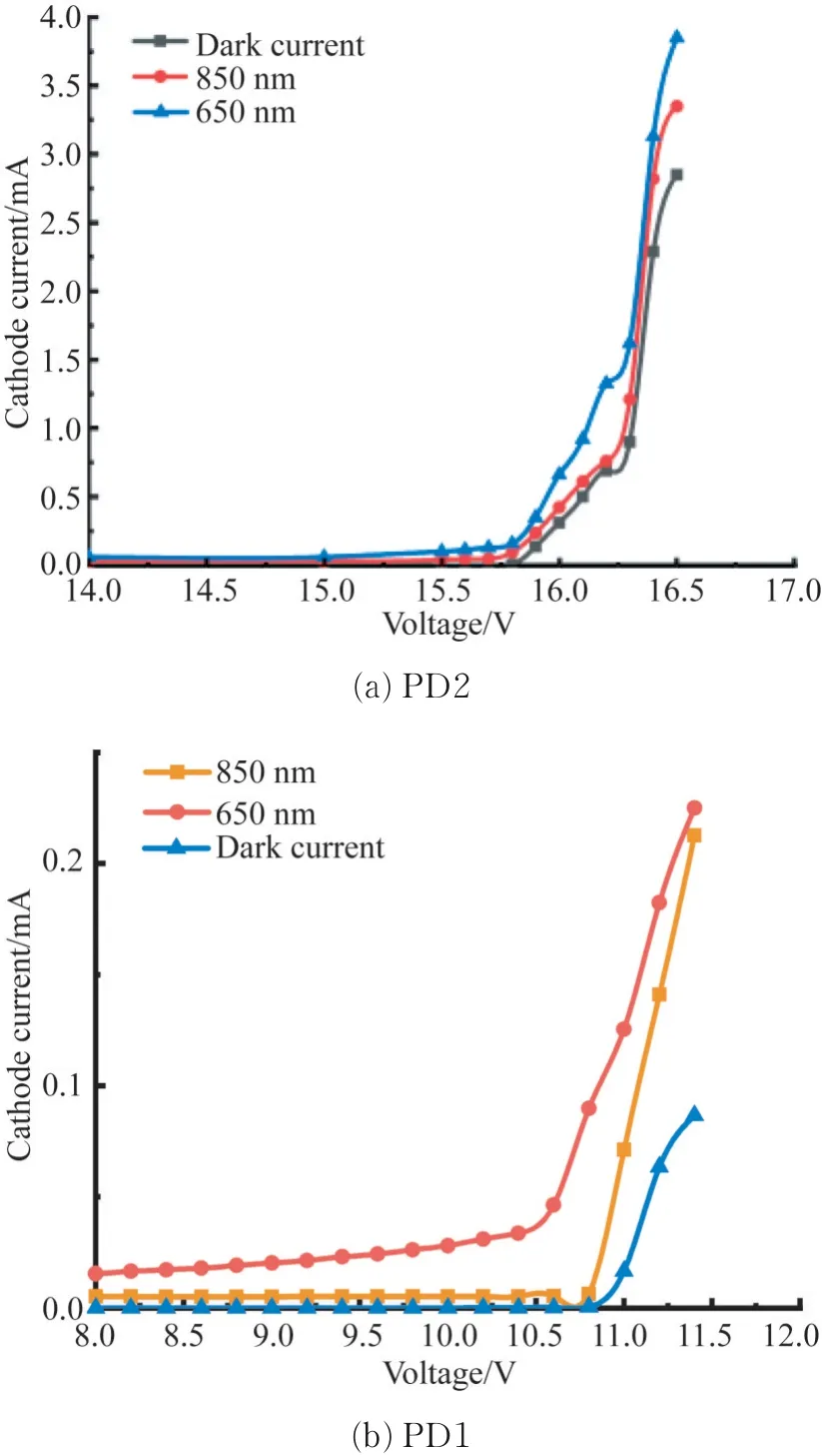

測試實驗在室溫下進行,圖17為單個探測器及芯片封裝后的照片。PD2和PD1的APD兩端的反向偏置電壓與陰極電流關系曲線分別如圖18(a)和18(b)所示。由圖18(a)可以看出,不加光照時,反偏電壓在15.8 V以下,暗電流很小,在10-14A量級;但當反偏電壓增至15.8 V時電流增加明顯,并隨著反向電壓的增大不斷增加。給APD分別施加650 nm波長和850 nm波長的激光照射,在偏置電壓小于15.8 V時,受光生載流子的影響,陰極電流明顯比不加光照時大很多,不過仍維持在較低水平;當電壓增加至15.8 V附近時電流陡增。從測試I-V變化曲線上不難得出,PD2結構APD的擊穿電壓為15.8 V,比仿真的擊穿電壓10.5 V高,這是因為流片工藝的影響,該偏差在允許范圍內。電流隨電壓的變化規律與仿真結果吻合,同時在相同光功率照射下,650 nm波長光對應的電流明顯大于850 nm對應的電流,證明了前面的仿真結果和設計的可行性。同時發現,曲線在偏置電壓增至約16.3 V時出現了拐點,電壓超過拐點后陰極電流迅速增加。這是由于此結構包含P+/Nwell、DNwell/Sub兩個PN結,DNwell/Sub形成的PN結因為摻雜濃度較低,所以相對于P+/Nwell形成的PN結擊穿電壓較高,在電壓升高至16.3 V左右時會形成第二次PN結擊穿。

從圖18(b)可以看出,偏置電壓低于10.6 V且無光照時陰極電流較小,在10-12A數量級,在此偏置電壓下給予光照會發現,陰極電流比不加光照時有所提升,當偏置電壓達到10.6 V后,陰極電流陡增,且相同的偏置電壓下和光功率下,650 nm波長對應的電流大于850 nm波長的電流。根據3條曲線的走勢可以判斷出P+/Nwell結構的雪崩擊穿電壓點為10.6 V,與仿真結果10.2 V非常接近,在可允許的范圍內,測試結果與仿真趨勢基本一致。

圖18 光電探測器的I-V測試曲線Fig.18 Tested I-V curves of photodetectors

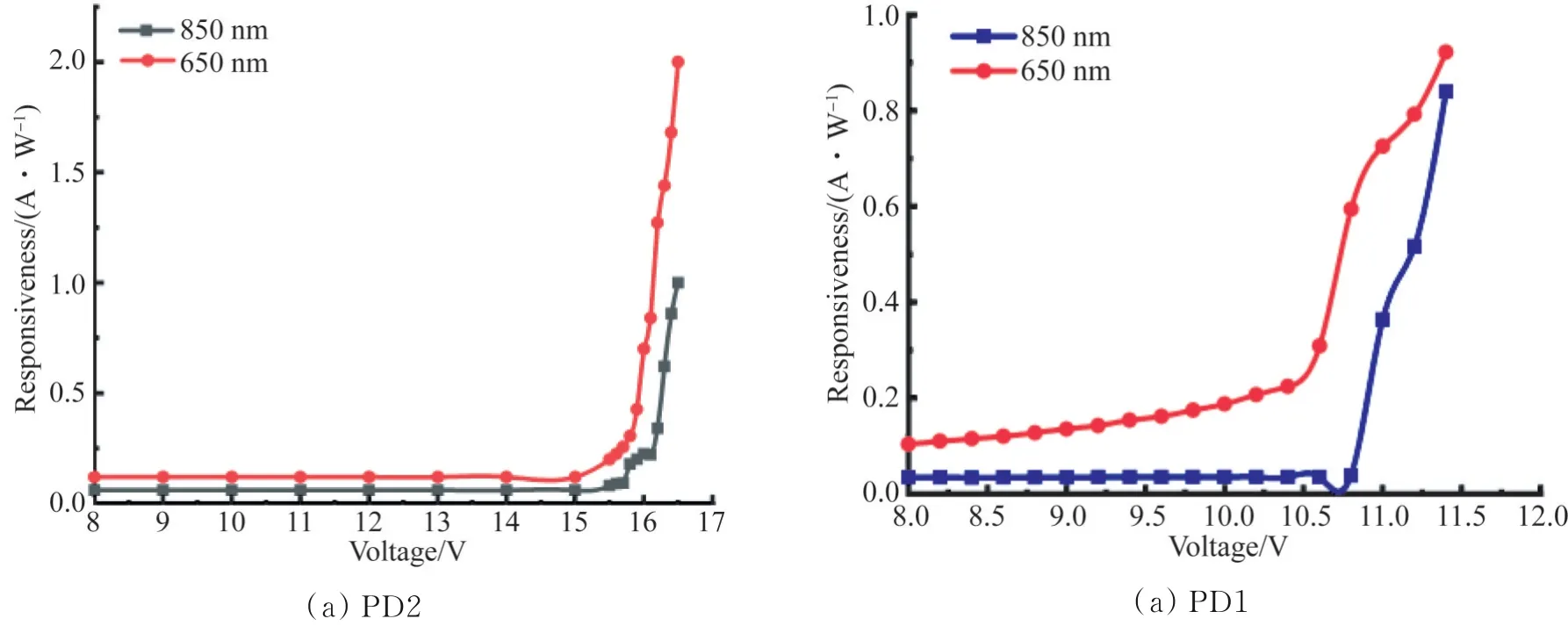

圖19 是對兩款APD的響應度測試曲線。從圖中可以看出,在擊穿電壓點附近兩款APD的響應度明顯上升,且650 nm光均比850 nm光的響應度高。PD2在電壓達到16 V時,650 nm光和850 nm光對應的響應度分別約為0.8 A/W和0.25 A/W。P+/Nwell在電壓為10.8 V時,650 nm光和850 nm光對應的響應度分別約為0.71 A/W和0.39 A/W。

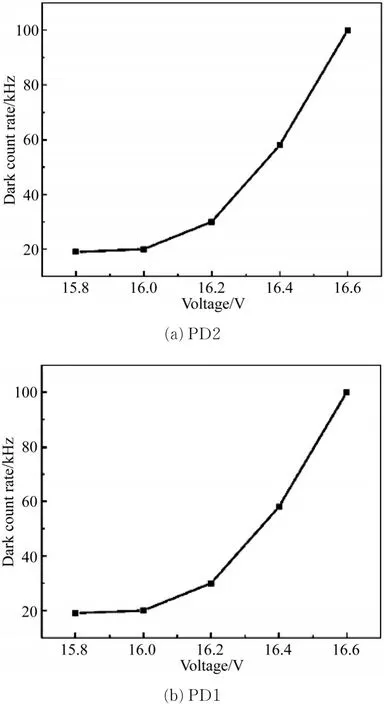

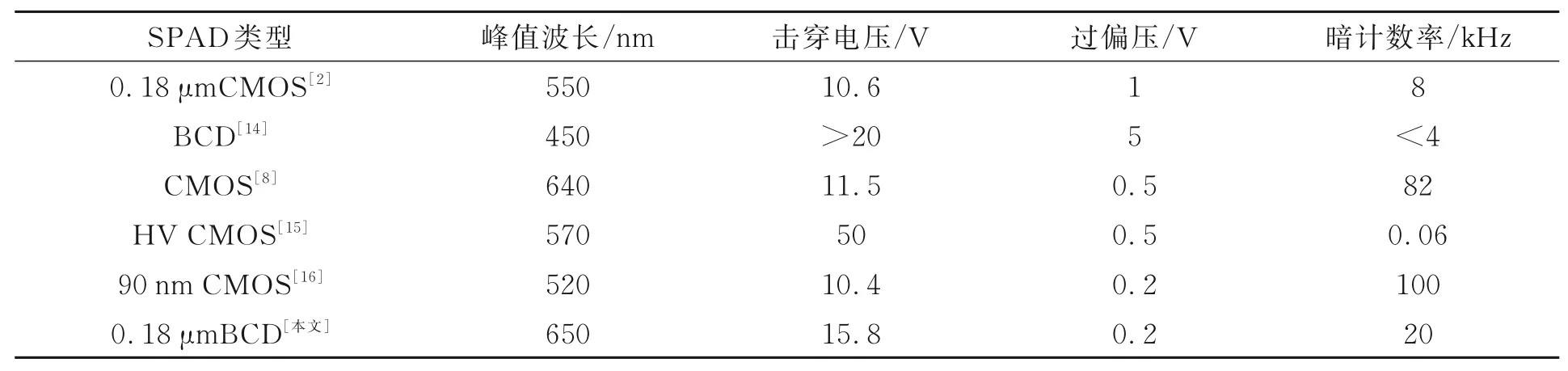

在遮光情況下對APD進行無源暗計數測試,暗計數是APD自身材料缺陷或熱載流子造成的雪崩觸發,會導致APD在沒有光子照射的情況下產生誤計數。在APD兩端施加不同電壓并記錄對應的DRC,測試數據如圖20和表1所示。隨著偏置電壓的增大,DRC不斷增大,P+/Nwell/DNwell結構中當偏壓為16 V時DRC約為20 kHz,P+/Nwell結構中當偏壓為10.8 V時DRC約為60 kHz。

圖19 PD2和PD1的響應度曲線Fig.19 Responsiveness curves of PD2 and PD1

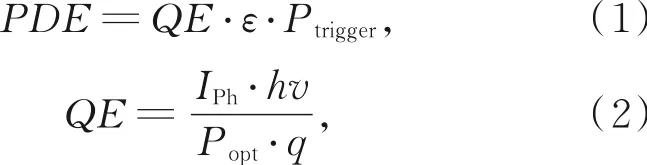

光子探測效率(Photon Detection Efficiency,PDE)是衡量探測器件性能的重要參數指標之一,其數值是探測到的光子數量與入射光子數量的比值,代表了探測器探測光子的能力。影響PDE的主要因素有:(1)有效雪崩區域的量子效率(Quantum Efficiency,QE);(2)幾何填充因子ε;(3)入射光子觸發雪崩的概率Ptrigger。其中ε為光敏面積與整體面積的比值[7]。則有:

其中:Iph為探測器內部產生的光電流,Popt為入射光的光功率,q是電荷,h為普朗克常量,ν代表入射光子的頻率。由式(2)可得響應度R和量子效率η的關系式η=R·1.24/λ。由式(1)可知,PDE與響應度R成正比,而本文設計的SPAD在峰值650 nm處具有較高的響應度(0.8 A/W),因此,在650 nm處應具有較高的PDE。

文獻[2][15-16]獲得了比較低的DRC,尤其是文獻[16],在過偏壓0.5 V下,僅有60 Hz的DRC,但是APD采用高壓CMOS工藝制作,擊穿電壓高達50 V;文獻[15]的擊穿電壓也高于20 V;文獻[2]整體性能都較好,然而其峰值波長在550 nm處,當探測器工作在650 nm處時光子探測概率下降較大。文獻[9]的峰值波長在640 nm,擊穿電壓較小,然而DRC達到80 kHz。文獻[17]有較低的擊穿電壓,但其工藝為90 nmCMOS,價格比較昂貴。綜合比較可得,本文設計的SPAD在峰值650 nm處具有較高的響應度,適 合在波段0.6~0.85μm內工作,擊穿電壓較低。

圖20 暗計數率與擊穿電壓的關系曲線Fig.20 Relationship between dark count rate and breakdown voltage

表1 不同文獻中SPAD參數比較Tab.1 Comparison of parameters of different SPADs

5 結 論

本文提出了一種在0.18μm BCD工藝中設計的圓形P+/Nwell/DNwell結構SPAD和前端淬滅-復位電路。SPAD器件雪崩區形成在P阱和DNW之間,具有更均勻的摻雜分布,邊緣擊穿概率顯著降低,深N阱有效減少P襯底流向雪崩區的暗電流,降低DRC,也保證了較小的縱向渡越時間,提高了響應速度。通過TCAD對P+/Nwell/DNwell結構、P+/Nwell結構和P+/Nwell/BNwell結構進行了建模,并且對3種結構的I-V特性、電場分布和光譜響應特性進行了仿真。仿真結果表明,圓形P+/Nwell/DNwell結構具有較低的擊穿電壓,P+區兩端邊緣處電場明顯降低,降低了邊緣擊穿的風險,且在650 nm具有較高的光譜響應。同時,為了研究有源區尺寸對器件性能的影響,又在6,8,10μm等不同尺寸下分別對3種結構進行了I-V特性仿真,仿真結果表明,隨著有源區尺寸的增大,3種結構的擊穿電壓的節點均有逐漸減小的趨勢,綜合考慮,選取有源區尺寸為10μm的結構進行流片。為實現光電探測器與集成電路的協同設計與仿真,改進了APD光電器件的等效電路模型,設計了主動淬滅復位電路,死時間約為2.6 ns,能夠達到快速探測的目的。基于CSMC 0.18μm BCD工藝對10μm的P+/Nwell/DNwell結構和P+/Nwell結構進行流片,測試表明,650 nm波長的光均比850 nm波長的響應度高,P+/Nwell/DNwell結構在電壓達到16 V時650 nm和850 nm對應的響應度分別約為0.8 A/W和0.25 A/W,以及DRC均優于P+/Nwell結構。由此可見,基于BCD工藝采用高壓深N阱工藝,通過合理地設計尺寸和結構,可獲得工作波段在0.6~0.85μm,且具有較低的擊穿電壓和高響應度的SPAD。本文的研究工作為可見光領域的硅基光電集成的高性能探測器的研制提供技術積累。