基于FPGA的便攜式VI曲線航空電路板測試裝置

袁 榮,張子明,李金猛,劉良勇,周勇軍

(1.中國人民解放軍第5720工廠,安徽 蕪湖 241007;2.安徽省航空設備測控與逆向工程實驗室,安徽 蕪湖 241007)

0 引言

隨著晶體管和集成電路技術的不斷發展,航空電子設備的電路板集成度越來越高,因此對其進行狀態監測和故障診斷的難度也越來越大,特別是在缺乏電路原理圖以及相關資料的情況下,要完成其健康狀態監測與故障診斷更是難上加難,給航空維修單位帶來了很大的壓力[1]。

VI(voltage-intensity)曲線測試是一種不加電的故障診斷技術,在線路節點之間注入一定幅度和頻率的周期信號,在顯示坐標上形成一條電流隨電壓變化的關系曲線,即VI曲線。VI曲線的形狀由被測節點之間的特性阻抗所決定,通過比較好、壞電路板(器件)上相同節點之間的VI曲線,可發現特性阻抗發生改變的節點,其通常為器件故障所引發。對選定的電路節點,激勵條件確定時,其響應是唯一確定的;響應如有變異,意味著電路節點特性的變異,這必然是電路元器件損傷或電路結構變化(短路或斷路)所致,通過這種測試理念與方法可以幫助維修人員快速找出已經損傷或即將損傷的元器件。

目前對VI曲線測試的研究主要還是集中在基于現有設備的測試應用上,包括通過對VI測試海量數據的轉換與壓縮來完成對電路板的自動狀態監測與故障診斷[1]、對復雜機載電路板件進行測試與故障定位[2-3]、針對大型貨架VI設備進行軟件開發實現測試功能[4-5]等。但是以上這些方法主要應用于內場大設備進行電路板故障診斷的情況,針對外場應用的便攜式的VI曲線測試儀雖然也有少量研究[6],但是其激勵源頻率和幅度要預先設置好,還有比較大的技術提升空間,尚不能滿足外場環境測試的需要。

FPGA(field programmable gate array)以其集成度高、開發靈活等特點,滿足航空電子裝備電路板高度集成、結構標準化、功能軟件化的發展要求[7],在航空領域的便攜式設備研制方面得到了廣泛的應用。如某型導彈的快速測試[8]、高速數據采集系統的設計與實現[9]、以及多通道航空總線檢測[10]等。本文提出的便攜式VI曲線電路板測試裝置也是基于FPGA設計開發的。

1 系統結構及原理

1.1 測試原理

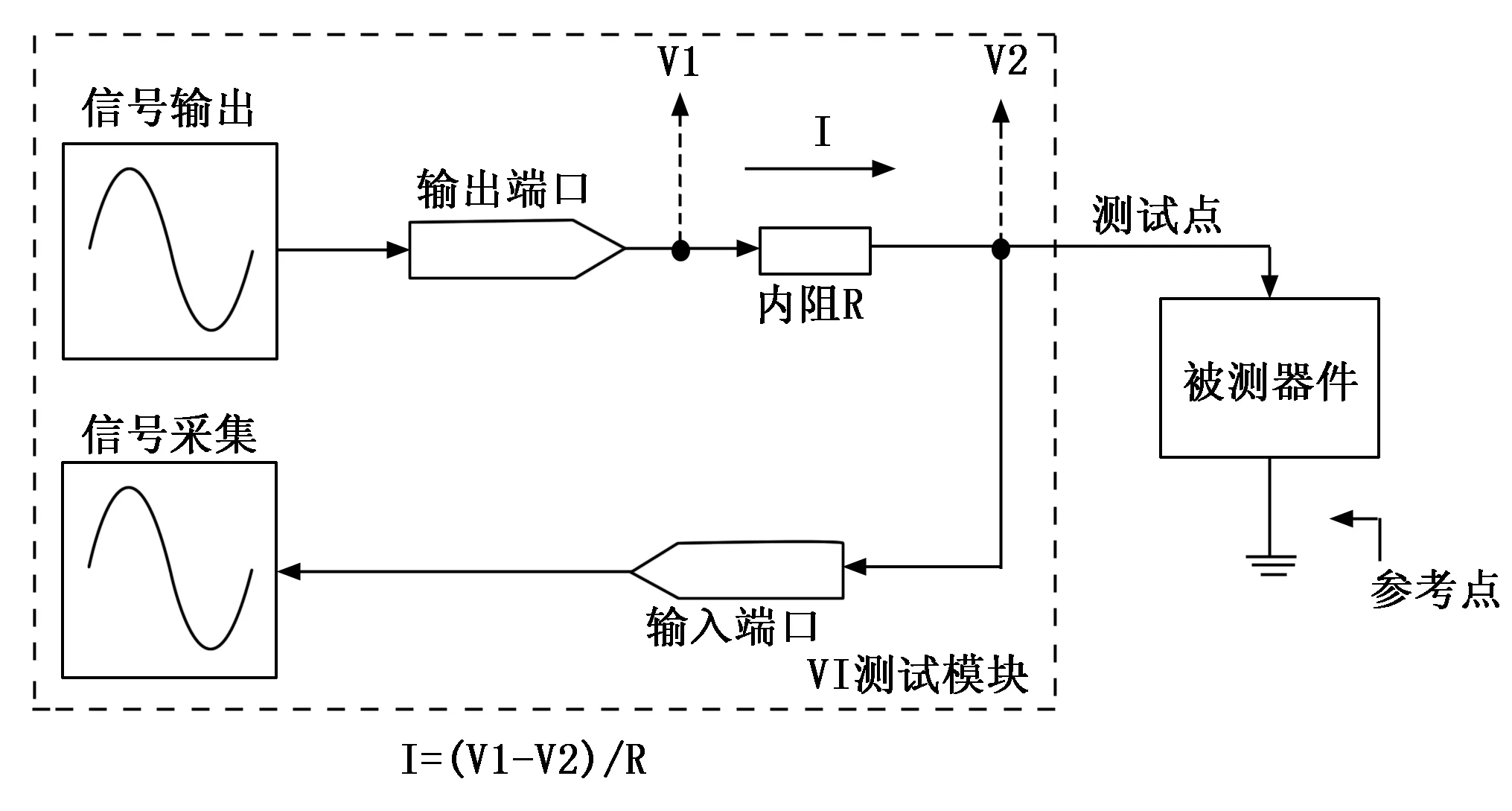

由于電信號的采集工作中往往針對電壓信號進行,為了得到電流信號,可以采用圖1中的方法,在輸出端口和輸入端口之間設置內阻R,這樣在測試器件時會有電流流過,此時輸出端口和輸入端口之間會因為存在內阻而產生壓降,通過計算輸出與輸入之間的壓差,再除以內阻的方法,就可以得到電流信號的值。

圖1 VI曲線測試原理

1.2 系統結構

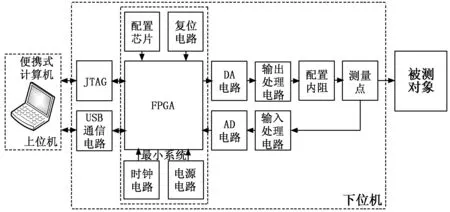

根據圖1所示的測試原理,設計了VI曲線測試模塊的總體框架,包括上下位機兩部分。其中下位機負責正弦激勵信號的產生及濾波輸出、輸出與輸入端口間內阻的配置、信號的回采及處理、與上位機的USB通訊傳輸等,為完成以上功能要求,設置了FPGA核心控制器及其最小系統、DA電路、輸出處理電路、內阻配置電路、輸入處理電路、AD電路、JTAG/CONFIG電路、USB通訊電路等,其中DA電路及輸出處理電路、AD電路及輸入處理電路均設置為2路,為便于2路信號同時測量進行對照;上位機的開發主要集中在用戶軟件上,該軟件用于人機交互和VI曲線的圖形化顯示等,主要的功能包括通過USB接口接收測試模塊上傳的數據、進行電壓電流數據的解算、通過繪制點圖顯示電壓電流之間的函數關系等,目前上位機軟件采用Python語言編程。

VI曲線測試模塊總體框架如圖2所示。

圖2 VI曲線測試模塊總體框架

2 系統硬件設計

2.1 FPGA控制核心及其最小系統

本項目中無論是AD、DA芯片的轉換速率,還是數據傳輸速率均達到了比較高的程度,需要保證微控制器的運行速率;另外因為所含模塊較多,對控制器的IO資源也提出了比較大的要求。在各種微控制器中,FPGA以其并行結構的特點占有很大的速度優勢,同時擁有大量的可配置外設接口,因此經過反復調研論證,選擇FPGA作為微控制器最終選型方案。在本項目中選用CycloneⅢ系列的EP3C5E144C,該芯片在之前的項目中已有比較廣泛的應用,技術成熟,性價比高。FPGA微控制器最小系統用于控制產生正弦激勵信號、采集測量信號、控制與上位機通信等,包括FPGA控制核心的時鐘電路、復位電路、電源電路、配置芯片電路等。

2.2 DA電路

DA電路用于將FPGA控制核心產生的激勵信號由數字型轉換為模擬型,并向測量段發送,產生所需的電壓掃描信號。

由于要產生可調頻率的正弦波,因此本項目對DA轉換速率要求較高,普通DA芯片無法勝任本項目需求。經過調研和試驗驗證,選用AD9764芯片作為DA電路的轉換芯片,該芯片為14路并行DA轉換器,轉換速率可達到125 MSPS,模擬信號輸出峰峰值范圍為600 mV~6 V,完全可以滿足項目要求。

2.3 輸出處理電路

由于AD模塊產生的信號為差分信號,因此需要設計輸出處理電路用于將差分信號調理為單端信號,另外還設計了7階橢圓無源LC濾波器和后級信號放大器,用來擴大正弦波輸出帶寬和信號強度。

2.4 配置內阻

配置內阻兩端的壓降是求出測試點電流信號的重要依據,因為被測元件的阻抗不確定,因此需要根據被測元件的阻抗自適應配置內阻,本項目采用的方式為采用多種阻值并聯的形式,每種阻值串聯跳線帽,通過跳線確定參與并聯的電阻,可靈活改動內阻的大小。

2.5 輸入處理電路

輸入處理電路包括使用衰減和偏移電路對輸入信號進行調理,將差分信號轉換為適合AD芯片處理的較小單端信號形式。

2.6 AD電路

AD電路用于將測量到的電壓信號由模擬型轉換為數字型,并向FPGA微控制器發送。同DA電路,本項目要求AD采樣速率較高,經過調研和試驗驗證,選用AD9226芯片搭建AD電路進行信號采集和轉換,AD9226芯片為12位高速AD轉換器,采用多級差分流水線架構,最大采樣速率達到65 MSPS,可滿足本項目需求。

2.7 JTAG/CONFIG電路

包括用于對下位機FPGA進行開發調試的JTAG電路和最終下位機程序的下載固化的CONFIG電路,其配置芯片選用EPCS16串行存儲器。

2.8 USB通信電路

USB通信電路用于將VI數據傳輸至上位機以供進一步處理,選擇FT245芯片作為USB傳輸協議芯片。該芯片最快傳輸速率1 MB/s,可將8位并行數據與USB信號進行相互轉換,實際是將串口數據按照USB的格式進行發送,免驅動安裝,對Windows7、Ubuntu16.04等各類操作系統的支持度高,開發操作簡便。

3 系統代碼開發

系統代碼開發主要含兩個部分,包括在下位機FPGA運行的代碼以及在上位機運行的軟件。

3.1 FPGA運行代碼

3.1.1 頂層文件

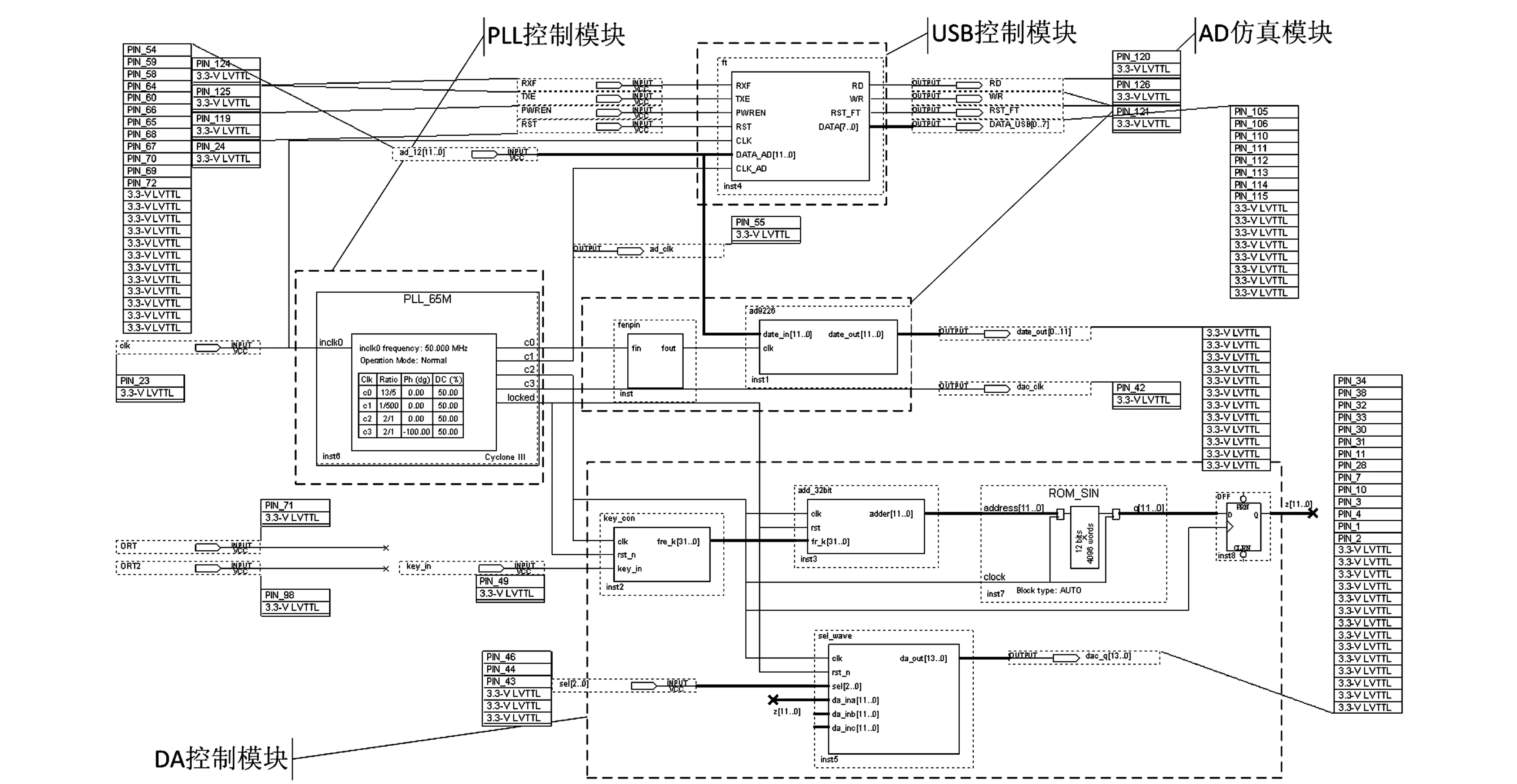

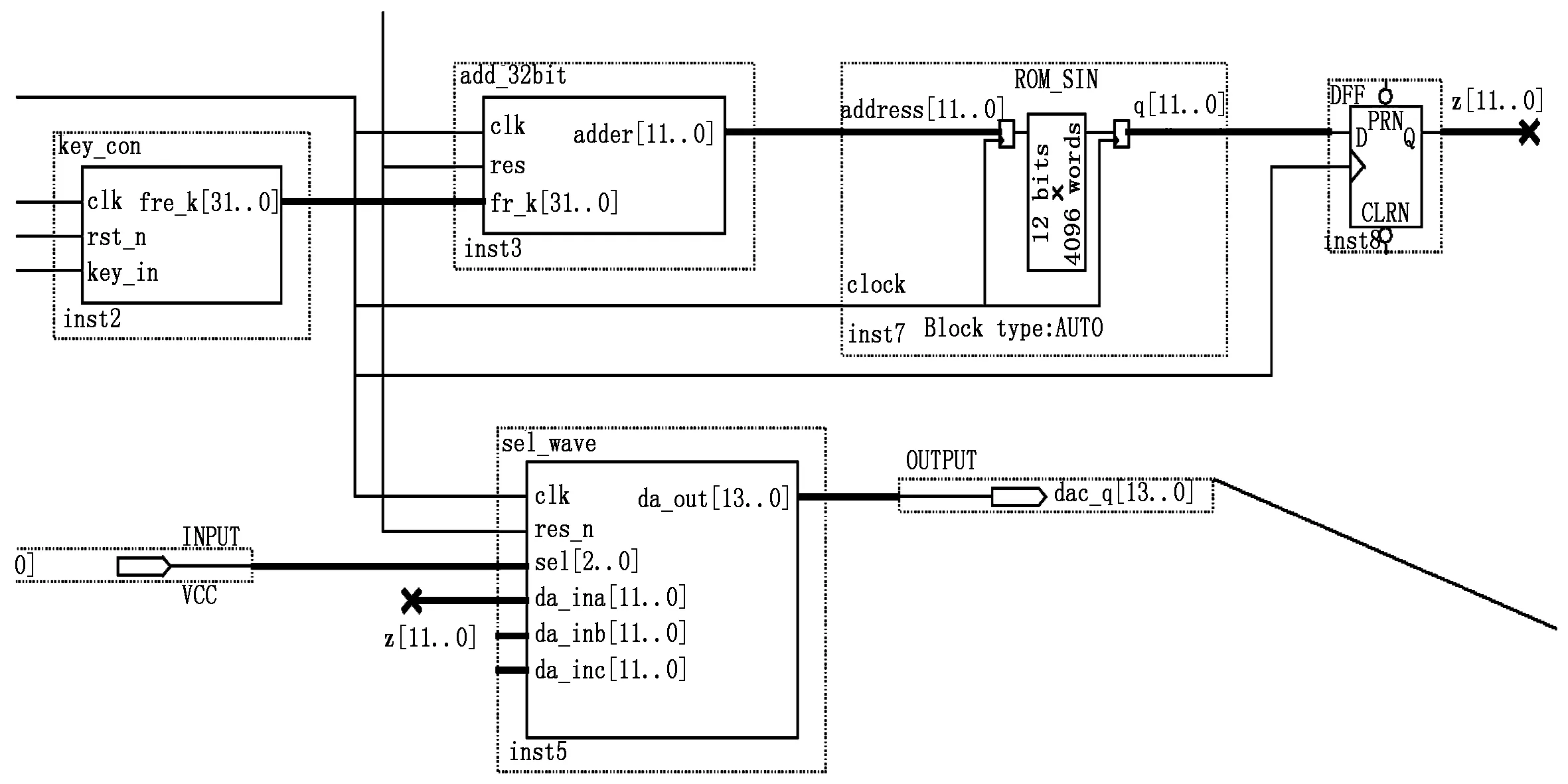

FPGA中運行頂層代碼采用BDF文件,使用Verilog HDL語言編寫各模塊并例化后,在頂層文件中用線相互連接編譯形成。包括PLL時鐘模塊、DA控制模塊、AD仿真模塊、USB控制模塊等,完成激勵信號產生、測試信號采集以及與上位機通信等功能。頂層文件如圖3所示。

圖3 FPGA頂層文件

3.1.2 PLL時鐘模塊

FPGA工作頻率為硬件電路連接的有源晶振產生的50 MHz,而本項目選用的AD和DA芯片分別最高可工作在65 MHz和130 MHz,并且USB芯片的最高傳輸頻率為1 MB/s,因此可以用PLL模塊產生這些芯片工作的頻率。

3.1.3 DA控制模塊

DA控制模塊主要負責將預定波形的信號按照一定的頻率發送給DA芯片,其框架如圖4所示。主要做法是將波形的信號編碼值按照4 096的分辨率保存在FPGA的內部ROM中,通過查表的形式給地址依次輸出對應的電壓值,查表的更新速度決定了輸出波形的頻率。

在本項目中,采用key_con模塊產生地址信號的步進值fre_k,然后add_32bit模塊中將32位計數器通過加上步進值,取計數器的前12位作為地址信號傳送到查找表,然后取出對應的值再送給DA芯片,通過公式(1)可以計算得到輸出波形的頻率FOUT。

(1)

在本例中,FPGA工作頻率為50 MHz,若fre_k取8 590,則可以計算輸出波形的頻率為100 Hz。

3.1.4 AD仿真模塊

該模塊將AD芯片轉換后的數字量輸出,同時配合輸出AD轉換頻率,可以在Quartus軟件的Signal TapⅡLogic Analyzer工具實時查看這些變換的數據,該模塊用于未配備數據傳輸模塊時查看AD轉換是否成功,在調試過程中有比較大的幫助,在AD調試成功,確保轉換功能沒有問題后可以不再使用。

圖4 DA控制模塊

3.1.5 USB控制模塊

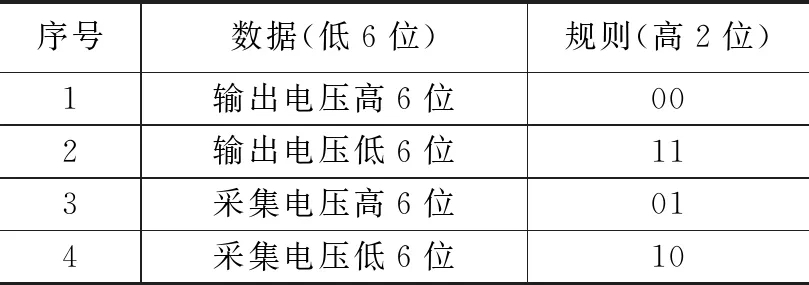

因為FT245一次只能發送8個字節,而輸出和采集的電壓值數字量為12個,在數據傳輸時要準確識別出數據的意義,因此需要編排輸出、采集的電壓值信號,控制FT245按照如表1所示的規則循環發送這些數據。

FT245在發送USB數據時,有以下的控制信號時序關系:在TXE信號為低時,將數據準備好,輸送到FT245的并行口上,將WR信號置高并保持50 ns以上,然后將WR信號置低,在這個邊沿處芯片將并口的數據準備發到USB接口,下降沿后的5~25 ns時間內TXE信號將變為高,此時表示正在傳送數據,在這個過程中不要進行寫操作,即WR保持為低電平,一直到TXE信號變為低,數據發送結束,此時可以將WR信號置高以進行下一個數據的發送。使用FT245進行USB數據發送的控制信號時序見圖5。

表1 數據傳輸編碼規則

圖5 使用FT245進行USB數據發送控制時序

3.2 上位機軟件開發

3.2.1 概況

上位機軟件的主要功能包括接收下位機通過USB發送的數據、通過計算求解出電壓和電流的值、將求解出的值以點圖的形式顯示到計算機屏幕等,在本項目中,使用Python語言編寫了上位機程序。

在Python語言中,可以非常方便地調用matplotlib(類似MATLAB的繪圖)、pyserial(USB形式的串口)等各種資源包,同時具有程序簡潔、代碼量少、開發方便等優點,已經廣泛應用于深度學習乃至人工智能領域,已經成長為最受歡迎的編程語言之一。為了緊跟行業發展動向,同時充分利用其便利因素,在本項目中也開始了對Python語言開發的應用嘗試。

3.2.2 軟件開發思路

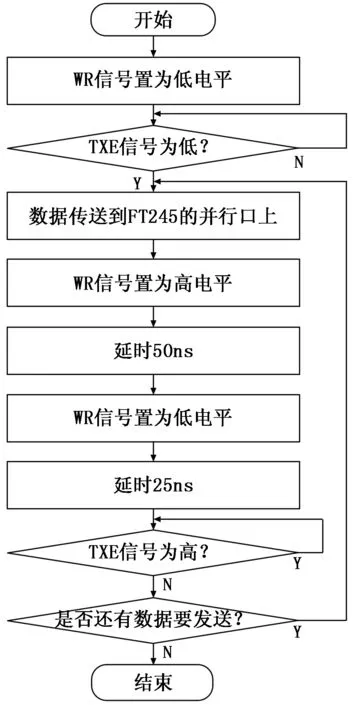

總的下位機軟件流程見圖6所示。

圖6 下位機軟件流程

首先導入“matplotlib.pyplot(plt)”、“serial”等后面需要用到的資源包,然后定義主函數。

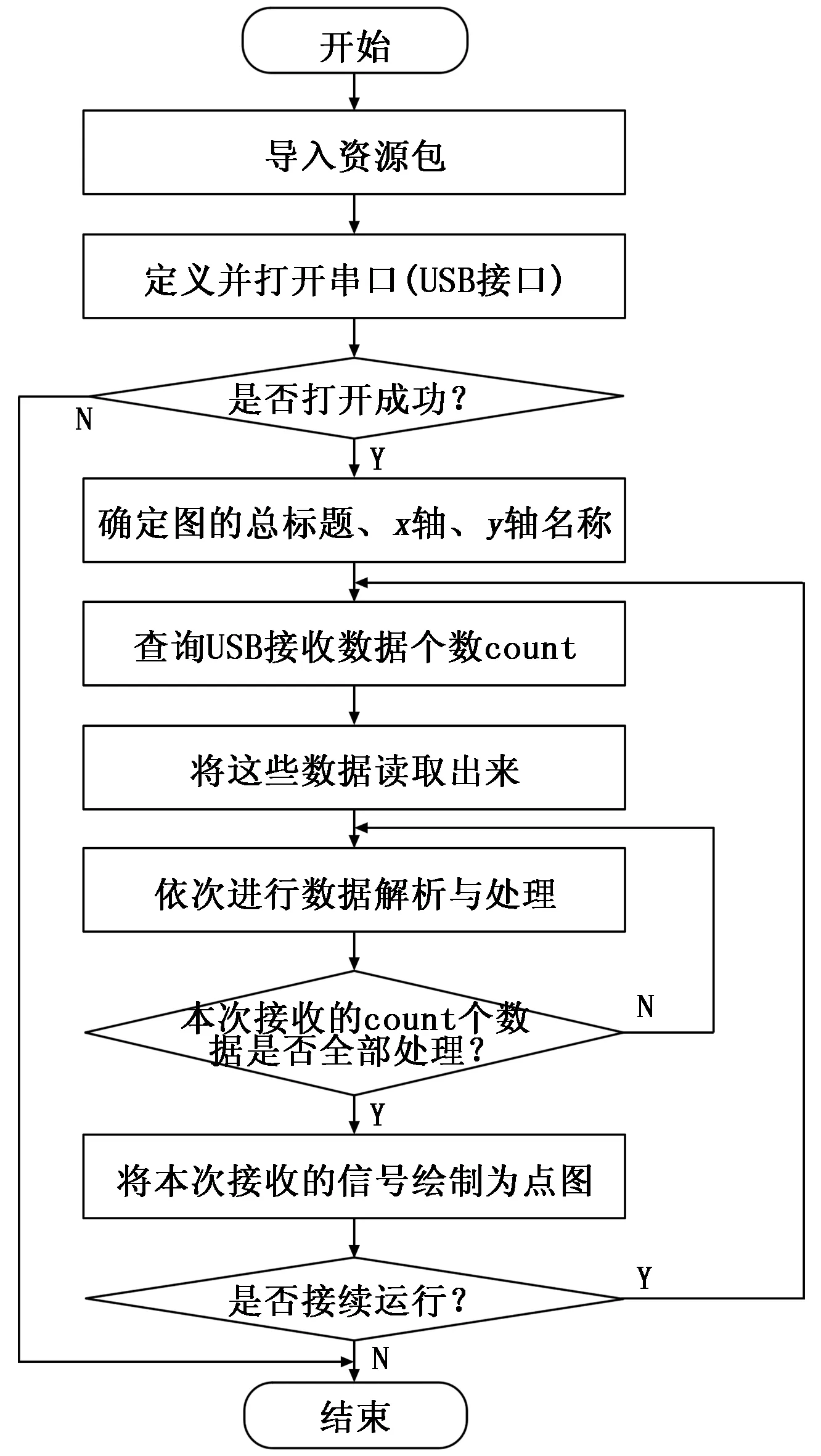

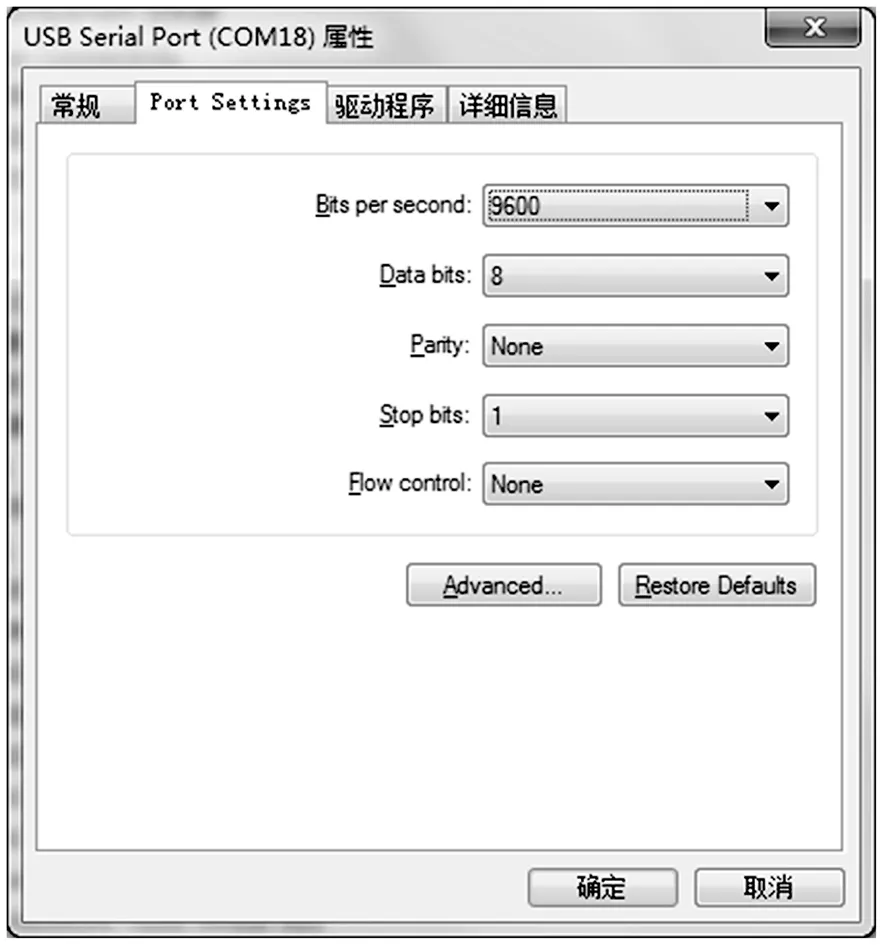

主函數中的最開頭需要定義USB接口,因為FT245芯片將該接口識別為串口(COM口),因此可以使用函數serial.Serial,參數為串口號和波特率,以上信息可以通過資源管理器查看,如圖7所示。然后使用函數serial.isOpen函數判斷串口是否打開成功,并將結果打印顯示。

圖7 串口參數查看

USB接口打開后,開始圖的初始化,包括確定圖的總標題、x軸名稱、y軸名稱等。

然后進行數據接收與處理工作,包括使用serial.inWaiting函數查詢USB接收數據待處理個數count,然后使用serial.read函數將count個數據讀取出來,在這些數據中依次查詢,如果四個連續數據按照表1中的規則依次讀出,則證明這是一組有效數據,分別存入輸出電壓高6位(vout_h)、輸出電壓低6位(vout_l)、輸入電壓高6位(vin_h)、輸入電壓低6位(vin_l)等4個列表中。然后進行數據處理,首先將數據組合得到輸出電壓(vout)和輸入電壓(vin)的數字量值,然后通過公式(2)、(3)分別計算電流、電壓的實際模擬量值。

(2)

v=(vout-2 048)*Voutpp/4 096

(3)

公式(2)、(3)中,vout表示當前輸出的電壓數字量,vin表示當前采集的電壓數字量,Vinmax表示所有采集電壓數字量中的最大值,Voutpp表示輸出電壓的模擬量峰峰值,Rin表示輸出電壓端與輸入電壓端之間的內阻。

電流、電壓模擬量值計算完畢后,通過voltage.append、current.append兩個函數存儲到voltage、current兩個列表中,在這一次USB接收的數據全部處理完后,plt.plot函數確定圖中x、y坐標的單數分別為voltage、current兩個列表中的值,并確定點的形狀、顏色等屬性,最后使用plt.draw函數繪制點圖,并使用plt.pause函數暫停一段時間以接收新的USB數據。

4 實驗結果與分析

分別選擇某電路板上的阻性和容性器件進行測試實驗。

4.1 阻性器件試驗

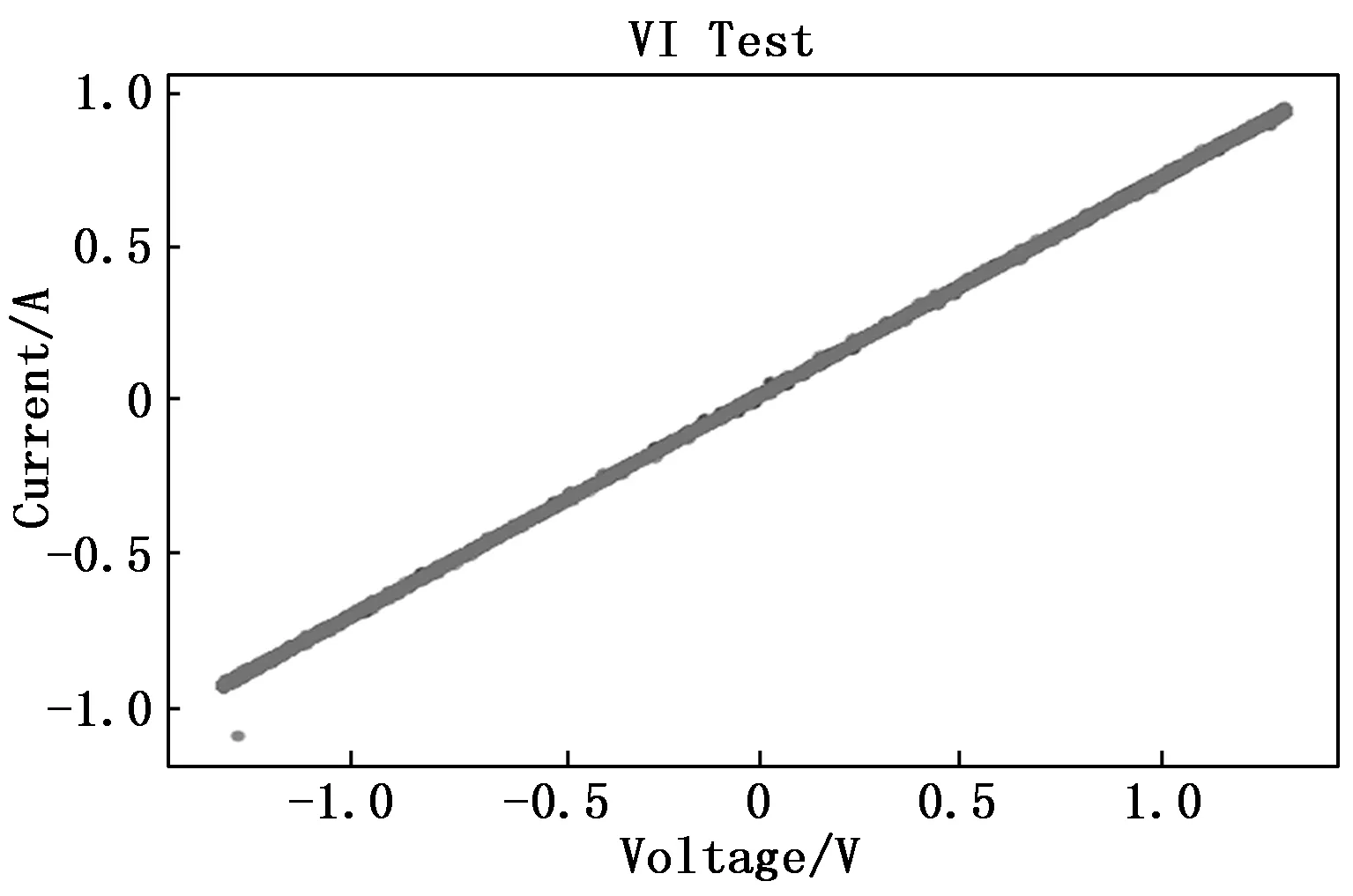

對板件上的某電阻器件進行測試,該器件用于板件上FPGA復位電路中復位信號的限流,一旦出現異常將導致FPGA無法正常復位、異常重啟等問題,板件將喪失功能。

電阻器件的阻抗特性上應該呈現電壓與電流的比例關系。如圖8所示在測試中可以觀察到輸出的圖像顯示R3器件的VI特性呈一條直線,與理論分析結果一致。

圖8 阻性器件試驗VI特性曲線

4.2 容性器件試驗

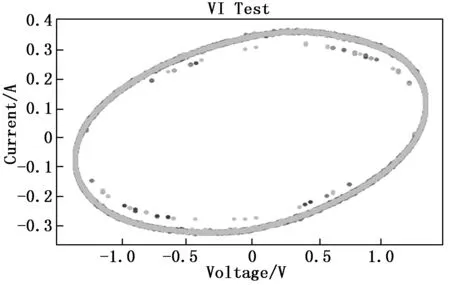

對板件上的某電容器件進行測試,該器件與另一個電容器件并聯放置在LMS1117-3.3 V輸入端,用于5 V向3.3 V電源轉換的輸入端濾波,如果出現異常可能引發電源供電不穩,影響3.3 V的正常輸出,而3.3 V電源在板件中是很多器件的供電來源,如果該電源出現問題板件將發生異常重啟、器件功能缺失等嚴重錯誤。

由于該器件節點處為兩個電容并聯,因此該節點的測試實際為對純容性阻抗特性,電壓與電流變化關系呈積分關系,由于激勵為正弦波,因此如圖9所示,C32器件的電壓電流特性為橢圓形,與理論分析一致。

圖9 容性器件試驗VI特性曲線

5 結束語

本文基于FPGA設計了一種便攜式VI曲線航空電路板測試裝置,裝置結構小巧、操作簡單、便于使用,可應用于在外場環境的航空電路板測試與維修。開發中充分利用了FPGA的靈活性,同時軟件的設計采用了Python語言,軟硬件都具有比較強的發展性,后續的維護非常便利,另外可以針對不同的需求進行升級和開發。