低噪聲、低紋波頭皮腦電信號采集的前端電路

李皓,王宇涵,薛楷瀧,袁燚,李效龍

前言

頭皮腦電信號具有幅度小、頻率低、易受環境噪聲干擾等特點。為了獲取信噪比高的腦電信號,要求模擬前端電路須具有超低噪聲的特點。在腦電信號采集過程中,噪聲源主要是器件本身的噪聲,尤其是閃爍噪聲(1/f 噪聲),該噪聲幅度大且與模擬前端電路的工作頻段重合。為了最大程度降低1/f噪聲的影響,模擬前端電路一般采用斬波穩定放大器以消除1/f 噪聲干擾,同時抑制直流失調電壓。目前常見的幾種斬波穩定放大器主要有套筒式和折疊式。斬波穩定放大器的有源放大部分大多采用兩級運算放大器、套筒式共源共柵放大器以及折疊共源共柵運算放大器等結構。其中折疊式共源共柵運算放大器具有增益帶寬大、低頻增益高、擺幅大、速度高、頻率特性好等諸多優點。由于不同頭皮處所采集的腦電信號幅度不同,要求模擬前端電路的增益須可調[1-2]。

1 電路結構

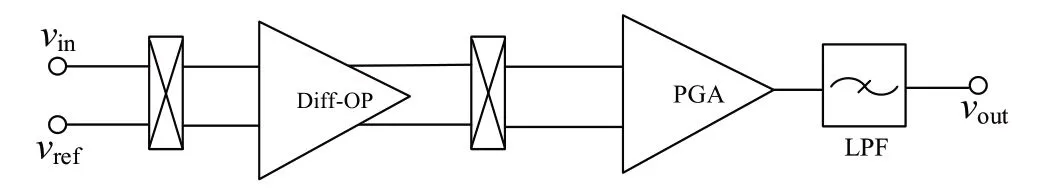

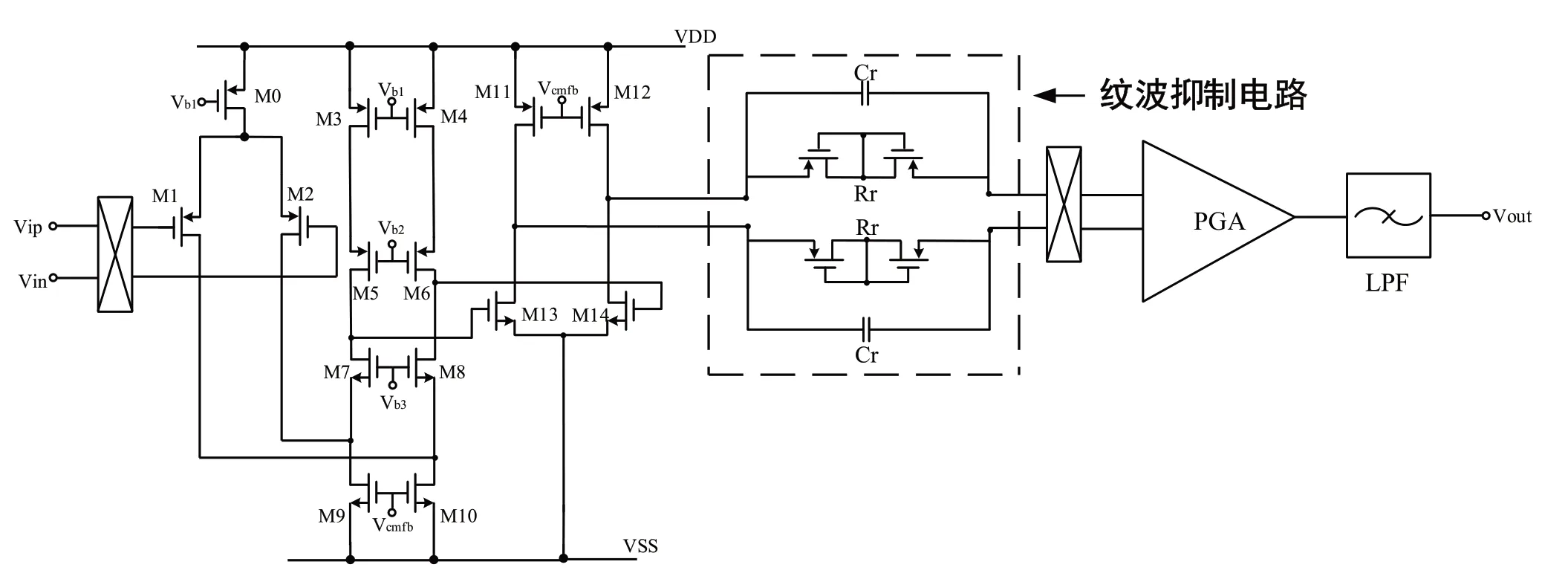

所設計的頭皮腦電信號采集前端電路主要由帶有斬波調制器的前置放大器、增益可編程放大器以及外置低通濾波器組成。電路的整體架構如圖1所示。

圖1 整體電路架構Fig.1 Overall architecture of circuit

1.1 前置放大器

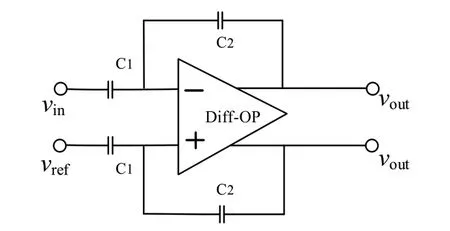

1.1.1 前置放大器電路結構對于極其微弱的頭皮腦電信號,要求前置放大器具有較高的增益、較高的共模抑制比和低噪聲。為了抑制共模信號,前置放大器通常采用全差分結構,如全差分電容耦合電路(圖2)。在理想的條件下,其雙端輸入信號通道完全對稱,雙端輸出信號中的共模分量完全抵消。雖然該電路結構的增益和噪聲性能基本能滿足指標要求,但是由于器件的閃爍噪聲(1/f噪聲)與頭皮腦電信號頻率重疊,低頻噪聲得不到有效抑制,導致信噪比較低,因此需要在此基礎上進一步提高對噪聲的抑制能力[3]。

圖2 全差分電容耦合電路Fig.2 Fully differential capacitive-coupled circuit

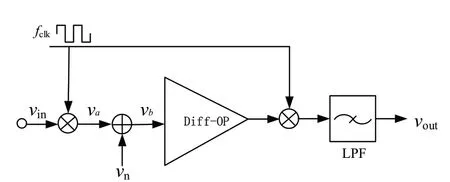

1.1.2 斬波調制前置放大器本設計在全差分電容耦合放大器中引入斬波調制技術來實現對低頻噪聲和失調電壓的抑制。斬波調制技術的過程是調制-信號無失真放大-解調。其信號調理過程是首先將低頻腦電信號通過第一個調制器搬移到斬波頻譜(高于器件閃爍噪聲的轉角頻率)上,然后將搬移的有用信號、低頻噪聲和失調電壓同時放大,再將所放大的信號通過第二個調制器(其調制頻率與第一個調制器相同)。此時低頻腦電信號被解調回原來的頻帶內,而低頻噪聲和失調電壓被搬移到較高的斬波頻譜上。最后引入一個低通濾波器,將低頻腦電信號單獨隔離出來[4]。

斬波調制技術的具體過程如圖3所示。輸入低頻腦電信號Vin首先與第一個調制器(fCLK)混頻,Vin被調制到fCLK的奇次諧波上,實現了低頻腦電信號的頻譜搬移。其輸出信號Va與放大器輸入端低頻噪聲及失調電壓Vn疊加得到信號Vb;Vb經放大器放大,再經第二個調制器(fCLK)混頻得到輸出信號Vc。注意到Vin經過兩次混頻,實現了調制和解調;而噪聲及失調電壓只經過一次混頻,被調制到fCLK上,成為只攜有斬波頻率奇數倍諧波頻率的分量。此時輸出信號須經過后端的一個帶寬略大于輸入信號截止頻率的低通濾波器就可獲得放大后的輸入信號。為保證解調回基帶的低頻腦電信號不會發生混疊,斬波頻率fCLK必須滿足以下關系式[5]:

式中,fCLK為斬波頻率,系數k≥2,BW為信號帶寬,fc為噪聲轉角頻率。

圖3 斬波調制信號流程圖Fig.3 Flow chart of chopper modulation signal

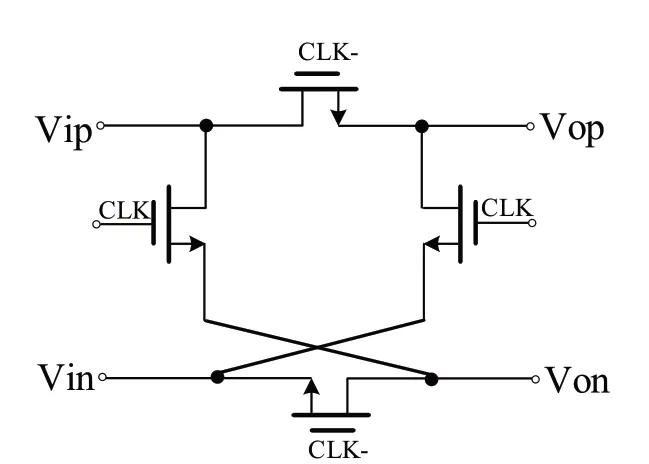

上述調制器電路可以用4 個MOS 管組成的開關電路來實現(圖4)。它是由相位互補的兩個時鐘信號(CLK、CLK-)來控制MOS 管的輸出以實現信號的調制或頻譜搬移。

圖4 調制器電路Fig.4 Modulator circuit

1.1.3 前置放大器有源放大部分電路前置放大器有源放大部分由折疊式共源共柵級和共源級構成兩級全差分放大器(圖5)。折疊式共源共柵級放大器的優點是輸入擺幅和輸出擺幅高,同時開環增益較高。頭皮腦電信號前置放大器的設計指標要求開環增益要大于90 dB,因此需要采用兩級放大器。圖5中前置放大器的輸入端采用PMOS 管以提高輸入信號擺幅;M1、M2、M7和M8構成折疊式差分電路,M9和M10管為折疊式共源共柵的偏置電流肼;M3、M4、M5和M6構成套筒式有源負載;M0是M1和M2的偏置電流源[6-7]。

圖5 前置放大器的輸出抑制紋波電路Fig.5 Ripple suppression circuit of the preamplifier

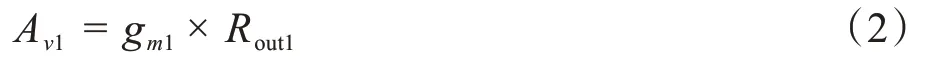

前置放大器有源放大部分第一級的增益表達式為:

其中,gm1是輸入差分管M1、M2的等效跨導。Rout1=gm8·rom10·rom8·gm6·rom4·rom6,其中gm6、gm8分別是M6和M8的跨導。rom10、rom8、rom4、rom6分別是M10、M8、M4、M6交流小信號的輸出電阻。

第二級是共源放大器,M11和M12作為輸入管,M14作為有源負載。第二級共源級輸出也可以提供適當的增益。

其中,gm2 是輸入差分管M13的等效跨導。Rout2=rom11//rom13,rom11、rom13分別是M11、M13交流小信號的輸出電阻。所以前置放大器的總增益為:

由于前置放大器采用了全差分“電容耦合”結構,所以其閉環增益為:

與傳統的兩級運放相比,這種電路結構的優勢是其第一級就能提供很高的增益。因而其共模抑制比CMRR和抑制噪聲性能都有所提高[8-9]。

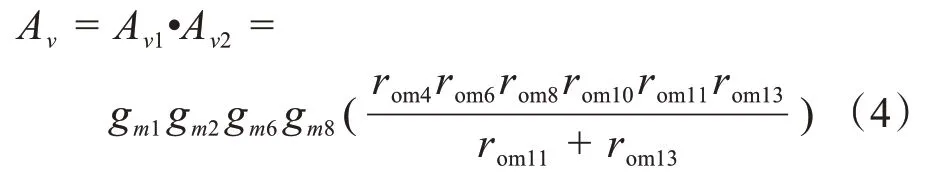

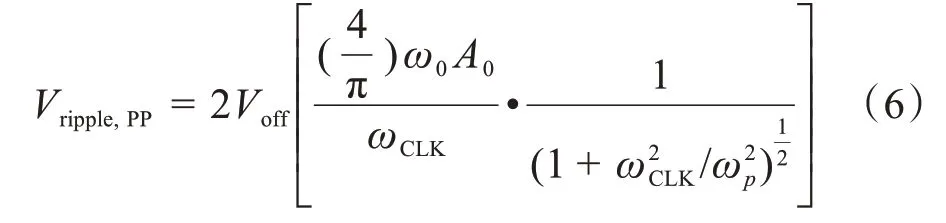

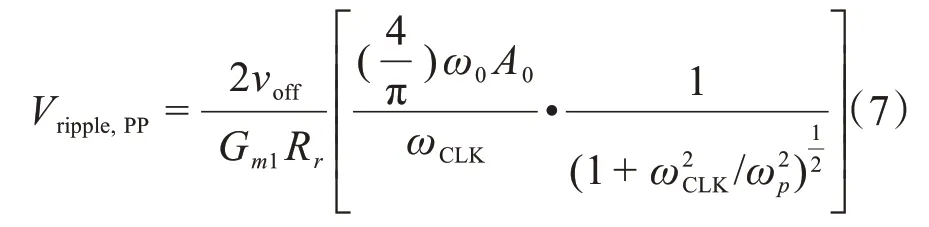

1.1.4 前置放大器的輸出紋波抑制電路當電路中引入斬波技術后,雖然噪聲特性和失調電壓得到明顯改善。但由于前置放大器本身的失調電壓和1/f 噪聲被調制到斬波頻率處后會輸出紋波信號到前置放大器的輸出端。輸出紋波信號會帶來嚴重的信號失真。其輸出紋波可表示為:

其中,Voff為輸出處失調電壓,ω0是前置放大器的閉環帶寬,A0是前置放大器的閉環增益,ω2p是后一級放大器的帶寬,ω2p=ωCLK=5ωo。

為了抑制紋波信號,設計了紋波抑制電路(圖5)。設計思路為:該輸出紋波抑制電路是在前置放大器輸出端接入并聯阻容耦合電路。考慮到版圖面積,電阻一般通過MOS 偽電阻來實現,MOS 偽電阻由兩個二極管接法的MOS管串聯而成。如果電阻大于前置放大器的輸出阻抗,則該阻容耦合電路在低頻下會成為前置放大器的開路。在斬波頻率下,如果電容器的阻抗(在斬波頻率處)小于前置放大器的輸出阻抗,則阻容耦合電路的作用為短路。因此在斬波頻率下,輸出的紋波信號將無法通過并聯阻容耦合電路,達到了抑制紋波信號的目的[10-12]。此時的紋波幅度為:

其中,Gm1是前置放大器的輸出阻抗,Rr是偽電阻的阻值。對于生物信號放大器來說Gm1≈10 μA/V,Rr≈1 GΩ。

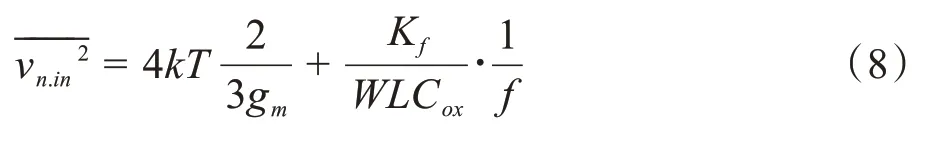

1.1.5 前置放大器的等效噪聲前置放大器輸入端的等效輸入參考噪聲為:

式(8)中等式右邊第一項為由于溝道電阻產生的熱噪聲在輸入端的表現,第二項為MOS管的閃爍噪聲。

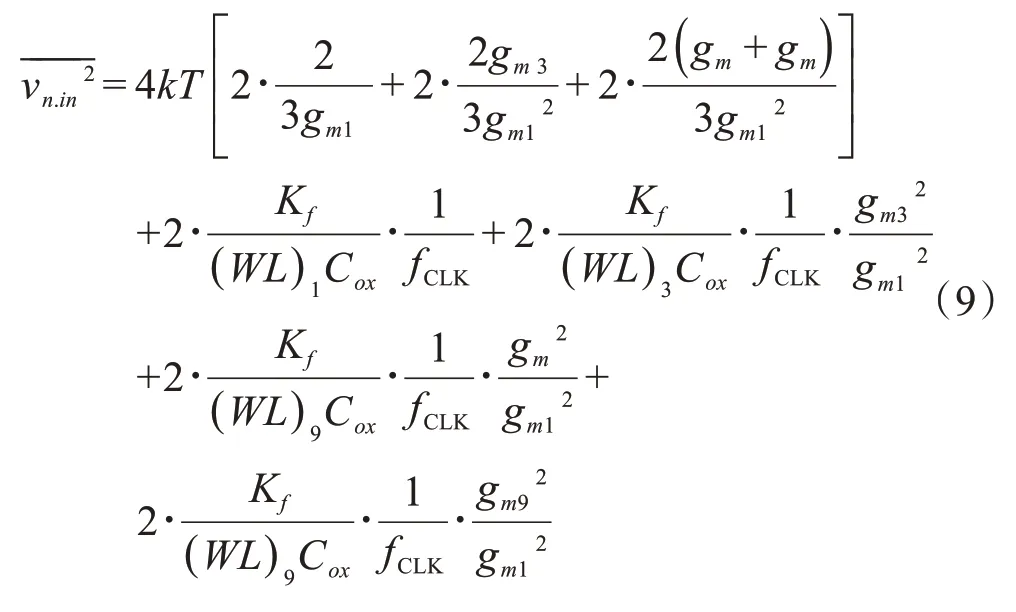

圖5中共源共柵MOS 管(M5、M6、M7、M8)的噪聲可以忽略不計;而第二級電路的噪聲要除以第一級的增益才反映在輸入端,比較小可以忽略;另外,電流源M0的噪聲也可以忽略。所以整個電路在輸入端的等效參考噪聲可以表示為[12]:

式(8)中Kf表示與工藝相關的系數,W、L分別表示MOS 管的寬度和長度,fCLK為斬波處頻率。由1.1.2中分析可知前置放大器的噪聲只在輸出端被調制了一次,因此其信號頻譜會被搬移到斬波頻率奇數倍諧波分量上。由式(9)可得要想減小電路在輸入端的等效參考噪聲,可以提高頻率值,即加大斬波頻率。但是受限于fc?fCLK這一條件,所以在此電路中將斬波頻率設為10 kHz[13]。

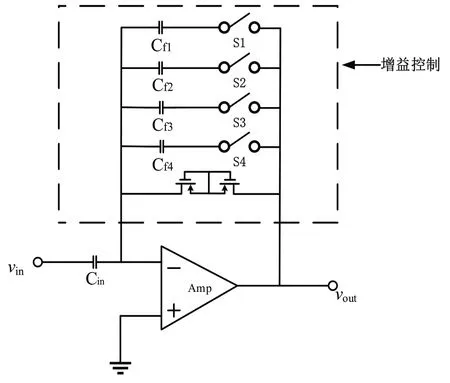

1.2 增益可編程放大器和低通濾波器

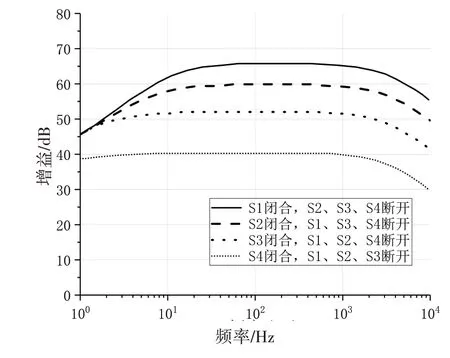

記錄部位、環境以及電極的變化都會導致頭皮腦電信號的幅度出現大范圍的變化,因此需要可變增益放大器對前置電路的總增益進行調節以避免輸出信號發生飽和現象。本設計中的可編程增益放大器如圖6所示,放大部分采用電容耦合結構,其中反饋電容由開關(S1~S4)控制的電容器構成,實現對閉環增益的調節[14-16]。

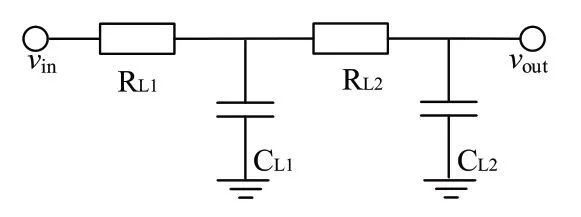

為了濾除頭皮腦電信號中的高頻成分,在增益可編程放大器后面應接入一個外置低通濾波器(圖7)。這里采用了二階無源RC濾波器[17-20]。

2 版圖設計及電路后仿真結果

圖6 增益可編程放大器Fig.6 Programmable-gain amplifier

圖7 低通濾波器Fig.7 Low-pass filter

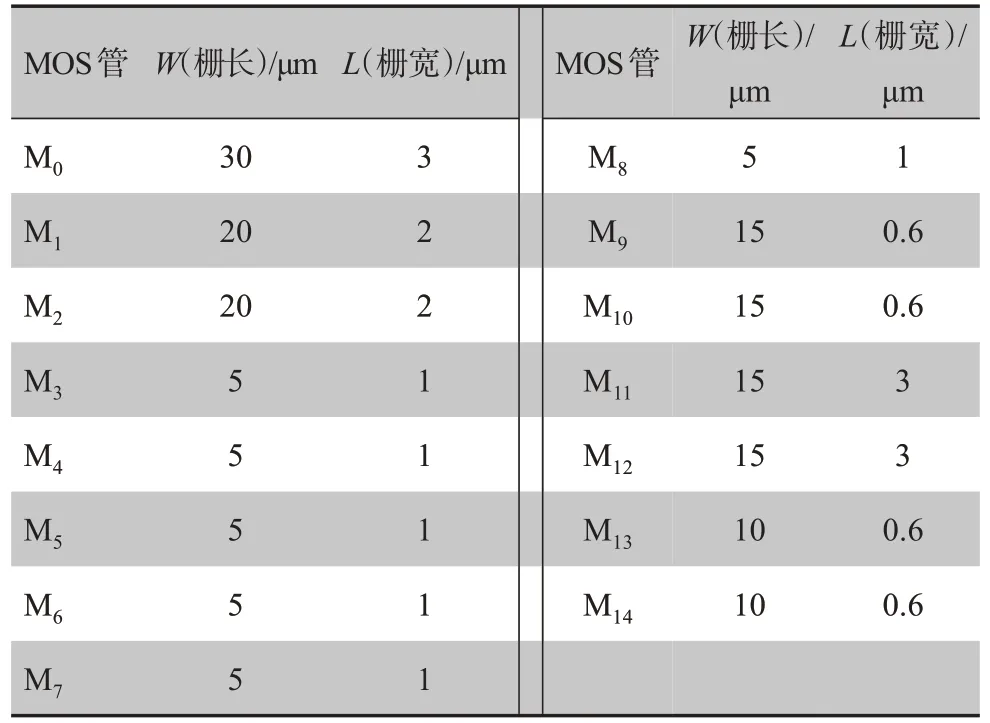

表1 前端電路中MOS管尺寸Tab.1 MOS tube size in front-end circuit

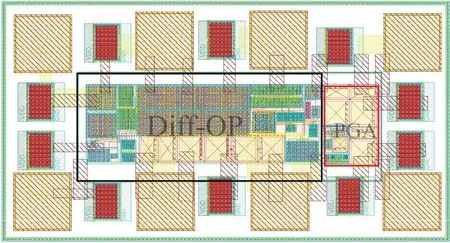

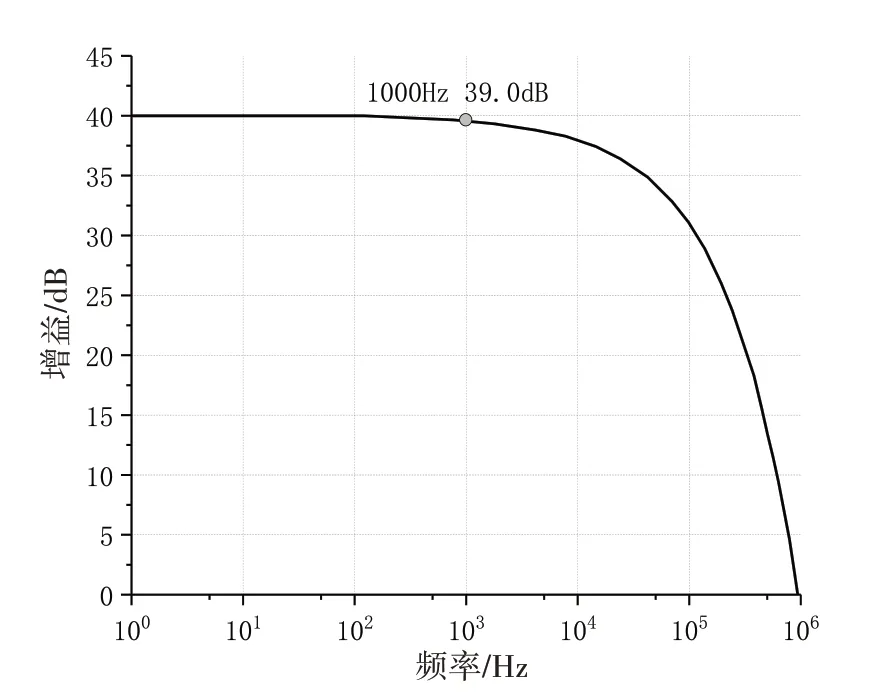

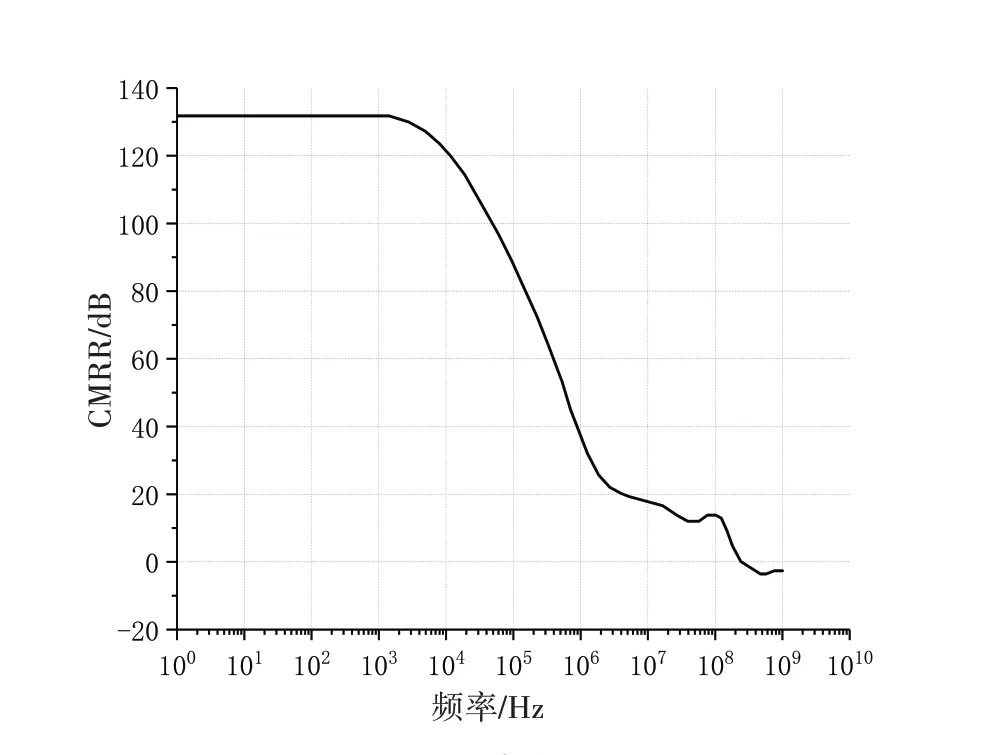

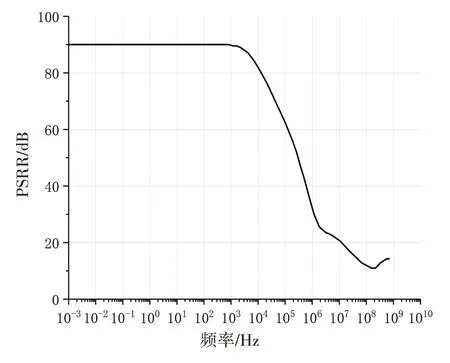

表1、表2列出了圖5~圖7中管子的尺寸和器件參數。所設計頭皮腦電信號采集前端電路版圖如圖8所示,版圖面積為395 μm×120 μm。圖9為前置放大器增益的后仿真結果,前置放大器帶內增益為40 dB。圖10、圖11分別給出了前置放大器的CMRR 和PSRR 的仿真結果,分別為131、90 dB。圖12為增益可編程放大器的增益,在40~65 dB可調。

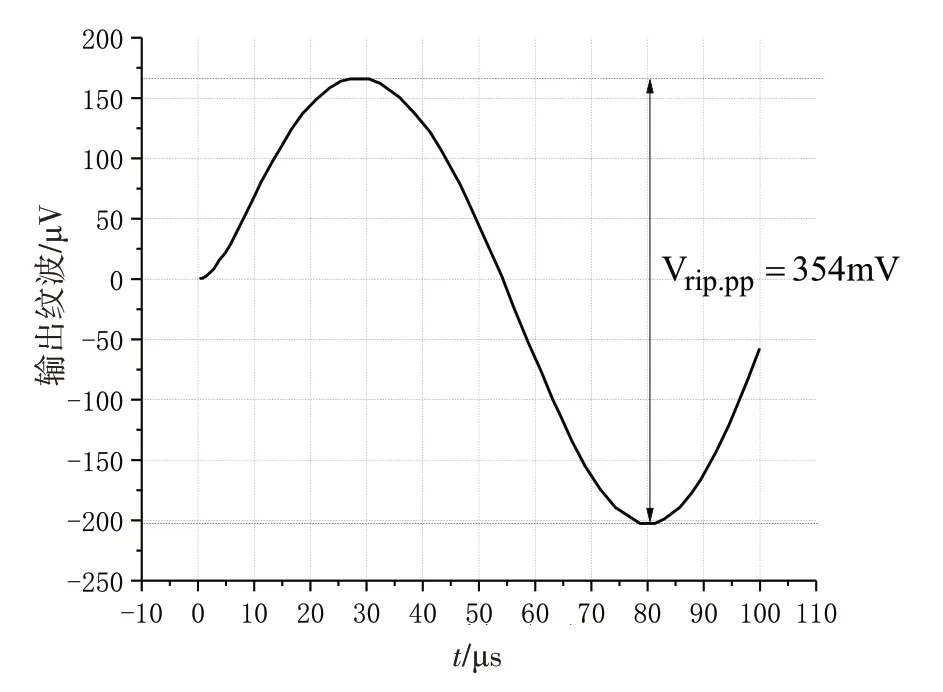

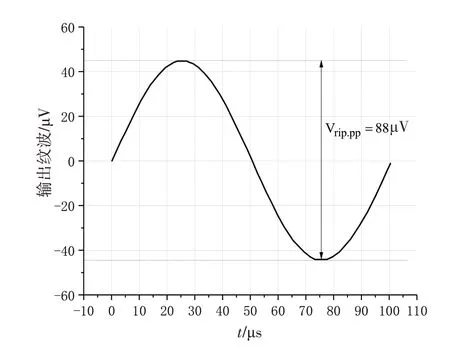

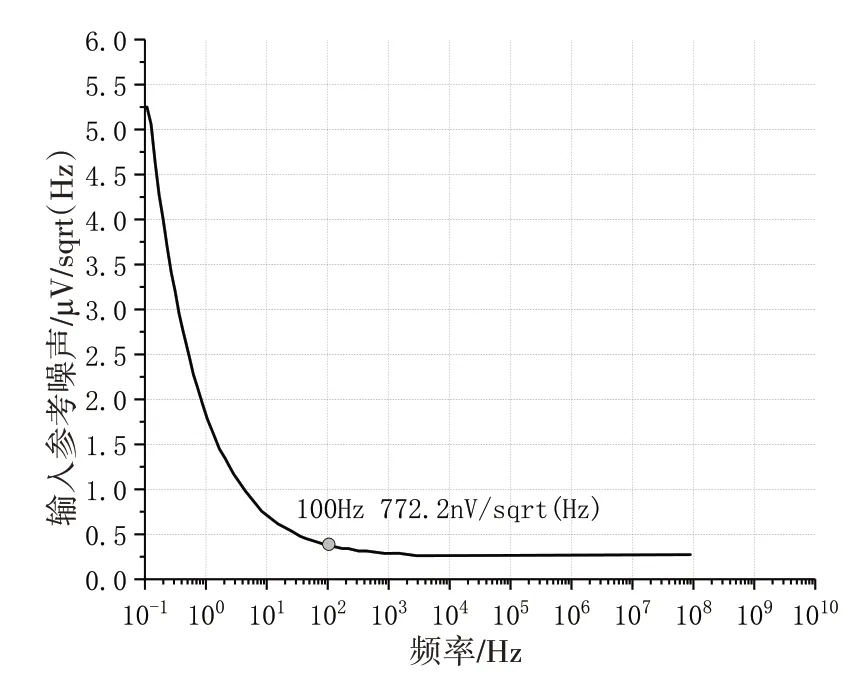

在Spectre仿真中,將前置放大器的輸出失調電壓設為1 mV,使用該失調電壓進行瞬態仿真。如圖13、圖14所示,未加紋波抑制電路的輸出紋波為354 mVpp,具有紋波抑制電路的輸出紋波為88 μVpp,紋波被抑制了400倍。可見該紋波抑制電路對減小前置放大器的輸出紋波有著顯著效果。圖15為頭皮腦電信號采集前端電路的輸入等效噪聲,在0.5~100 Hz頻帶內的輸入等效噪聲為772 nV/sqrt(Hz)@100 Hz。

表2 器件參數Tab.2 Device parameters

3 結論

本文提出一種適合采集頭皮腦電信號的模擬前端電路,由前置放大器、增益可編程放大器和低通濾波器組成。最后仿真結果表明,在5 V 工作電壓下,采用SMIC 0.18 μm CMOS 工藝模型利用Cadence 公司的Spectre 仿真工具對電路進行仿真,實現增益在40~65 dB 可調,電源抑制比90 dB、共模抑制比131 dB、輸入等效噪聲772 nV/sqrt(Hz)@100 Hz。紋波抑制電路對在斬波頻率處的紋波具有400 倍的抑制效果。該前端電路滿足設計指標。

圖8 前端電路版圖Fig.8 Front-end circuit layout

圖9 前置放大器增益Fig.9 The gain of Preamp

圖10 共模抑制比Fig.10 Common mode rejection ratio

圖11 電源抑制比Fig.11 Power supply rejection ratio

圖12 前端電路可調增益Fig.12 Adjustable gain of front-end circuit

圖13 未加紋波抑制電路的輸出紋波Fig.13 Output ripple without ripple suppression circuit

圖14 紋波抑制電路的輸出紋波Fig.14 Output ripple with ripple suppression circuit

圖15 輸入等效噪聲Fig.15 Equivalent input noise