重離子治癌裝置中γ-γ 符合時間測量系統設計

顏俊偉,柯凌云,陳金達,張秀玲,杜成名,楊海波,王長鑫,3,吳俊達,蘇 弘,千 奕,佘乾順,趙紅赟,蒲天磊,孔 潔*

(1. 中國科學院近代物理研究所 蘭州 730000;2. 中國科學院大學核科學與技術學院 北京 石景山區 100049;3. 華南師范大學物理與電信工程學院 廣州 510631)

重離子束治癌是生物醫學與核技術深度交叉和融合的產物。由于重離子具有倒轉的深度劑量分布曲線(Bragg 曲線)和較高的相對生物效應,重離子束治癌技術可以克服常規放射療法的局限性[1-2]。在重離子治癌裝置[3-5]中,12C 束流轟擊靶組織(腫瘤)會引發彈核碎裂產生β+發射體(11C、15O、10C),因此在徑跡末端遇負電子會產生湮滅反應,同時釋放兩個在同一直線上沿相反方向發射的511 keV γ光子。在患者受輻射后立即對該反應空間進行測量,可以測得有效的照射劑量信息[6]。重離子治癌裝置要求采用符合探測技術進行γ-γ 符合測量,能夠從不同探測器的輸出脈沖中挑選相關的時間脈沖,進而確認關聯事件,甄別排除無效事件,提高探測器的探測效率。符合測量系統通過一對相對放置的探測器測量兩個511 keV γ 光子擊中探測器的時間信息和能量信息,并基于時間窗和能量窗的判選,進而獲取符合事件和精確推斷出湮滅位置[7]。能量符合的目的是為了消除正電子發射斷層掃描成像(positron emission tomography, PET)系統中由康普頓散射造成的散射符合事件,時間符合的目的為了消除系統中的隨機符合事件。因此,設計用于重離子治癌裝置的符合測量系統必須滿足高分辨率和高精度時間測量。

時間量在核物理與粒子物理實驗中具有重要意義,時間-數字轉換(time digital conversion, TDC)是時間間隔測量的基本方法之一[8-9],廣泛應用于現代物理測量系統,可采用模擬方法、數字方法以及專用的集成電路實現[10]。采用專用集成電路(ASIC)獲取高分辨率時間間隔測量,如GP2、HPTDC 等專用TDC ASIC 芯片[11],雖然簡化了設計復雜度,但是其開發周期長、通用性差。采用現場可編程邏輯陣列(FPGA)技術,由于其編程靈活性強、精度高、可靠性高、通道多特性,同時擁有豐富的延遲鏈單元、時鐘、觸發器等資源,使其成為實現數字TDC 的主要手段[12]。

傳統的符合測量電路通常采用NIM(nuclear instrument module)機箱、線性放大插件、符合插件等,存在著設計復雜,抗干擾性、測量再現、易操作性和系統升級等方面的不足,探索開發新型的符合測量系統迫在眉睫[13]。本文設計基于Altera 公司Cyclone Ⅴ系列FPGA 實現重離子治癌裝置中γγ 符合時間測量系統,實現高分辨率及高精度的時間間隔測量,本征時間測量精度達百皮秒量級,符合時間譜分辨達1.5 ns (FWHM)。

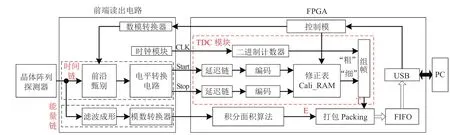

1 符合時間測量系統結構

研制的γ-γ 符合時間測量系統結構如圖1 所示,包括晶體陣列探測器、前端讀出電路和FPGA電路和PC。前端讀出電路包括時間鏈、能量鏈、數模轉換器(DAC)和時鐘模塊組成,其中時間鏈負責處理晶體陣列探測器打拿極輸出的時間信號,產生定時脈沖信號;能量鏈完成電荷信號的濾波成形和模數轉換;時鐘模塊提供FPGA 所需的系統時鐘。FPGA 設計實現了控制模塊、TDC 模塊、積分面積算法模塊、數據打包模塊及通信模塊(USB),其中控制模塊用于配置修正表(Cali_RAM)及控制DAC 的閾值電平。TDC 模塊標記信號的時間戳信息,即通過記錄每個擊中信號發生的時刻,利用修正表對記錄的時間信息進行修正,得到精確的“細”時間,由組幀模塊將“細”時間與“粗”時間測量結果合成時間戳。組幀模塊根據幀格式將時間戳(T)與能量(E)數據打包暫存于先進先出緩沖器(FIFO)中,而后通過USB[14]進行數據傳輸和配置。在PC 上利用MATLAB 編寫分析代碼讀取上傳的數據包,順序提取各個通道的時間和能量信息,基于設置的時間窗篩選符合的事件同時做差處理,得到時間譜。

該系統電路結構簡單,具有較強的靈活性和可擴展性,易于系統升級。

圖1 γ-γ 符合時間測量系統結構框圖

2 符合時間電路設計與實現

圖2 符合時間電路時間鏈和FPGA-TDC 模塊

符合時間電路中時間鏈和FPGA-TDC 邏輯框圖如圖2 所示。光電倍增管打拿極輸出信號為固定的脈沖波形,其寬度、幅度、周期及邊沿特性一致性好,適合選用前沿定時甄別。其中時間鏈采用LEMO 接頭,阻抗50 Ω,交流耦合至由超高速比較器構成的定時甄別電路,同向端是DAC 產生的閾值電平輸入,經甄別給出觸發信號(start/stop)。由于比較器是PECL 電平標準輸出,選用的FPGA的IO 端口為LVDS 電平標準,故電路采用Micrel公司的高速電平轉換芯片SY55855 將PECL 轉為LVDS 電平送給FPGA,提高信號的抗干擾性。FPGA-TDC 設計采用“粗細”時間測量相結合的方法實現。“粗”時間測量采用計數器型TDC構建,分辨率為系統時鐘f2 的周期,實際工作中為了消除亞穩態現象,計數器系統時鐘f2 與f1 有180°的相位差。“細”時間測量單元分為3 個部分:緩沖器和寄存器陣列構成的級聯延遲鏈、編碼邏輯和Cali_RAM 修正模塊。在觸發電平信號通道中插入一條延遲鏈,信號在延遲鏈上傳播,在其到來后的第一個時鐘上升沿進行鎖存寄存器陣列上的電平信號,將輸出的多bit 電平稱為溫度碼。在編碼邏輯中對溫度碼進行二進制編碼,輸出“細”時間結果。考慮到由于器件工藝、布局布線、溫度以及硬件電路等因素影響,延遲鏈單元存在非線性,每個單元延遲時間不一致,從而降低“細”時間測量精度。故在本設計中,通過將修正查找表載入Cali_RAM 來修正非線性以提高測量精度,得到最后的“細”時間,最終輸出“細”和“粗”的時間測量結果,并將時間測量數據按數據幀格式打包暫存于先進先出緩沖器FIFO 中;之后通過USB 數據通信模塊將數據傳輸至PC 機完成后續的處理。

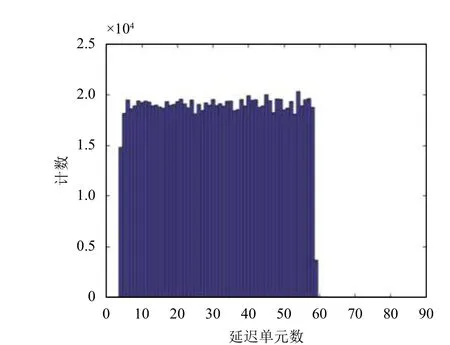

2.1 “粗細”時間測量

圖4 粗時間測量和細時間測量邏輯框圖

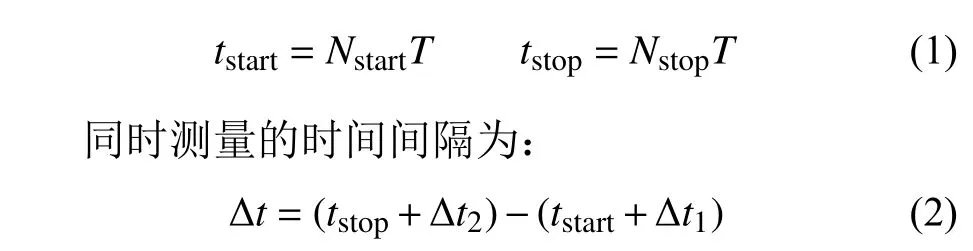

2.2 Cali_RAM 修正表實現

為減少非線性的影響,本文設計Cali_RAM 存儲碼密度查找表進行“細”時間碼的修正。實驗中start 或stop 的頻率與系統時鐘頻率呈弱相關,累計大量數據,將有輸出的延遲單元個數作統計分布圖,即碼密度圖,如圖5 所示。

圖5 碼密度示意圖

在呈弱相關且大量數據前提下,認為信號的前沿到來時刻均勻分布在一個時鐘周期內部,故有輸出的延遲單元的個數的統計差異性取決于自身的延遲時間大小,單元的延時計算為:

把有效輸出的延遲單元對應的總延遲時間計算出來后,將其轉化為二進制并寫入到Cali_RAM中。正常工作狀態下得到未修正的“細”計數編碼值作為Cali_RAM 的地址查找到對應的真實延時值,即可完成時間測量的修正。

2.3 FPGA-TDC 的布局布線

符合時間測量系統采用Altera 高性能Cyclone V 系列。底層架構由4 輸入查找表(LUTs)構成的自適應邏輯模塊(ALM)、存儲器模塊以及乘法器組成。圖6a 為實現延遲鏈底層布線圖,每一級均由ALM 左端的輸入引腳到右端的寄存器輸出。圖6b 為10 個ALM 組成的1 個LAB 單元。ALM是Cyclone V 中最小的邏輯單元,每一個ALM 中包括6 個LUT,4 個可編程寄存器。

圖6 延遲鏈底層布局布線

3 性能測試與討論

3.1 TDC 的本征時間分辨

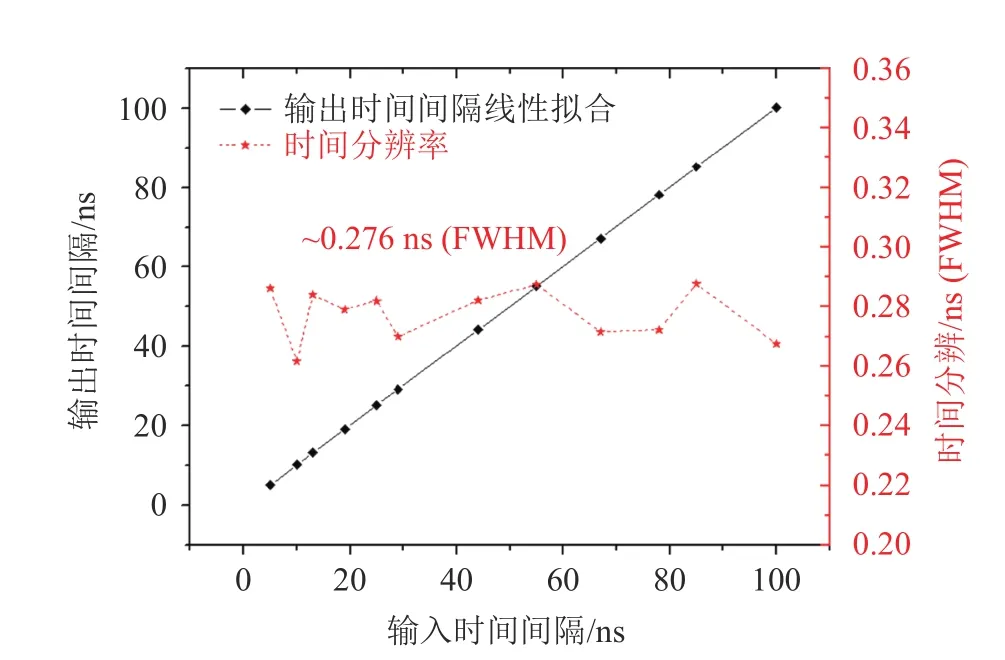

通過基于電纜延遲方法的延遲時間測量來研究定時測量的精度[15]。電纜延遲方法旨在消除信號發生器本身的時間抖動:輸入大量延遲時間固定的成對快脈沖信號作為觸發信號,測量其時間間隔,將測試得到的數據進行統計分析,得到固有時間分辨。利用Tektronix AFG3252 雙通道信號發生器模擬探測器輸出信號,在同樣的輸出脈沖頻率和恒定的室溫下,采用不同長度的同軸電纜,選擇固定延遲時間為10 ns 進行時間間隔的測量,經過統計分析使用高斯擬合[16]方法得到FPGA-TDC 的時間分辨。固定的線纜延遲時間下測得時間分布,分辨為255 ps(FWHM),如圖7 所示。輸入不同延遲時間測得FPGA-TDC 的線性及分辨好于276 ps (FWHM),如圖8 所示。

圖7 固定延遲時間的分布圖

圖8 不同延遲間的線性擬合及均方根值

3.2 聯合測試性能

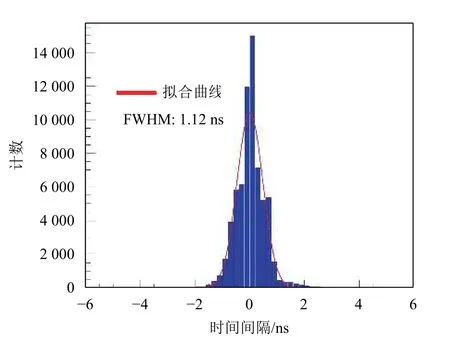

γ-γ 符合時間測量系統聯合測試實驗裝置如圖9 所示。每個探頭采用H8500 耦合LYSO 晶體陣列組成,LYSO 陣列用白色的特氟龍膠帶和黑色膠帶避光包裹起來,并連接到H8500C 光電倍增管上。在每個光電倍增管之后,采用DPC 橋式電路通過LEMO 電纜連接到符合時間測量系統板上[17-18]。 USB 電纜將數據傳送到PC 進行后期數據分析處理。其中的探測器晶體陣列采用由22×22個2 mm×2 mm×15 mm LYSO 晶體條組成,在950 V的正高壓偏置下,H8500 的增益高達106。光電倍增管打拿極輸出信號作為時間信號,用于符合測量。測得有效符合事件時間分布,系統時間測量精度優于1.12 ns (FWHM),如圖10 所示。統計分析有效符合事件得到的LYSO 晶體陣列位置映射散點圖清晰,如圖11 所示。

圖9 γ-γ 符合時間測量系統裝置圖

圖10 符合時間間隔的時間譜

圖11 LYSO 陣列晶體位置映射圖

4 結 束 語

本文設計并實現了一種用于重離子治癌裝置的γ-γ 符合時間測量系統,該系統具有結構簡單、易實現、低成本的特點,可方便實現通道數的擴展,且各個通道間獨立。經過試驗測試,本征時間分辨好于276 ps (FWHM),具有良好線性。LYSO 晶體陣列構成的符合測量系統對511 keV γ 射線的測試,時間測量精度優于1.12 ns (FWHM),略好于文獻[19]提出的多相時鐘測得符合時間精度。而且晶體陣列位置映射散點圖清晰,能夠滿足γ-γ 符合時間測量系統的研究和測試需求。