基于ZYNQ 的高速數據采集系統設計

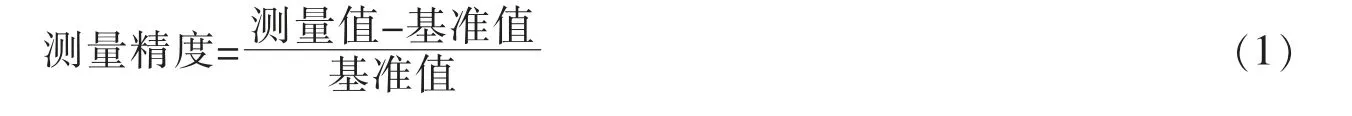

張雪皎,陳劍云

(華東交通大學電氣與自動化工程學院,江西 南昌330013)

隨著電網中非線性負荷用戶的不斷增加,電能質量問題日益嚴重。 高精度數據采集系統能夠為電能質量分析提供準確的數據支持,是解決電能質量問題的關鍵依據。 通過對比現有高速采集系統的設計方案,主控電路多以ARM 微控制器搭配AD 轉換芯片、ARM+DSP 搭配轉換芯片以及FPGA+DSP 搭配AD 轉換芯片的架構方式[1-5]。 ARM 有著良好的決策控制特性,在工業控制領域被廣泛應用,但其數據處理速度慢,不能滿足系統的實時性。 由于DSP 的串行指令流特性,復雜數據處理只能在低速系統中進行。 FPGA 的全可編程和并行數據處理特性使其在數字信號處理領域越來越受到青睞,但是對系統的決策能力較弱[6-10]。 同時,ARM 和DSP,FPGA 與DSP 之間通過低速工業通信接口(SPI、Mcbsp 等)或者采用處理器外部總線接口連接多芯片的結構,復雜化了板級電路設計,芯片間頻繁通信難以保證系統的穩定性[11-12]。

對此,設計一種基于ZYNQ 的數據采集系統,ZYNQ SOC 整合了ARM 雙核cortext-A9 處理器和Xilinx7系列FPGA 架構。 片內集成高度定制的AXI 互聯和接口形成兩個部分之間橋梁,加速了各模塊間的通信且加強了系統的穩定性。利用FPGA 的硬件可編程特性設計出與高速AD 連接的接口控制器,調用AXI_DMA官方硬核IP 可直接將采集數據搬運至ARM 的DDR 中進行存儲。 ARM 驅動串口或者HDIM 口完成數據顯示,執行系統的整體決策。 經過對某變電所電能質量分析,發現穩態下電網高次諧波為60 次左右,系統選用的AD7606 采集卡采樣頻率為200 kHz,8 通道同步采集,分辨率為16 位,采集精度和速度都能滿足數據采集系統設計要求,實現信號的模數轉換。 相對ZYNQ 自帶XADC 的12 位位寬、1 MHz 采樣率AD7606 有著更高的轉換精度。

1 數據采集系統的整體設計

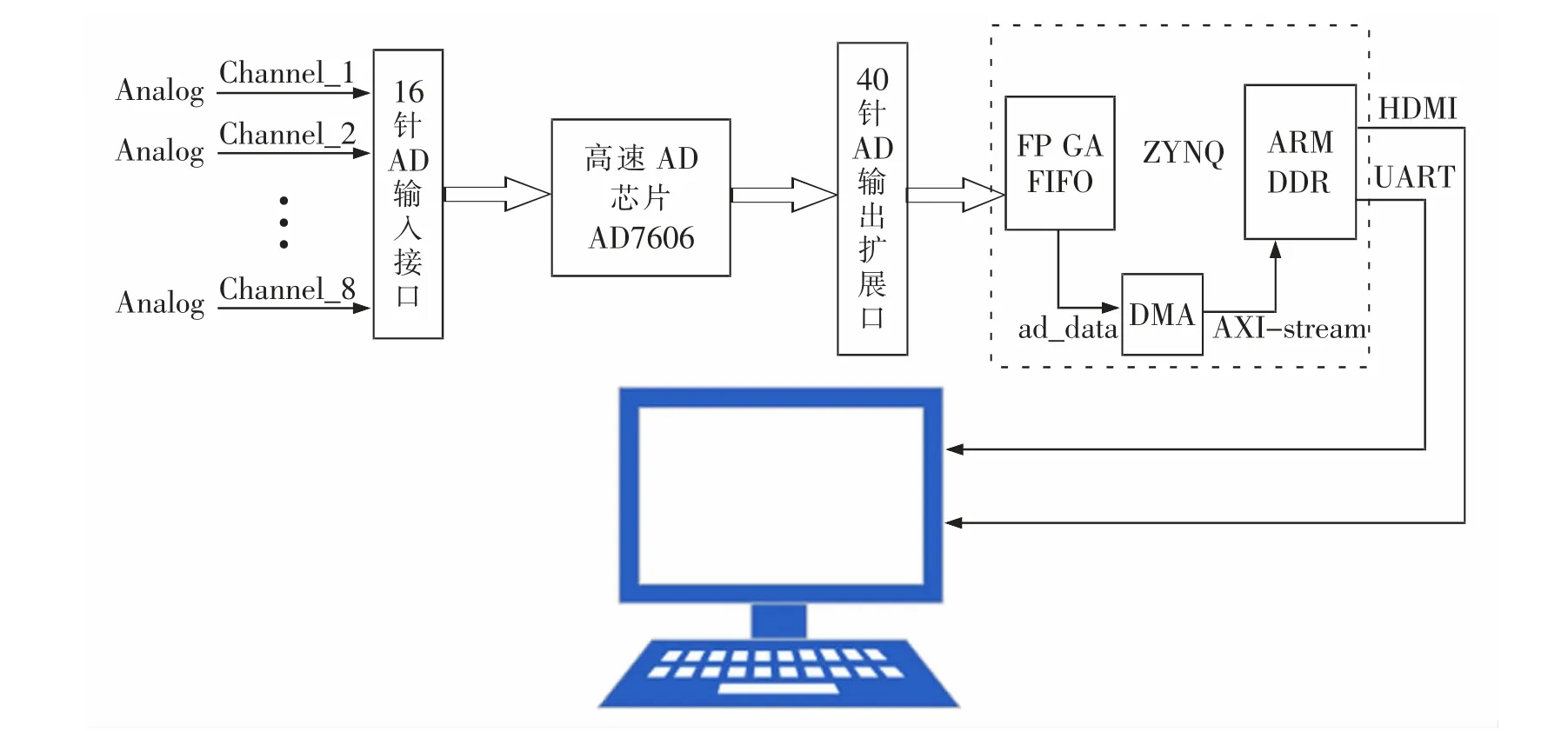

圖1 為系統的整體設計簡圖,AD7606 采集卡輸入端引出了16 針接口, 分別用于8 通道連接外部模擬信號線路的VP 和VN。 模擬信號進入AD 采集芯片內,經過模擬多路復器輸入轉換電路完成模擬信號到數字信號的轉換。系統通過40 針擴展口實現AD7606 與ZYNQ 的高速通信。接口位于ZYNQ 的PL 部分,采用Verilog 代碼編寫接口控制器程序實現AD 采集控制功能后封裝為IP 核,主要設計包括AD 的復位、時鐘、采樣率、片選、FIFO 數據緩存器以及AXI 協議例化。 調用Xilinx 官方IP 核AXI-DMA 將PL 數據傳輸至PS 的DDR 存儲器中。ARM 驅動URAT 或者HDMI 端口將數據傳輸給終端顯示出來。AD 控制器先將采集數據緩存到FIFO 中,從FIFO 中讀出數據后轉換為AXI-stream 流數據格式,如此可以加快數據處理速度,降低數據對時序的影響,系統采用AXI-stream register slice 模塊提升接口時序。 系統采用異步時序設計,ADC 配置時鐘頻率為50 MHz,AXI 總線時鐘為100 MHz,數據顯示時鐘為150 MHz,按照輸入到輸出倍增的方式設置時鐘,可有效防止緩存模塊的數據溢出。

圖1 數據采集系統整體設計圖Fig 1 The overall design of the data acquisition system

2 數據采集系統的硬件設計

2.1 ZYNQ 簡介

ZYNG 是Xilinx 推出的新一代(all-programmable system-on-chip,SoC)全面可編程片上系統。 本質特征是組合了一個雙核ARM Cortex-A9 處理器,簡稱PS 和一個傳統的現場可編程門陣列(field programmable gate array,FPGA)邏輯部件簡稱PL[13]。 芯片集成了AMBA AXI4 互聯,內部存儲器,外部存儲器和外設。 外設主要包括USB 總線、以太網、SD 接口、UART 接口、HDMI 口、GPIO 口等[14-15]。具有高達6.25 MHz 的邏輯單元以及766 MHz 的內部時鐘,能夠實現硬件加速和可擴展性,充分滿足了系統設計的實時性和高精度。

2.2 AD7606 控制器設計

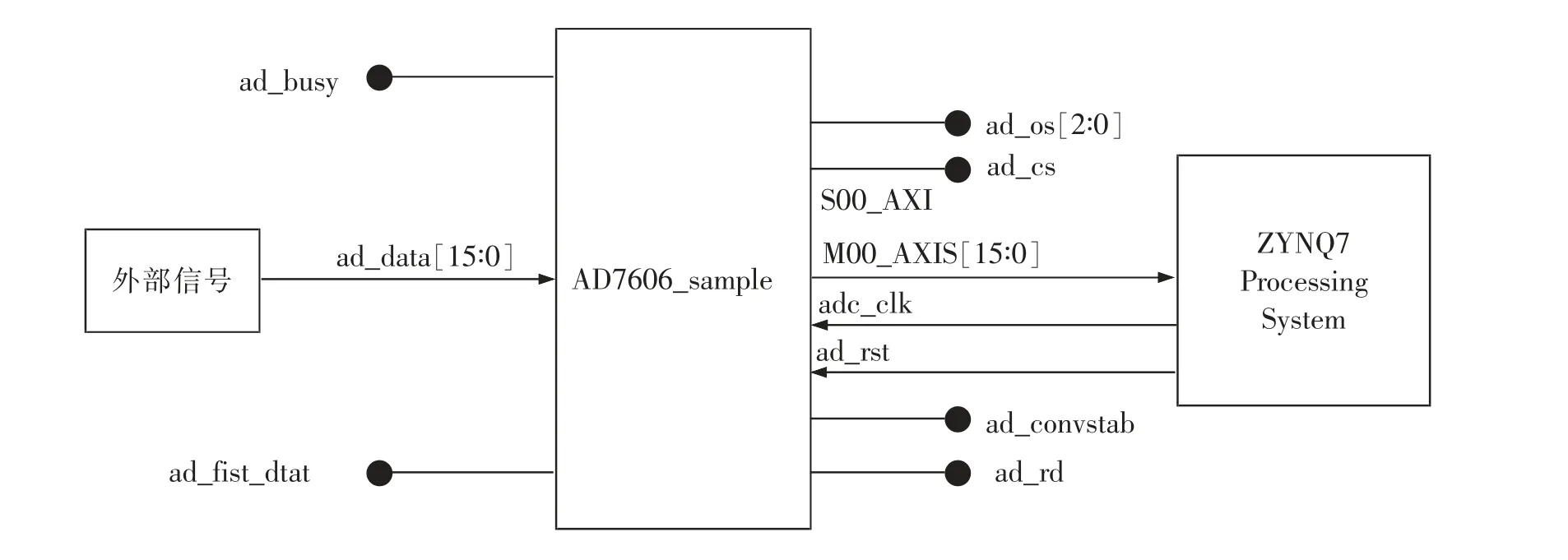

AD7606 采用+5 V 單電源供電,片內集成輸入放大器、過電壓保護、二階模擬抗混疊濾波器、模擬多路復用器、16 位200 kbps SAR ADC 和一個數字濾波器,2.5 V 基準電壓緩存以及高速串行口和并行口,可實現8 通道同步采樣,所有通道均以高達200 kbps 的吞吐率采樣[16]。 AD 控制器如圖2 所示,外部信號通過ad_data[15∶0]端口進入AD 控制器。 未連接的端口采用Verilog 代碼編程控制,根據時序特性設計轉換過程,ad_convstad 端口信號上升沿啟動時8 通道同步采樣,端口ad_busy 為高電平時表示信號正在轉換,當端口ad_busy 信號為下降沿時表示ad_rdd 讀信號端口可以啟動,控制器可讀取數據總線中8 個通道的采集數據。ad_cs 端口控制數據讀片選。 ad_os 為AD 內部數字濾波器采樣倍率選擇端口,共有8 種倍率選擇,控制器可以通過此端口選擇是否使用濾波器,以達到更高的測量精度。 系統通過DMA 將ADC 采集數據傳輸到DDR中,端口M00_AXIS[15:0]為數據輸出通道接口,傳輸數據為流式數據,在設計時需要將ADC 數據轉換為AXIS 流數據。由于ADC 時鐘與AXIS 的時鐘頻率不同,需要在ADC 中添加FIFO 進行跨時鐘域處理,起到緩沖的作用,AXIS 時鐘頻率是ADC 時鐘的兩倍,所以不會發生數據溢出的情況。 ARM 配置adc_clk 時鐘端口,adc_rst 和復位端完成采集的時序及復位控制。

圖2 AD7606 控制器設端口連接圖Fig.2 AD7606 controller set port connection diagram

2.3 采集系統通信

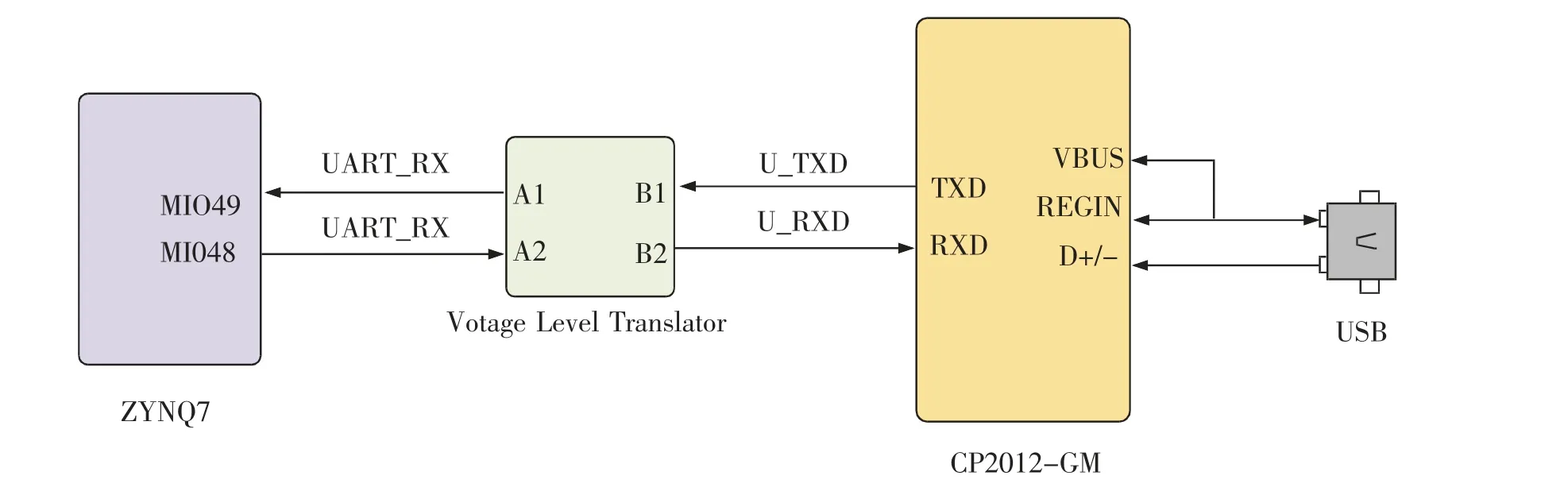

系統分為內部通信和外部通信。 內部通過AX4 總線進行通信,包含5 個獨立的傳輸通道讀地址、讀數據、寫地址、寫數據、寫回復,這些通道都支持單向傳輸,包括AXI4、AXI-Stream、AXI-lite 3 種接口,系統數據從AD 到ZYNQ 單向傳輸;因此只開啟了寫通道。 DMA 采用的AXI-Stream 接口,主從設備間能夠直接進行數據的讀取,數據傳輸不需要地址,提高了系統的實時性。 AXI 協議中主設備和從設備通過握手信號建立連接。 如圖3 所示, 使用UART 接口與外部通信系統采用Silicon Labs CP20102GM 芯片實現USB 接口轉UART 接口的功能, 并采用micro USB 線與終端進行串行通信。 UART 接口的TX/RX 信號與ZYNQ PS 的BANK501 信號相連,BANK501 的VCCMIO 電平為1.8 V,而CP2102GM 的數據電平為3.3 V,系統中間接入TXSOQ02DCUR 電平轉換芯片實現電平匹配。

圖3 串口通信連接圖Fig 3 Serial communication connection diagram

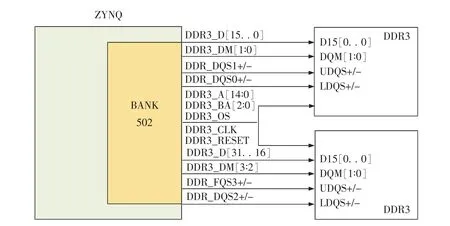

2.4 DDR 高速存儲

圖4 為DDR3 DRAM 硬件連接示意圖,DDR 是雙倍速率同步動態隨機存儲器,數據在工作時鐘的上升沿和下降沿都會進行采樣, 有效提升了存儲速率。 系統配有兩顆4 Gbit 的DDR3 芯片, 型號為H5TQ4G63ARFR-PBC。 DDR 總線位寬為32 bit, 最高運行速度可以達到533 MHz。 DDR3 存儲器直接與ZYNQ 處理器的BANK502 存儲接口相連。ZYNQ-Processing System 核配置存儲器時,必須確保DDR 接口型號一致或者兼容。

圖4 DDR3 DRAM 硬件連接圖Fig.4 DDR3 DRAM hardware connection diagram

3 數據采集系統的軟件設計

Xilinx IDE 套件中,在vivado 完成硬件工程設計的基礎上,SDK 會自動配置一些重要的參數,分為3 個模塊:硬件定義(hardware definition)包含定義的寄存器類型、地址映射以及當前設計包含的IP塊信心;板級支持包(board support package)包含支持IP 塊的驅動程序和變量參數頭文件; 應用程序(application)用于測試不同的功能。 據此完成系統軟件部分設計。

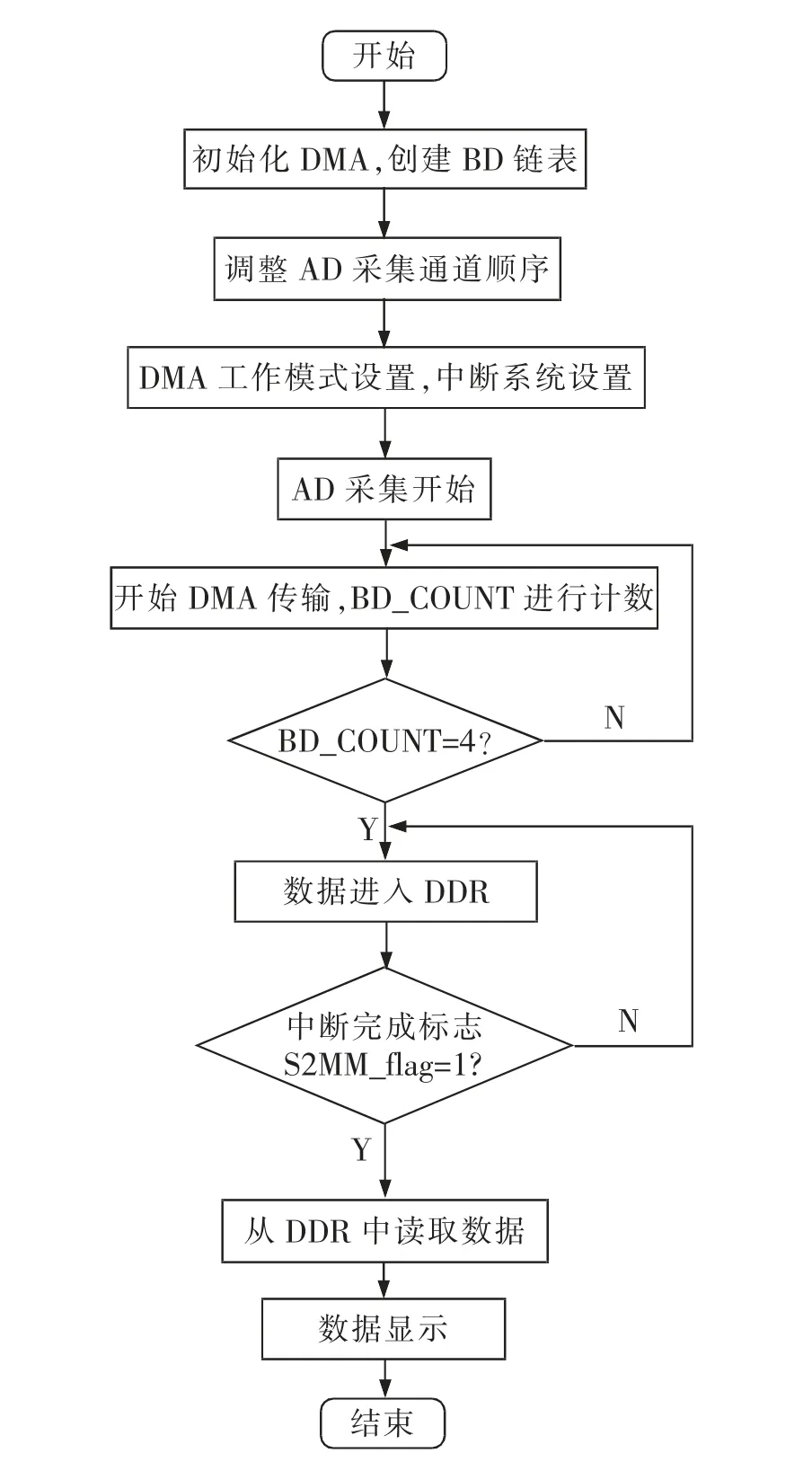

3.1 ADC-DMA 控制

ADC-DMA 控制是系統軟件核心模塊,程序運行前對ADC 和DMA 相關參數進行初始化設置,如ADC 的括基地址、偏移地址、采集長度、系數、字節數、位數和通道數。DMA 最大傳輸字節數、設備ID、中斷ID 和中斷觸發源。 ADC 數據寫入FIFO 中是按照1 至8 通道順序存儲, 程序定義了二維數組,將每個通道的數據獨立出來, 并調整了通道順序。為了在屏幕上顯示所有通道數據,系統將每個通道的系數進行了微調,使各通道波形形成錯位。 DMA的中斷觸發類型為完成觸發,此中斷屬于ZYNQ 的共享中斷, 觸發機制為當任務執行完成后觸發,硬件設計中DMA 只開起了寫通道接口, 中斷函數只打開Streams 到Memery Map 中斷。 SDK Terminal的接口、波特率和數據位配置后,應用printf 函數驅動串口通信完成終端數據顯示。 同時可以通過HDMI 接口與顯示器相連, 實現波形的實時顯示。ADC 控制流程圖如圖5。

圖5 ADC 控制器設計流程圖Fig.5 ADC controller design flow chart

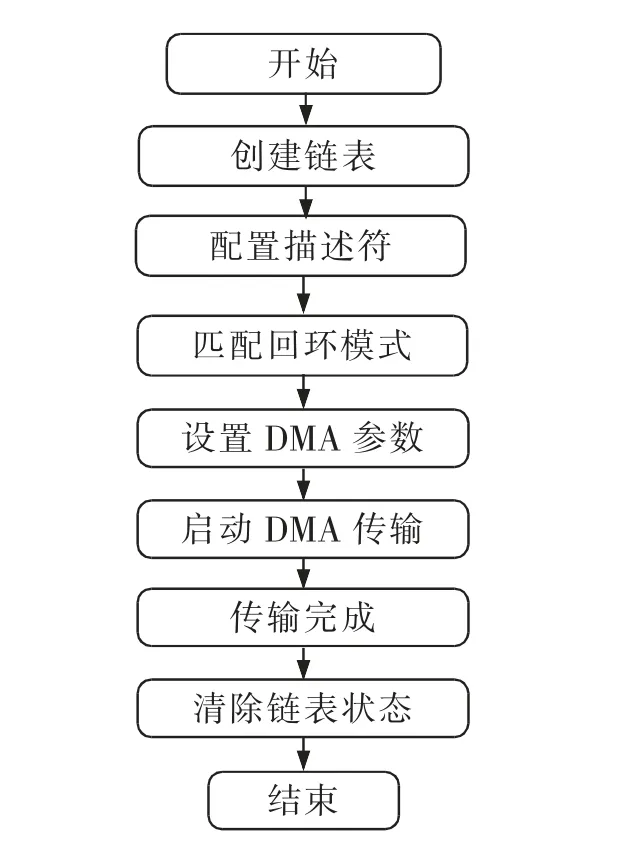

3.2 DMA-SG 模式應用設計

DMA-SG 模式相對簡單模式有著更高效的數據傳輸特性,允許一次單一DMA 傳輸訪問多個內存空間,所有任務結束后才觸發中斷。硬件工程開啟SG 模式后引出M_AXI_SG 接口,用于讀寫鏈表。鏈表以13 個寄存器組成的描述符為基本單元。 描述符中包含下一個描述符指針地址、數據緩存地址、控制存儲信息等。 寫通道SG 模式驅動設計流程如圖6 所示,需要在內存中開辟緩存空間和鏈表制作。將第一個描述符寫入當前地址寄存器。啟動DMA 并建立中斷系統,傳輸結束后會觸發中斷。將最后一個描述符寫入結尾結存器,觸發DMA 通過總線抓取鏈表描述符,BD 包傳輸完成后讀取下一個描述符。 將最后一個描述符指針只指向第一個描述符的地址,匹配回環模式。 數據處理完成后,清除鏈表狀態。

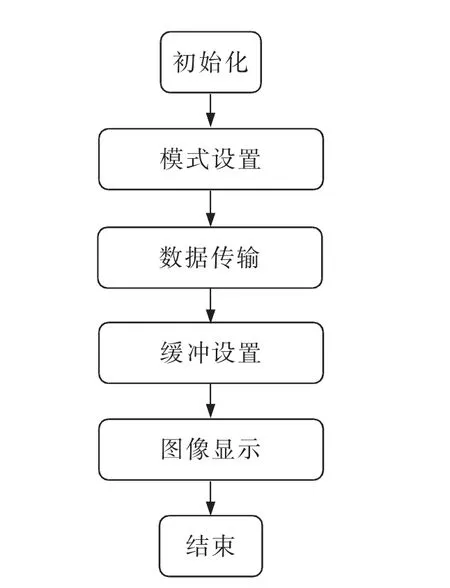

3.3 顯示控制模塊

該模塊提供了易于使用的API,控制顯示器通過VGA 或HDMI 連接到系統開發板上。根據顯示器分辨率大小設置畫布大小、背景和顏色。在畫布中取長方形區間作顯示波形的幅值和傳播時間。區間內設計32×32 像素點的小方格作為量化單位,水平和垂直方向每隔4 像素點顯示一次,網格顯示為灰色,背景顯示為黑色。 設計網格疊加函數和波形疊加函數對畫布緩存區的數據進行實時讀取, 實現波形的不間斷顯示。Catch 中讀取的數據在圖像上顯示為離散點,將數據與前一個數據進行比較,得出差值并在同一列描點,使波形顯示更為平滑。 可以通過修改波形起始位置參數改變波形區域的大小,但列起始位置加上波形高度必須小于顯示器分辨率,否則無法正常顯示。 系統屏幕以彩條作為顯示背景,設計了無縫幀緩沖器區,可實現無痕動畫。

圖像驅動流程如圖7 所示。首先要創建一個顯示對象,并對其初始化設置。調用DisplaySetMode 函數設置傳輸模式。 調用DisplayStart 函數將數據傳輸到顯示器上。 要實現無縫動畫,需要先將一張圖像繪制到當前未顯示的幀緩存區,后調用DisplayChangFrame 函數顯示此幀,重復操作顯示圖像。 若更改分辨,需調用顯示模式函數設置模式,然后,從新開始傳輸數據。

圖6 SG 模式驅動流程圖Fig.6 SG mode driving flow chart

圖7 圖像顯示流程圖Fig.7 Image display flow chart

4 實驗結果分析

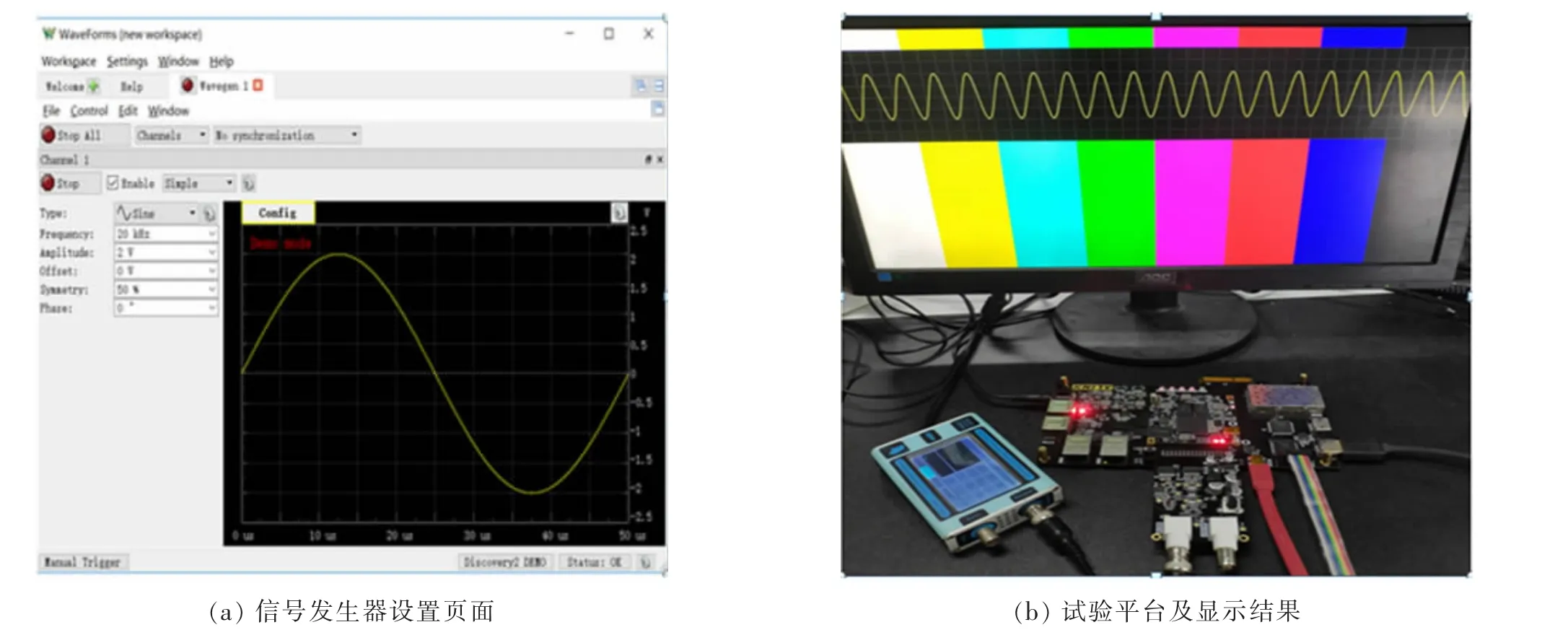

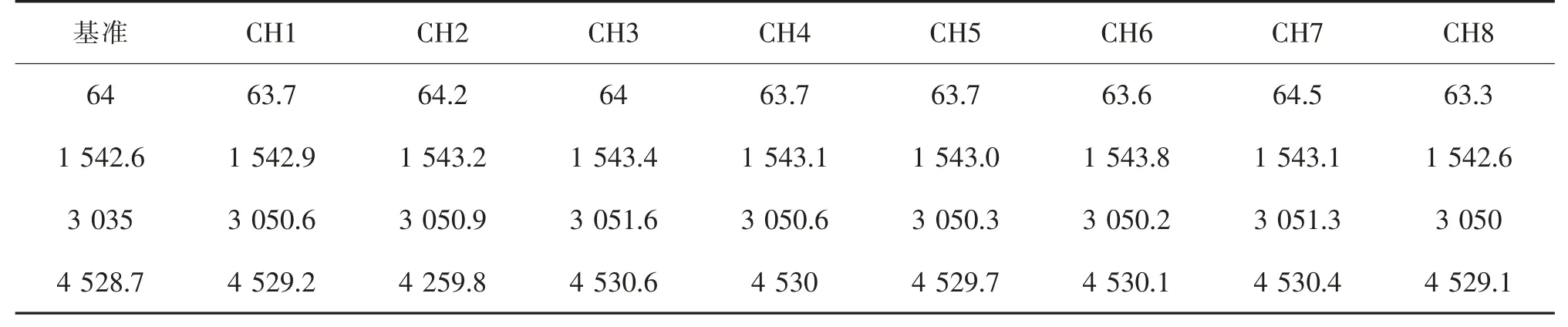

采用digilent 的Analog Discovery 2 任意函數發生器提供所需的信號進行實驗。 圖8(a)為信號發生器設置頁面,實驗對正弦信號、20 kHz、2 V 信號進行采集顯示,AD 采樣頻率為200 kHz,8 個采集通道全部開啟,由于硬件條件限制,只進行了單通道實驗。HDMI 顯示結果以及試驗平臺如圖8(b)所示,圖形界面顯示的正弦波即為系統采集信號,縱向分析,相鄰虛線間距表示一個度量單位,波峰到波谷共經過4 個單位表示從+2 V 到-2 V 信號,分析得出實驗結果和原始信號波形相同。 為了進一步驗證采集精度,實驗進行了8 通道4 個模擬電壓值的測試,測試結果通過串口打印出來,如表1 所示,第一列基準電壓為信號發生器發出值,后面8 列為系統測量結果。 根據式(1),計算出采集誤差為0.02%。

圖8 實驗結果圖Fig.8 Experimental results

表1 數據采集結果Tab.1 Data collection results mV

5 結論

針對電能質量檢測領域的高速數據采集要求,利用Xilinx 提供的Vivado 開發套件在ZYNQ SoC 上完成高速數據采集系統的設計。 該設計在硬件方面,借助ZYNQ 的FPGA 部分實現系統的采集控制,ARM 部分完成數據傳輸、存儲和結果顯示,其中基于自定義ad7606_sample IP 實現了AD7606 的采集控制,利用AXIHP 高速接口、AXI-DMA 硬核IP、DMA-SG 模式加快了系統的數據傳輸和處理速度。在軟件方面,完成了SG模式下的BD 包建立、波形顯示設計及DMA 數據傳輸控制。 通過測試的實驗結果表明,ARM 端驅動HDMI接口實現了采集信號的實時在線顯示。 通過對串口終端打印出來的數據進行分析,確定系統的采集誤差可達到0.02%。 系統具備體積小、功耗低、精度高、實時性強、穩定性強等特點。