基于ZYNQ+AT86RF215的電力高速載波雙模通信系統無線技術規范(HRF)技術驗證平臺

錢海鋒 張宏亮 王蓉

摘要:提出了一種基于ZYNQ+AT86RF215的電力高速載波雙模通信系統無線技術規范(HRF)技術驗證平臺,此平臺采用Xilinx ZYNQ SOC平臺和Atmel AT86RF215射頻收發芯片搭建,能低成本、快速實現原型芯片的驗證以及芯片模組在研產銷過程中的測量、分析、自動化故障排除。首先介紹ZYNQ+ AT86RF215的驗證平臺的硬件設計,其次對國網電力線高速載波雙模技術規范無線部分(HRF)規范進行計算機仿真并在平臺上實現,最后討論平臺在原型驗證、測量分析、故障排除等方面的實現方法。

關鍵詞:高速載波雙模技術規范;HPLC;HRF

0引言

電力行業提出2025年電力率先實現碳達峰,并正通過泛在電力物聯網、工業云網、智慧能源等舉措,加速推動碳達峰目標的實現。基于電力線通道的高速載波通信(HPLC)技術和基于無線通道的高速無線通信(HRF)技術,是實現輸電、配電、用電信息化和智能化的基礎設施,具有重要的作用。全流程的系統開發和應用,涉及到協議、芯片、模組、網絡等各環節,每個環節又涉及概念驗證、原型開發、小批量試制、實驗局驗證等步驟。該流程的周期長,通常有2到3年的時間,專用通信芯片研發成本高,并且開發過程存在極高的失敗風險。在這個背景下,需要一種低成本的快速芯片原型驗證平臺,需要能完成協議開發的合理性驗證,需要能完成通信芯片流片前的功能性能驗證,需要能完成模組開發過程中的功能性能驗證,也需要能實現實際網絡中的故障排除等工作。

本文提出了在ZYNQ+ AT86RF215的架構下,實現電力高速載波雙模通信系統無線技術規范部分原型系統的設計。本方案電路具備結構靈活的特點,接收和發射頻點靈活可調,適應各種頻率部署要求,ARM+FPGA的結構,快速實現協議開發,同時具備高動態范圍等優點。

1硬件架構

基于ZYNQ+AT86RF215的電力高速載波雙模通信系統無線技術規范部分原型系統技術驗證平臺的硬件架構框圖如圖1-0所示。

芯片驗證平臺的硬件架構實現分為核心處理板和射頻前端板兩個部分,兩部分之間用并線總線連接,完成供電、時鐘、控制、基帶數據等信號在兩個板子之間傳輸,實物如圖1-1。具體處理流程如下:

射頻前端板包括功率放大器(PA)、低噪聲接收器(LNA)和射頻收發器(Transceiver),其中PA實現發射信號的放大, LNA實現信號的低噪聲系數接收,PA和LNA的配合使用,實現了遠距離傳輸的要求,Transceiver采用的是Atmel公司的AT86RF215,是一種雙通道零中頻的軟件無線電解決方案,實現數模轉換DAC、模數轉換ADC、數字濾波Filter、上變頻DUC、下變頻DDC、自動增益控制AGC等功能。

核心處理板的主芯片為Xilinx Zynq UltraScale+ MPSoCs(ZU3),處理器內置四核ARM Cortex-A53和核心FPGA可編程邏輯模塊,實測算力可達1.2TOPS,平均功耗低至5-10W。針對泛在電力物聯網中通信協議,ARM采用C語言開發,實現層2、層3的功能,FPGA采用Verilong語言開發,實現層1的功能。

兩個處理板的主要規格參數如下:

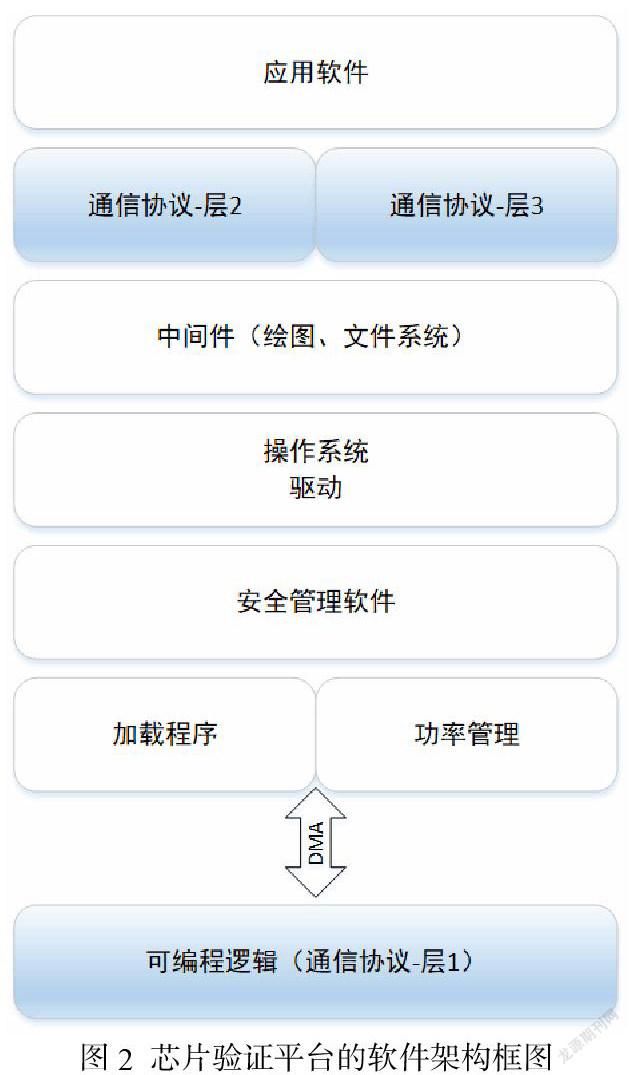

2軟件架構

基于ZYNQ+AT86RF215的電力高速載波雙模通信系統無線技術規范(HRF)快速驗證平臺的軟件架構框圖如圖2所示。

芯片驗證平臺的軟件架構實現分為ARM層軟件和FPGA層兩個部分,兩部分之間用DMA完成數據的交互。ARM為4個Cortex-A53核和2個RealTime核,實現通信協議的層2和層3的功能。FPGA為可編程邏輯,實現通信協議的層1的功能。

3 HRF協議原型實現

HPLC是高速電力線載波,是在低壓電力線上進行數據傳輸的寬帶電力線載波技術。寬帶電力線載波通信網絡則是以電力線作為通信媒介,實現低壓電力用戶用電信息匯聚、傳輸、交互的通信網絡。進一步,為了更好的實現這一目標,在HPLC的基礎上增加基于無線通信信道的通信制式HRF,該協議是本文要進行芯片原型驗證的目標。

在基于ZYNQ+ AT86RF215的驗證平臺上,快速的、低成本的實現HRF通信協議,以達到芯片原型驗證的目的,其中使用C軟件在4個ARM核實現層2、層3的功能。本文重點論述在FPGA的可編程邏輯上實現的物理層協議,該部分是芯片驗證的重要部分,分為仿真建模和可編程定點實現兩個過程。

3.1仿真建模

仿真建模采用Matlab軟件,版本號為R2020A,數據為雙精度浮點數,分別實現發射機和接收機的功能以及性能的仿真驗證。物理層發射鏈路的仿真實現流程圖3所示。物理層接收鏈路的仿真實現流程圖4所示。

3.2程序實現

邏輯實現采用Xilinx Vivado軟件開發,版本號為R2019.1,數據為定點數,分別實現物理層發射鏈路和接收鏈路的功能。

系統主時鐘為50MHz,在速度和功耗之間做了折衷。基帶數據速率為3.125M,數模轉換DAC和模數轉化ADC的接口速率為4M,因此發射鏈路要做32倍內插,25倍的抽取,接收鏈路要做25倍的內插,32倍抽取。為了獲得較好的帶外抑制指標,需要在DA和AD處添加信道濾波器,帶外抑制不低于45dBc,帶內平坦度不大于0.1dB。

PL和PS之間的DMA搬移速度為25M,用于PS和PL之間的數據傳輸,實現層1和層2、層3之間的協議幀的交互。系統的數據位寬定位16bit,其中Turbo解碼和信道估計的主路徑數據定位32位。

完整的發射鏈路和接收鏈路的實現所需要的資源如下表所示:

3.3測試分析

3.3.1發射信號頻譜分析:在頻譜儀上,實時顯示RF信號的頻域信號,可以初步查看信號的質量,如圖5。

3.3.2 接收數據星座圖分析:在信噪比比較理想情況下,抓取QPSK調制的數據進行分析,在分析過程中畫出的星座圖,如下圖6-0 。在信噪比存在惡化情況下,抓取QPSK調制的數據進行分析,在分析過程中畫出的星座圖。如圖6-1。

3.3.3 接收數據誤碼率分析:HRF 信號,采用turbo編碼,交織,QPSK星座圖映射,OFDM調制等操作。接收數據經過OFDM解調,信道均衡,星座圖軟判決,解交織,turbo碼的MAX-LOG-MAP解碼算法等。在接收端在線計算信噪比,統計解碼后的誤碼率,然后把統計結果通過網口送個電腦。通過改變無線信道的信噪比。繪制成曲線,圖7。

3.3.4其他在線測量參數如下表所示:

3.3.5報文分析:與在線數據質量分析著重在信號質量的分析不同,在線協議分析著重在層2、層3的協議報文的實時分析。

實現方式是按照協議要求,發送特定報文給其他網元,并獲得該網元的反饋協議報文。根據這些報文情況,對網絡拓撲等信息進行具體分析,獲得網絡故障信息甚至實現自動化運維。

4結語

本文提出了一種基于ZYNQ+ AT86RF215的驗證平臺,該平臺具備架構靈活、性能優越且成本低廉的特點,同時,把泛在電力物聯網的HRF協議在該平臺上實現,驗證了平臺的能力,最后,在該平臺上開發了一些列功能,可以實現數據抓取、在線數據質量分析、在線協議分析等需求,可以協助完成驗證、故障排查和自動化運維的工作。平臺驗證的結果可以直接運用于流片,使得HRF等芯片開發周期大大縮短。

參考文獻

[1]楊小牛.從軟件無線電到認知無線電,走向終極無線電-無線通信發展展望[J].中國電子科學研究院學報,2008(1):1-7.

[2]鄭君里《信號與系統》

[3]李昱燃,楊軍,任志國.FPGA 內嵌ARM 的高速數據采集系統設計[J].新器件新技術,2019(6):54-59.

[4]詹書榮,黃春暉.Turbo譯碼器滑動窗的改進及其FPGA設計.電力學報.