一種X波段鎖相環頻率合成器的設計與實現

郝延剛,祁 全,吳 梅

(1. 海軍裝備部駐南京地區第二軍事代表室,南京 211153;2.中國船舶集團有限公司第八研究院,南京 211153)

0 引 言

作為雷達和通信系統的重要組成部分,頻率合成器在工作時產生高準確度和穩定度的本振基準信號,供雷達及通信收發模塊對載波信號進行調制解調及相參處理。[1-3]本振信號頻譜質量的優劣直接關系到雷達及通信收發系統的信號處理能力。高質量的頻率合成器可有效提高雷達接收機的靈敏度及目標檢測能力,降低通信系統解調信號的誤碼率,實現更加安全準確的無線通信。

頻率合成器的主要技術指標有相噪、雜散、跳頻時間等,其中相噪是衡量頻率合成器輸出信號質量最關鍵的技術指標。在雷達系統中,本振信號的邊帶相噪直接決定接收機的靈敏度和選擇性,影響雷達檢測目標的能力。雜散是偏離載波離散頻率上的干擾信號。它會與其他信號混頻產生不期望的噪聲產物,惡化接收機系統的噪聲系數和動態范圍。跳頻時間影響雷達系統處理數據的速度,足夠迅速的跳頻能保證雷達系統單位時間內實現頻率快速捷變,提高雷達對抗能力。

基于鎖相環(PLL)技術的頻率合成器具有較寬的頻率輸出范圍、高雜散抑制和較好的相噪性能,成為現代電子信息系統中應用最廣泛的頻率合成器件。本文以PLL頻率合成方法進行頻率合成仿真與電路設計,并對其輸出的點頻信號展開研究。

1 結構與理論分析

1.1 PLL結構

PLL是一個閉環相位負反饋系統,其基本結構包括鑒相器(PD)、環路濾波器(LP)、壓控振蕩器(VCO)。[2]歷經數十年成熟的理論研究和實踐應用,以及數字技術的進步,現今基于PLL的頻率合成技術還增加了參考分頻器(R)、環路分頻器(N)、電荷泵(CP),稱為數字鎖相環技術。

本文基于數字鎖相環技術的PLL頻率合成器結構如圖1所示。

圖1中,鎖相環路中所用的PLL芯片和VCO芯片采用美國HITTITE公司的HMC704和HMC509,其主要技術參數如下:

PLL芯片HMC704:

? 頻率范圍:DC~8 GHz,fPFD:115 MHz;

? 基底相噪:-233 dBc/Hz。

VCO芯片HMC509:

? 輸出頻率:7.8~8.8 GHz,內置二分頻;

? 開環相噪:-115 dBc/Hz@100 kHz;

? 輸出功率:10~15 dBm。

1.2 相噪理論分析

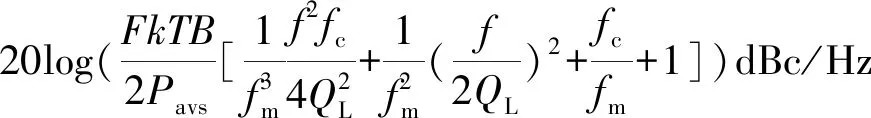

相噪是衡量PLL性能最重要的指標。通過理論分析,對相噪性能進行合理評估,可為實際設計和測試提供理論參考。振蕩器的相噪模型依據leeson相噪方程[4],如式(1)所示。

(1)

由式(1)可知,相噪的組成成分包含1/fn(n=0~3),近端相噪主要受閃爍噪聲(又稱1/f噪聲)主導。考慮到leeson相噪方程結構復雜,工程應用中難以做到準確分析。

出于簡化理論分析需要,工程師在實際應用中更多采用式(2)[4-5]對PLL的帶內相噪性能進行粗略評估。

PN=PN1Hz+10logfPFD+20logN

(2)

式中,PN1Hz是PLL芯片的基底相噪。根據式(2),帶內相噪主要依賴于環路分頻系數N,其數值將以20logN惡化。分頻系數越大,相噪性能越差,因此通過降低分頻系數可有效改善帶內相噪性能。由于本文所設計的PLL頻率合成器產生點頻信號,無需考慮頻率步進,在保證環路工作穩定的前提下應盡可能設置大的鑒頻鑒相頻率fPFD,從而降低分頻系數,改善帶內相噪性能。

2 設計與實現

根據要求,所設計的PLL頻率合成器產生8.4 GHz的點頻信號。PLL芯片HMC704整數模式下fPFD高達115 MHz,此處設置fPFD=100 MHz,以獲得較好的相噪指標。首先對PLL的相噪性能進行必要的仿真分析,初步評估系統性能,進而優化相關設計。

2.1 環路濾波器設計與相噪仿真

環路帶寬的設置是PLL頻率合成器調試最重要的工作之一。若設置的環路帶寬較寬,則鎖定時間變短,但因濾波不充分將產生較大雜散信號,反之鎖定時間變長。若無特別要求,出于折中考慮,通常設置環路帶寬值為PLL芯片和VCO芯片相噪值相等處的頻率,這樣可最大限度地兼顧鎖定時間和雜散指標。

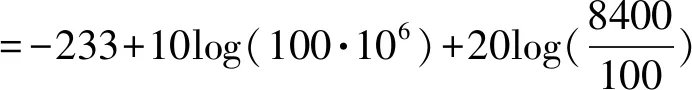

根據式(2)可得,PLL帶內相噪理論值為

=-114.5 dBc/Hz

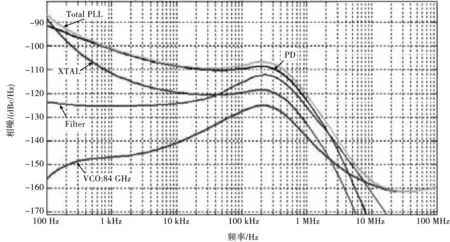

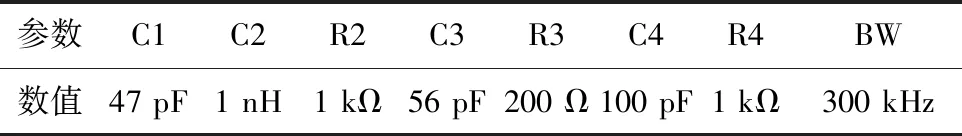

參考VCO芯片的相噪測試圖[5],兩者在頻偏100 kHz處相近,因此在仿真初期可設置環路帶寬值為100 kHz左右。仿真過程中,當設置環路帶寬100 kHz時,在環路的“肩膀”處出現了較大的過沖現象。此處的相噪甚至高達-90 dBc/Hz,而且整體近端相噪也有所抬升,無法滿足實際應用。因此,需要適當增大環路帶寬。經過反復仿真,最終設置帶寬300 kHz。圖2是設置帶寬300 kHz的相噪仿真曲線。從圖中可以看出,從1~100 kHz的近端相噪均優于-100 dBc/Hz。考慮到PLL的電荷泵電壓無法滿足VCO的高調諧電壓,環路濾波器采用有源四階結構[6],如圖3所示。表1給出環路濾波器的元件參數。

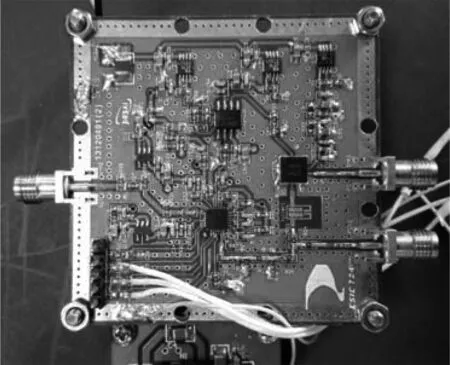

2.2 版圖實現與測試

PCB測試版圖如圖4所示。采用外部連接100 MHz恒溫晶振OCXO和89C2051單片機控制,版面尺寸60 mm·60 mm。若合理布局,并采用更小封裝的基礎元器件,可進一步縮小尺寸。為了獲得較純凈的反饋信號頻譜,抑制諧波分量或雜散信號對PLL的調制,在VCO輸出反饋端設計了一個低通濾波器。

圖2 相噪仿真曲線

表1 環路濾波器參數

圖4 測試版圖示意

圖5是Span分別設置為1 GHz和10 MHz時的輸出頻譜圖。從圖中可以看出,寬掃頻和窄掃頻下的頻譜均非常純凈,頻率準確鎖定在8.4 GHz處。

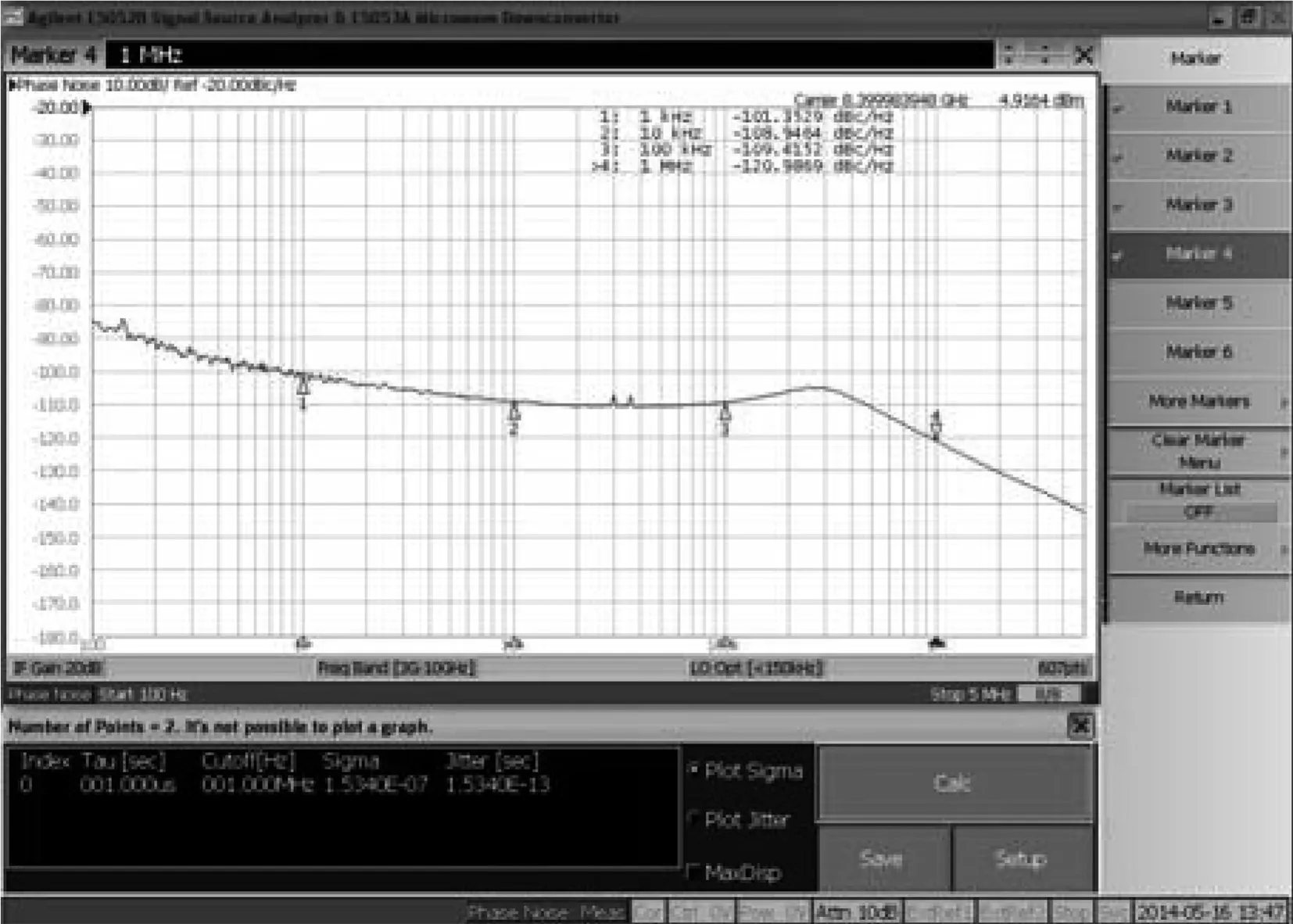

利用信號源分析儀E5052B測試得到的相噪曲線和頻率穩定度如圖6所示。圖2與之比較可發現,兩者相噪曲線吻合較好,驗證了仿真結果的可靠性。從圖6得到,相噪曲線上無明顯參考雜散干擾和工頻諧波信號,1 kHz頻偏處的相噪優于-100 dBc/Hz,10和100 kHz頻偏處的相噪接近-110 dBc/Hz,1 MHz頻偏處的相噪優于-120 dBc/Hz。頻率抖動達到亞皮秒級,在100 Hz~100 kHz帶寬內,抖動低于160 fs。輸出功率約4.9 dBm,注意到測試所用線纜在8.4 GHz處的損耗約5 dB,SMA轉接頭和走線損耗約2 dB,故實際輸出功率可達12 dBm,與VCO芯片所給指標是一致的,能夠滿足一般收發系統對功率的指標要求。

圖6 相噪和頻率穩定度測試結果

3 測試數據分析

理論研究表明,PLL的近端相噪主要由參考源和PLL的相噪特性決定,而遠端相噪由VCO的相噪特性決定。從仿真曲線可以看出,OCXO只在非常靠近輸出頻率(頻偏100 Hz以內)時才對相噪起決定作用,而環路濾波器截止頻率附近的相噪性能又同時受到多個器件影響,無法準確分析各器件對相噪的貢獻。考慮到雷達系統對載波信號的近端相噪有較高要求,因此主要分析頻偏1 ~100 kHz范圍內的相噪性能。

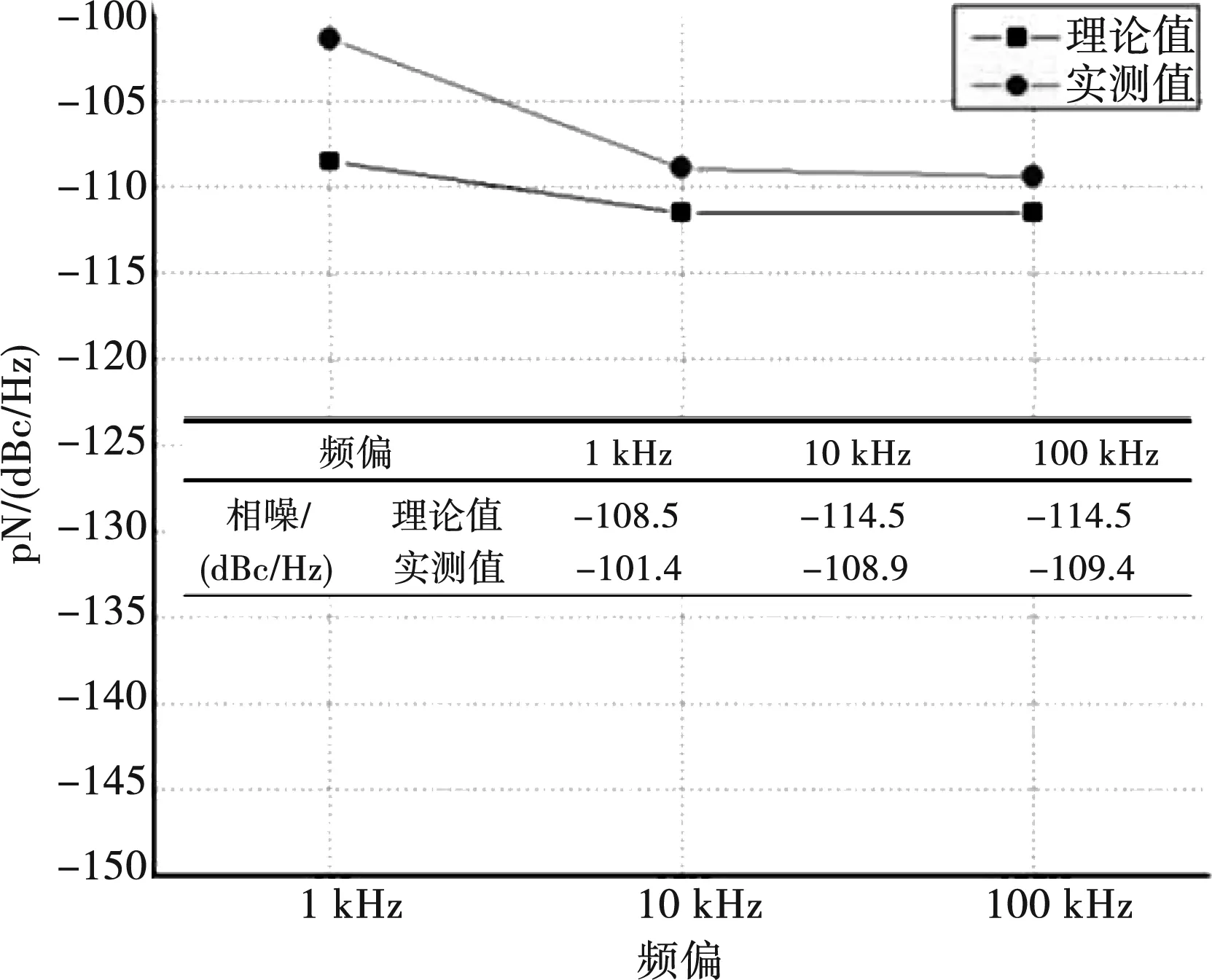

根據1.2節的分析,評估PLL帶內相噪性能時忽略了閃爍噪聲對近端相噪(頻偏100 Hz~1 kHz以內)的影響。假設閃爍噪聲與基底噪聲對PLL近端相噪的貢獻是相同的,則相較僅受基底噪聲的貢獻,理論相噪在此頻率范圍內將會惡化3 dB。參考芯片數據手冊、理論分析和實測數據,匯總得到圖7。

根據圖7所示,實測曲線與理論曲線具有一致的變化趨勢。實測值與理論值最大相差7.1 dB@1 kHz,最小相差5.1 dB@100 kHz。一方面,簡化理論分析后削弱了閃爍噪聲對近端相噪的決定影響,從而導致1 kHz處的差值最大;另一方面,PLL受到電源紋波和工頻等干擾對帶內相噪的調制,且未采取有效的電磁屏蔽措施,惡化了EMC特性。

圖7 近端相噪理論值與實測值比較圖

綜上所述,所實現的PLL頻率合成器采用大鑒頻鑒相頻率,輸出點頻信號具有優異的相噪和雜散特性,達到了設計要求。通過充分的電源去耦和電磁屏蔽,近端相噪性能仍有提升的空間。通過進一步合理設置環路濾波器帶寬和相位裕度,有望改善過沖效應和遠端相噪性能。

4 結束語

本文設計了一個X波段的PLL頻率合成器。測試結果顯示,輸出信號頻率為8.4 GHz,頻譜質量純凈,無明顯雜散干擾,1 kHz頻偏處的相噪優于-100 dBc/Hz,可為雷達收發系統提供優質的本振信號。