Zynq SOC嵌入式圖像邊緣檢測系統設計

聶陽 王博文 王宇鵬 梁蔭恩 唐偉健 趙國宏 徐碩

摘? 要:針對目前市場上嵌入式圖像處理平臺可擴展性差的缺點,利用Zynq SOC嵌入式處理器ARM和FPGA結合的優勢,文章提出基于Zynq SOC的嵌入式圖像處理系統設計方案。實驗結果表明,該方法不僅提高了圖像邊緣檢測質量,而且具有實時性和可擴展性好的優勢。

關鍵詞:嵌入式系統;Zynq;圖像處理;邊緣檢測

中圖分類號:TP391? ? ? ? 文獻標志碼:A? ? ? ? ?文章編號:2095-2945(2020)23-0054-03

Abstract: Aiming at the disadvantage of poor scalability of embedded image processing platform on the market, we propose an embedded image processing system design scheme based on Zynq SOC with the advantages of Zynq SOC embedded processors ARM and FPGA. The experiment results show that the proposed method not only improves the quality of image edge detection, but also has the characteristics of real-time and scalability.

Keywords: embedded system; Zynq; image processing; edge detection

1 概述

圖像是人類獲取和交換信息的主要來源之一。因此,圖像處理的應用已經涉及人類生活的各個方面。目前,圖像處理在物聯網、機器識別和多媒體信息交換等領域得到了廣泛的應用。但是,隨著圖像處理系統規模和復雜性的不斷增加,其硬件系統實現越來越復雜。為了滿足圖像處理算法的正確性和實時性,現場可編程門陣列(Field Programmable Gate Array,FPGA)已經成為了實時圖像處理硬件平臺的理想選擇[1-2]。

近年來,隨著嵌入式處理器性能的不斷提高,嵌入式操作系統的不斷完善,以及網絡、通信多媒體、圖像處理技術的快速發展,基于嵌入式技術的圖像處理系統以其低廉的價格和便攜性成為圖像處理的一個發展方向。目前,市場上主流的嵌入式圖像處理系統大多采用ARM9、ARM11等系列微控制器。大部分的ARM微控制器硬件外設出廠時已經固定,不利于用戶進行硬件擴展和升級,而ARM和FPGA相結合的多芯片圖像處理解決方案又會導致系統成本太高,同時還會造成系統資源的浪費,整體系統功耗較大。為了滿足市場的需求,美國Xilinx公司開發了Zynq系列全面可編程芯片,該系列芯片采用高性能Cortex-A9雙核處理器和FPGA相結合[3-4]。

本文采用Xilinx全面可編程芯片Zynq作為開發平臺,ARM處理器完成系統運行和數據交換,FPGA部分實現硬件擴展和圖像處理算法。采用軟硬件協同設計的方法,完成嵌入式圖像處理系統的設計。相比于傳統的圖像邊緣檢測系統,基于Zynq SOC的嵌入式系統不僅提高了圖像的檢測質量,而且具有實時性和可擴展性好的優點。

2 系統整體設計結構

ZYNQ是賽靈思公司(Xilinx)推出的新一代全可編程片上系統(APSoC),它將處理器的軟件可編程性與 FPGA 的硬件可編程性進行完美整合,以提供無與倫比的系統性能、靈活性與可擴展性。與傳統SoC解決方案不同的是,高度靈活的可編程邏輯(FPGA)可以實現系統的優化和差異化,允許添加定制外設與加速器,從而適應各種廣泛的應用。Zynq-7000系列是Xilinx公司推出的全可編程片上系統,主要包含PS(Processing System)和PL(Programmable Logic)兩部分。PL采用28nm工藝;PS以2個Cortex A9的ARM核為核心,還包括片上存儲器、片外存儲器接口(DDR)和一系列的外設接口。Zynq-7000系列將ARM CPU 和外設集成在一個芯片內,使得 Zynq-7000系列皆具處理器和 FPGA 雙重特性,特別適用于軟硬件協同設計。

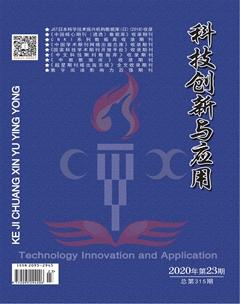

系統平臺由攝像頭、顯示器和Zynq SOC開發板三部分構成,結構如圖1所示。攝像頭選用MT9V034,顯示器為21英寸戴爾液晶顯示器。Zynq SOC開發板選用ZedBoard開發板,該開發板板載512M的DDR3內存。ZedBoard是Digilent公司開發的一款搭載Xilinx Zynq-7000全面可編程系統芯片的低成本開發板。該開發板可以基Linux,Android,Windows或基于其它操作系統進行設計。Zynq-7000器件配備雙核ARM Cortex-A9處理器,該處理器與基于28nm Artix-7FPGA集成,具有優異的性能功耗比和最大的設計靈活性,為嵌入式應用實現高度差異化設計提供保證。

整個圖像處理系統的實現由處理系統和可編程邏輯協同完成。PS部分的ARM處理器負責運行操作系統、調用資源實現與PL的數據交換,并且完成應用層QT程序的實現。PL部分主要實現攝像頭的圖像采集并通過VDMA到DDR3存儲器中保存數據,同時將采集到的圖像進行圖像處理,最后把處理好的圖像通過自定義設計的顯示模塊高清顯示。

3 圖像處理算法:邊緣檢測

所謂邊緣是指其周圍像素灰度急劇變化的那些象素的集合,它是圖像最基本的特征。邊緣存在于目標、背景和區域之間,所以,它是圖像分割所依賴的最重要的依據。由于邊緣是位置的標志,對灰度的變化不敏感,因此,邊緣也是圖像匹配的重要的特征。

邊緣檢測和區域劃分是圖像分割的兩種不同的方法,二者具有相互補充的特點。在邊緣檢測中,是提取圖像中不連續部分的特征,根據閉合的邊緣確定區域。而在區域劃分中,是把圖像分割成特征相同的區域,區域之間的邊界就是邊緣。由于邊緣檢測方法不需要將圖像逐個像素地分割,因此更適合大圖像的分割。邊緣大致可以分為兩種,一種是階躍狀邊緣,邊緣兩邊像素的灰度值明顯不同;另一種為屋頂狀邊緣,邊緣處于灰度值由小到大再到小的變化轉折點處。邊緣檢測的主要工具是邊緣檢測模板。

邊緣檢測的原理是檢測圖像特性發生變化的位置。不同的灰度圖像灰度不同,邊界處會有明顯的邊緣,利用該特征可以分割圖像。邊緣總是以強度突變的形式出現,這被定義為圖像局部特性不連續,如灰度的突變和紋理結構的突變。圖像的邊緣包含了物體形狀的重要信息,它不僅在分析圖像時大幅度地減少了要處理的信息量,而且還保護了目標的邊界結構。邊緣檢測是圖像分割的經典研究課題之一,直到現在仍然在不斷發展和改進,尤其是面向嵌入式系統的圖像檢測。Sobel算子對圖像進行了二維空間梯度測量[5]。通常,它用于在輸入圖像的每個點找到近似的絕對梯度幅度。

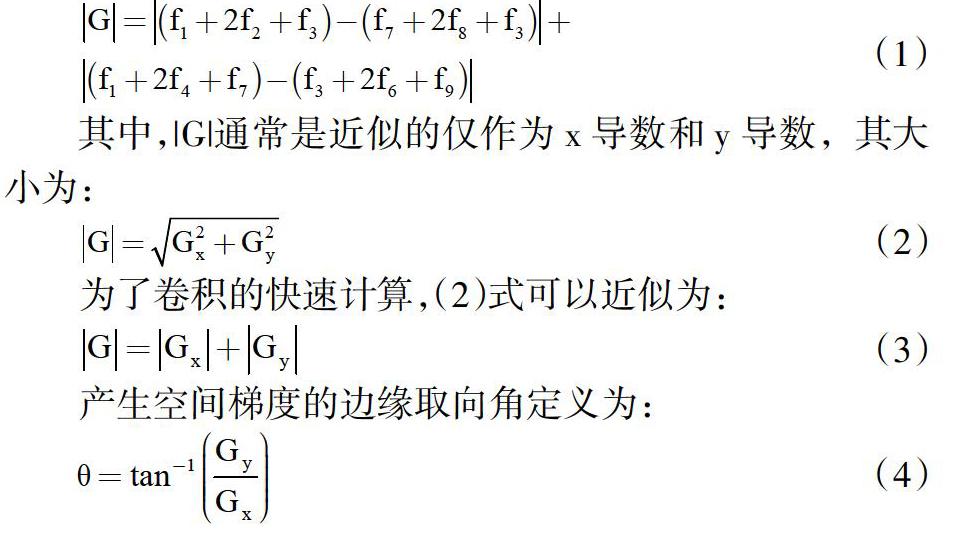

Sobel算子每個卷積因子是進行圖像的九十度旋轉。假設一個與Sobel算子維度相同的圖像片段,卷積的結果如下:

4 系統測試與驗證

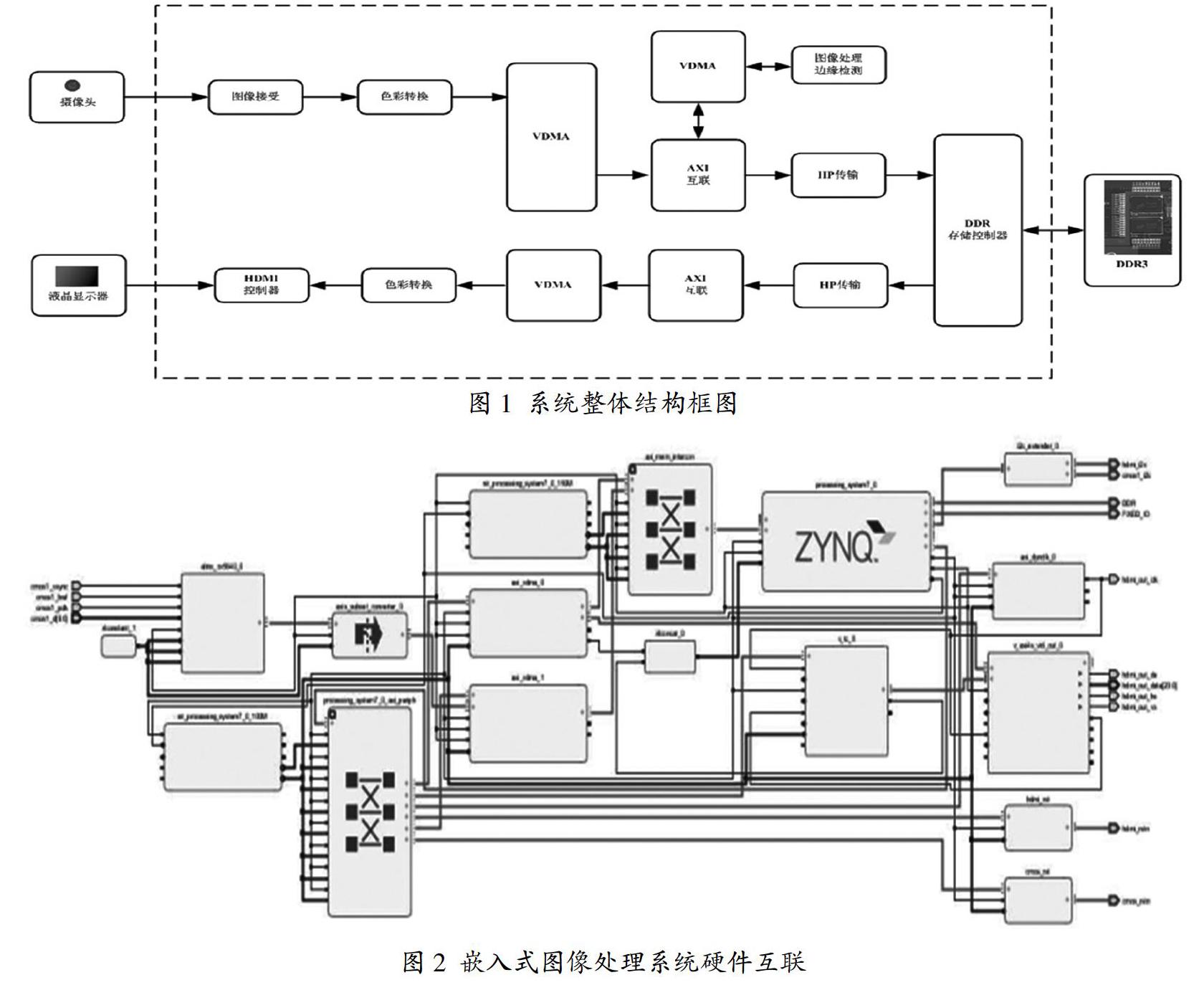

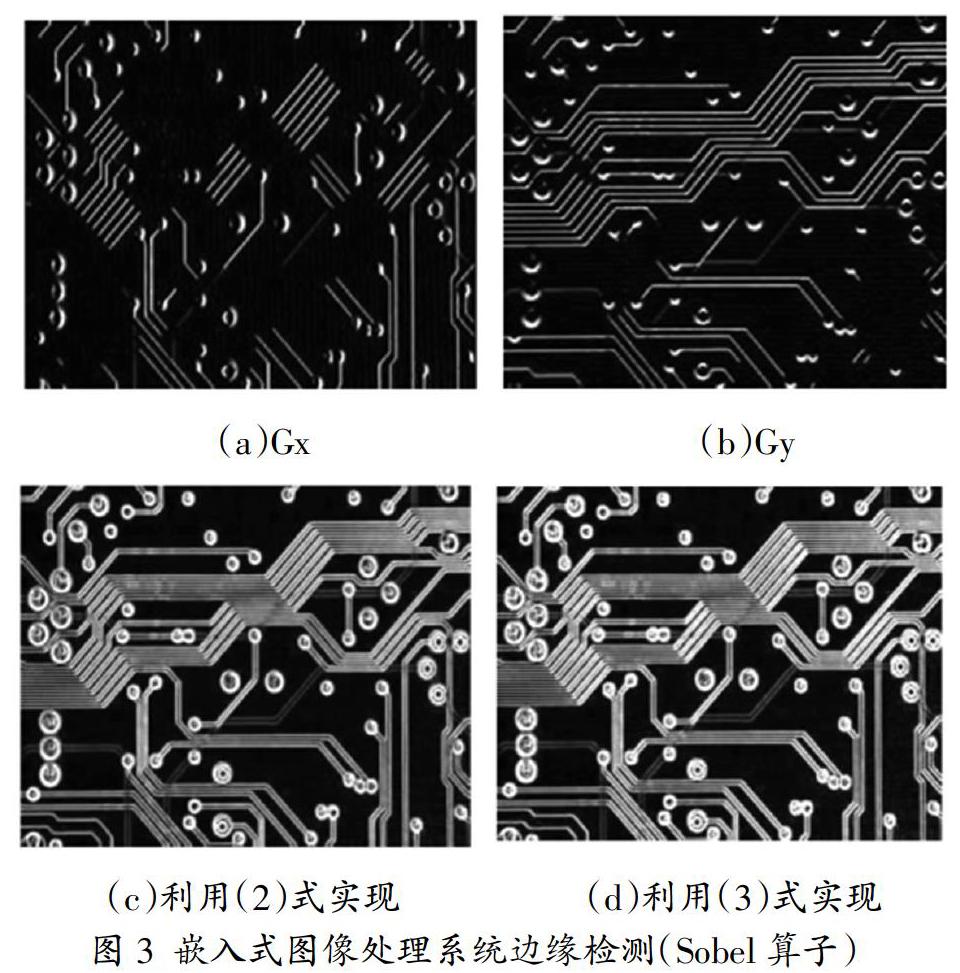

基于Zynq SOC的嵌入式圖像處理系統由攝像頭負責圖像采集,Zedborad開發板負責系統的運行和邊緣檢測算法,系統的硬件模塊連接如圖2所示。從圖中可以看出,Zynq SOC是整個系統的核心,基于定制的IP模塊VDMA完成圖像的幀的緩沖,通過AXI互聯與DDR進行數據的高速交互,最后利用HDMI接口輸出處理后的圖像,如圖3所示。

5 結束語

本文基于Zynq SOC全面可編程芯片完成了嵌入式圖像采集與處理系統,系統利用Sobel算子實現了圖像的邊緣檢測。該系統充分體現了Zynq SOC芯片ARM處理器與FPGA可編程邏輯的優勢。與傳統圖像處理硬件方案相比,基于Zynq SOC嵌入式圖像處理方法不僅提高了圖像處理的質量,而且具有實時性和可擴展性好的特點。

參考文獻:

[1]李朗,張索非,楊浩.基于Zynq-7000的視頻處理系統框架設計[J].計算機技術與發展,2017,27(05):192-195.

[2]孟繁星.基于ZYNQ-7000的視頻圖像處理系統設計[J].信息通信,2015(08):60-62.

[3]郭豐收.Xilinx FPGA/Zynq設計中使用HLS實現OpenCV的開發流程[J].電子產品世界,2014,21(Z1):50-52.

[4]聶陽.基于Zynq的嵌入式系統教學研究[J].電子測試,2016(Z1):92-93.

[5]Lee C C. Elimination of redundant operations for a fast Sobel operator[J]. IEEE Transactions on Systems Man & Cybernetics,1983,SMC-13(2):242-245.