一種亞閾值有源共源共柵補償運算放大器

張春茗 王夢海 嚴展科

摘? 要: 針對低壓低功耗高增益高帶寬應用背景的運算放大器,提出一種新型亞閾值有源共源共柵補償(SACC)運算放大器。通過使用亞閾值跨導提升輔助放大器,以非常低的功耗成本改善整體電路的帶寬,同時有效地減小補償電容的數值,且輸出級采用動態前饋結構,顯著提升電路擺率。當驅動10 pF容性負載時,放大器的補償電容僅需60 fF即可實現穩定,從而大大減小了放大器的版圖面積。提出的放大器在28 nm CMOS工藝下設計并驗證,并且當驅動10 pF的容性負載時,仿真結果表明,在0.9 V電源電壓下,可實現69.5 dB的直流增益和13.3 MHz的增益帶寬積,且功耗僅為4.5 μW。此外,提出的放大器與現有的方案相比較具有更好的品質因數(FOM)。

關鍵詞: 亞閾值共源共柵補償; 亞閾值區域; 運算放大器; 低壓低功耗; 穩定性分析; 仿真驗證

中圖分類號: TN722.7+7?34? ? ? ? ? ? ? ? ? ? ? ? 文獻標識碼: A? ? ? ? ? ? ? ? ? ? ? 文章編號: 1004?373X(2020)06?0013?05

A subthreshold active cascade compensation operational amplifier

ZHANG Chunming, WANG Menghai, YAN Zhanke

(College of Electronic Engineering, Xian University of Post and Telecommunications, Xian 710121, China)

Abstract: A novel subthreshold active cascade compensation (SACC) technique is proposed for the application background of low voltage, low power consumption, high gain and high bandwidth. The booster amplifier is promoted by means of the subthreshold transconductance to improve the bandwidth of the whole circuit at very low cost of power consumption, and effectively reduce the value of the compensation capacitor. The slew rate of the circuit is improved significantly with the dynamic feed?forward structure adopted in the output stage. The required compensation capacitance to stabilize the amplifier is only 60 fF when driving a 10 pF capacitive load, so that the layout area of the amplifier is greatly reduced. On the basis of the 28 nm CMOS process, the proposed amplifier is designed and verified. The simulation results show that, when driving the 10 pF capacitive loading at the supply voltage of 0.9 V, the proposed amplifier can achieve DC gain of 69.5 dB and gain?bandwidth product (GBW) of 13.3 MHz, and the power consumption is only 4.5 μW. Moreover, the proposed amplifier achieves a better quality factor (FOM) in comparison with the existing solutions.

Keywords: SACC; subthreshold region; operational amplifier; low voltage and low power consumption; stability analysis; simulation verification

0? 引? 言

隨著便攜可穿戴設備的普及,市場對低壓低功耗電池供電設備的需求不斷增長,因此要求模擬和混合模式信號處理電路具有更好的性能。運算放大器作為模擬集成電路的關鍵模塊,廣泛應用于低壓差穩壓器、開關電容電路、數據轉換器以及帶隙基準等電路系統中[1?2]。在低電壓低功耗設計中,運算放大器的頻率補償問題將面臨嚴峻的挑戰。兩級CMOS運算放大器普遍采用密勒補償技術,以在閉環條件下實現穩定。然而由于補償電容引入的前饋路徑使得電路存在一個右半平面零點,在相對較高的頻率產生負的相位貢獻,因此極大地降低了可實現的最大增益帶寬積。因此,在兩級運算放大器的設計中,右半平面零點補償必須考慮。針對運算放大器的穩定性問題,已經提出了各種補償技術[3?9]。

文獻[4]采用與補償電容串聯的調零電阻。文獻[6?7]分別在補償網絡串聯電流緩沖器和電壓緩沖器來破壞前饋路徑,消除密勒補償帶來的右邊平面零點。文獻[8]引入前饋網絡補償非主極點帶來的相位損失。文獻[9]引入阻尼因子控制(DFC)電路進行頻率補償。各種補償技術不同程度地改善了穩定性問題,但也會引入一些其他問題,例如:調零電阻使得版圖面積增大;電流緩沖器帶來額外的功耗;電壓緩沖器使得輸出擺幅受限等。且上述補償技術需要大的補償電容,其數值一般為負載電容的0.1~0.5。為了解決以上問題,本文提出一種亞閾值有源共源共柵補償運算放大器,在降低功耗的同時,顯著減小補償電容的數值,增大單位增益帶寬。

1? 共源共柵補償

圖1為典型的共源共柵補償跨導運算放大器,M2~M7和Mc組成折疊式共源共柵輸入級,M8和M9組成Class?A型輸出級,CC為補償電容。

該結構以電流緩沖補償技術為原型,補償電路和輸入級電路共用同一個晶體管Mc,在減小電路復雜度的同時節約了功耗,因而廣泛地使用在模擬集成電路系統中。然而,Mc作為輸入級的共柵管,受功耗限制其跨導gmc不可能無限大。當該電路驅動大的容性負載時,傳輸函數存在共軛復極點且極點的位置和品質因數Q的值由gmc和CC決定。因此,如果電路參數設計不當,增益特性曲線將會在單位增益附近出現頻率尖峰,造成相位損失,嚴重影響運放的閉環穩定性和建立特性。同時在低功耗設計中,使用Class?A型放大器作為輸出級會使得負擺率嚴重受限。

2? 亞閾值有源共源共柵補償

2.1? 電路結構

本文提出的SACC跨導運算放大器電路結構如圖2所示。每級輸出端的輸出電阻和集總寄生節點電容分別用R和C表示;CC是密勒補償電容,和有源共源共柵結構形成反饋網絡;k為工作在亞閾值區域的輔助運放,以非常低的功耗成本提高共柵晶體管的等效跨導gmc;CL為負載電容;跨導級gm1和gm2構成兩級跨導放大器。從輸入到輸出的前饋級gmf僅在放大器的高頻部分產生左半平面零點,它可以在不影響頻率響應的情況下改善瞬態響應。與傳統的共源共柵放大器相比,在驅動相同的負載電容時,所提出的SACC結構可以顯著地減小補償電容CC的數值,因而可以大幅改善放大器的帶寬,同時可以減小大的補償電容所帶來的物理版圖面積消耗。動態前饋級與輸出級構成推挽輸出結構,使得SACC放大器在帶來瞬態性能顯著改善的同時在穩定狀態下保證了低的功耗。反饋網絡通過改進的共源共柵補償方案實現,包括補償電容器CC、跨導級gmc和亞閾值輔助運放k,相比于傳統的共源共柵補償方案,由于輔助運放提高了共柵晶體管的等效跨導gmc,因而可以把反饋網絡所引入的左半平面零點推到更高的頻率。

2.2? 傳輸函數

本文提出的SACC放大器的小信號模型如圖3所示。研究電路的傳輸函數,以分析SACC放大器的穩定性。

使用以下假設導出傳遞函數:

1) 反饋跨導級的輸入電阻等于其跨導的倒數;

2) 每一級的增益都遠大于1;

3) 電容C1,C2和CC都遠小于CL。

根據以上假設,電路的傳輸函數為:

低頻增益Adc和主極點P-3 dB分別為:

因此單位增益帶寬積為:

根據傳輸函數式(1)可以確定非主極點為共軛復極點以及其對應的Q值:

式(5)和式(6)表明共軛復極點的位置和品質因數Q控制著放大器的穩定性,其值依賴于gmc,gm2,CL和k。由于增加了輔助放大器,共軛復極點的位置可以更容易地到更高頻率,并且Q值也因此變得很小。這里k為輔助運放的增益,其值一般不能太大,因為輔助放大器會放大共柵管的柵源寄生電容Cgs,過大的k會把共柵管源端帶來的極點由高頻移到低頻處,惡化放大器的穩定性。在本設計中k為4.5。

從傳輸函數還可以看出SACC放大器存在兩個左半平面的零點,如下:

由于gmf和gm2處在相同的量級,C1為寄生電容且小于CC,所以z1與單位增益帶寬的比例約為CC/C1,最終左半平面零點z1可以補償非主共軛復極點帶來的相位損失。同時,共柵晶體管的等效跨導gmc被等效放大為原來的k+1倍,因此z2出現在非常高的頻率,其影響可以忽略。

2.3? 穩定性分析

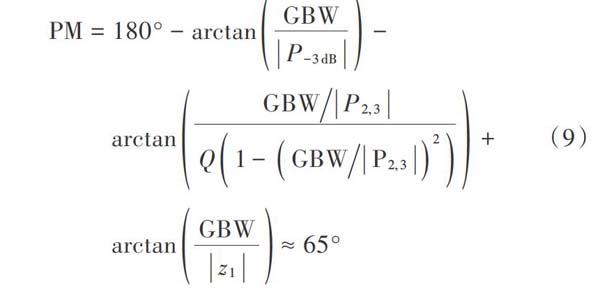

根據電路的傳輸函數可知,存在非主導共軛復極點,其帶來的相移取決于它的位置和Q值。為了避免產生頻率“尖峰”,建議Q的值[10]取為[12]。在所提出的電路中,為保證電路的穩定性,使得相位裕度大于60°,因此必須滿足|P2,3|≥2GBW,同時令z1≥4GBW。根據上面的條件可以容易得到gmc,gmf和CC的取值約束。相位裕度PM為:

根據上面的討論,合理設置零極點的位置,可以看出,SACC放大器相位裕度大于60°,滿足工程上的穩定性要求。同時如果建立時間不足,可以對參數k、補償電容CC進行適當的調整,增大相位裕度。

2.4? 擺率分析

由于電路的內部寄生電容遠小于CC和CL,因此限制擺率的主要因素為對補償電容和負載電容充放電的電流大小。由于gmf和gm2構成推挽輸出結構,其正負擺率都很大,所以SACC放大器的擺率主要受限于驅動補償電容CC的第一級電路。擺率公式為:

式中,I1為可用于對CC充放電的電流量。從式(10)可以得出提高擺率可以通過提高I1或者減小CC。在提出的結構中,由于增加了輔助運放,使得補償電容相比于傳統共源共柵補償大大減小。因此,SACC放大器的內部壓擺率在給定的條件下得到提升。

3? 放大器的電路實現

圖4顯示了所提出的SACC放大器的電路實現。折疊式有源共源共柵跨導放大器構成了輸入級,由M2~M9組成,差分對M2,M3決定第一級的跨導gm1。同時跨導提升輔助運放由晶體管Ma1~Ma3和Mb1~Mb3組成。其中,晶體管Ma1,Ma3,Mb1和Mb3工作在亞閾值區域。該輔助運放的增益決定了補償電容的數值。

第二級的跨導gm2由M13決定,M10~M12構成動態前饋級,其等效跨導為gmf ,與M13構成推挽輸出。CC為金屬?氧化物?金屬(MOM)補償電容,CL為輸出外部負載電容。Vb是由偏置電路提供的偏置電壓,圖中沒有給出偏置電路。

4? 仿真結果

所提出的SACC放大器在28 nm CMOS工藝下設計并仿真驗證。當電源電壓為0.9 V,所提出的運算放大器消耗靜態電流僅為5.14 μA。負載電容為10 pF時,驗證電路的頻率特性。仿真結果如圖5所示,從圖中可以看出所提出的運算放大器直流增益為69.5 dB,單位增益帶寬積為13.3 MHz,相位裕度為61.1°。

將圖4所示電路連接成單位增益模式,輸入峰峰值為200 mV,周期為8 μs,占空比為50%的方波信號,輸出瞬態波形如圖6所示。可以看出在沒有添加動態前饋級電路時,輸出波形在下降時不能跟隨輸入信號,且SR-=0.12 V/μs。在添加動態前饋級電路后,從圖中可以看出負擺率顯著改善,是之前的25倍,此時SR+=5.1 V/μs,SR-=3.0 V/μs。

本文提出的SACC放大器與現有放大器的關鍵性能參數對比如表1所示。工程上用FOM值來衡量不同放大器的性能,兩個品質因數用來評估放大器的小信號和大信號性能指標,分別由式(11)和式(12)給出。

由于不同設計的電源電壓不同,為了比較其性能,引入與電源電流相關的品質因數,分別由式(13)和式(14)給出。

從表1可以看出,與之前提出的補償方案相比,本文提出的SACC放大器顯然具有出色的FOM和IFOM,這表明所提出的SACC結構具有更好的功率帶寬效率。此外,所提出的SACC結構還實現了最高的負載電容CL與補償電容CC比率。這表明SACC放大器是一種面積能效優化的補償方案,在驅動小的容性負載具有顯著的優勢。

5? 結? 論

本文面向低壓低功耗應用領域提出一種新型的SACC放大器。SACC補償方案使用小的補償電容在低電壓低功耗約束條件下把與帶寬相關的非主共軛復極點推到高頻,同時減小品質因數Q值,改善放大器的穩定性。由輸入到輸出的動態前饋級與輸出級構成推挽結構,以低的靜態功耗顯著改善擺率。仿真結果表明,提出的放大器與現有的方案相比較具有更好的小信號和大信號性能指標。同時具有所有補償方案中最高的CL/CC值,表明此方案的有效性,可以應用于模擬集成電路系統中。

注:本文通訊作者為王夢海。

參考文獻

[1] AMINZADEH H, NABAVI M R, SERDIJN W A. Low?dropout voltage source: an alternative approach for low dropout voltage regulators [J]. IEEE transactions on circuits and systems II: express briefs, 2014, 61(6): 413?417.

[2] ANDREOU C M, KOUDOUNAS S, GEORGIOU J. A novel wide?temperature?range, 3.9 ppm CMOS bandgap reference circuit [J]. IEEE journal solid?state circuits, 2012, 47(2): 574?581.

[3] MALHOTRA S, MISHRA A, RAKESH B R, et al. Frequency compensation in two?stage operational amplifiers for achieving high 3?dB bandwidth [C]// 2013 IEEE Asia Pacific Conference on Postgraduate Research in Microelectronics and Electronics. Visakhapatnam: IEEE, 2013: 107?110.

[4] ABDULAZIZ M, TORMANEN M, SJOLAND H. A compensation technique for two?stage differential OTAs [J]. IEEE transactions on circuits and systems II: express briefs, 2014, 61(8): 594?598.

[5] NAJJARZADEGAN M, JALILI A, DEHGHANI R. A high?speed, high?gain OTA structure with a new compensation technique [C]// 2015 23rd Iranian Conference on Electrical Engineering. Tehran: IEEE, 2015: 1332?1335.

[6] RAJ A, YADAV R, AKASHE S. Frequency compensation in two stage operational amplifier using common gate stage [C]// 2015 International Conference on Communication Networks. Gwalior: IEEE, 2015: 155?159.

[7] PAKALA S H, MANDA M, SURKANTI P R, et al. Voltage buffer compensation using Flipped Voltage Follower in a two?stage CMOS op?amp [C]// 2015 IEEE 58th International Midwest Symposium on Circuits and Systems. Fort Collins: IEEE, 2015: 1?4.

[8] SINGH S I. Design of low voltage CMOS two stage operational transconductance amplifier [C]// 2017 International Conference on Electrical, Electronics, Communication, Computer, and Optimization Techniques. Mysuru: IEEE, 2017: 248?252.

[9] ZHOU Qianneng, LI Hongjuan, DUAN Xiaozhong, et al. A two?stage amplifier with the recycling folded cascode input?stage and feedforward stage [C]// Proceedings of 2011 Cross Strait Quad?Regional Radio Science and Wireless Technology Conference. Harbin: IEEE, 2011: 1557?1560.

[10] GUO Song, LEE Hoi. Dual active capacitive feedback compen?

sation for low power large capacitive load three stage amplifiers [J]. IEEE journal of solid?state circuits, 2011, 46(2): 452?464.