基于ADF4360-0的2.4 GHz射頻信號源設計

摘要:在現代無線通信系統中,對數據的高速無線傳輸需求日益增加,而且無線路由器、藍牙等技術也在生活中有著廣泛的應用,故而對于2.4 GHz頻段的信號源的需求越來越多。但是,除了一些在2.4 GHz頻帶產生信號的高端信號發生器外,平常使用的信號源很少會涉及2.4 GHz這一頻段,因此,為滿足科學和教育的需要,設計和研發了一款便宜可靠的2.4 GHz射頻信號發生器,并對其實現與仿真進行了介紹。

關鍵詞:2.4 GHz;射頻信號源;壓控振蕩器

0? ? 引言

在電子通信系統中,如果想實現更大的帶寬,我們只能通過使用更高的載波頻率來滿足要求。在無線通信中,需要使用天線來發送和接收信號,工作頻率越高,天線的尺寸就越小,滿足了小型化的通信要求。由于整體趨勢是朝著寬頻率覆蓋、高精度、多功能以及自動化和智能化的方向發展,當今電子領域更多的電子通信系統使用更高頻率的射頻,這促進了豐富的射頻應用,并帶動了射頻技術的進一步發展[1]。

1? ? 相關原理概述

壓控振蕩器(VCO)的定義為輸出頻率對應于輸入控制電壓的振蕩電路,其在無線測量儀器和通信系統電路中使用廣泛。VCO作為鎖相環電路和時鐘恢復電路的主要組成部分,其性能可以直接影響到頻率源的性能,這又決定了整個系統輸出信號的穩定性、噪聲特性和諧波抑制特性。正是由于這些因素,VCO在電子通信技術領域發揮著重要作用。因其具有電子調諧、緊湊、低功耗和高可靠性等優點,關于VCO的研究很多。近年來,隨著集成電路的快速發展,VCO的設計和實現逐漸融入其中,集成式VCO使用方便、性能穩定[2]。

2? ? 關于ADF4360-0的介紹

在ADF4360系列鎖相環中,我們需要在芯片ADF4360-7和ADF4360-8的外部去設置兩個電感,作用是方便確定VCO所處頻段,這個操作步驟就相當于從芯片中將VCO的電感移除。兩個0603電感不占用太多的體積,但有兩點需要注意:一是電感和ADF4360芯片之間以及接地層之間的連接必須盡可能短,并且電感必須使用線繞測試(例如使用Coilcraft 0603CS系列的射頻電感,如果使用普通的堆疊電感,則VCO不會振動);那么,ADF4360的每個電源引腳必須分別用102和104的陶瓷電容去耦,這就成為了另一個問題。

在硬件電路設計之前,需要仔細確定原理圖參數和各個元件,原理圖可以直接復制ADF4360應用筆記,當然在引腳附近還應該加上相應的去耦電容,為保證電源的穩定性,MIC5527和MIC5565LDO低噪聲控制可用于提供電源。需要注意的是,電源紋波過大且功率集中在特定頻率點上會使AM寄生分量達到ADF4360的輸出,對于這樣的情況,我們必須采取方法做到完全消除。此外,需要根據元件參數確定ADF4360的參數,包括VCO電感(僅限ADF4360-7、ADF4360-8)和環路濾波器,這兩個參數可以使用Applied Radio Labs提供的ADISimPLL仿真軟件來確定。相位噪聲是我們在使用仿真軟件的時候,需要關注的一點。

3? ? 電路設計

3.1? ? 設計要求

本文中,我們所要設計的信號發生器,其頻率的工作范圍需要控制在2.3~2.6 GHz范圍內[3]。因為只有將工作范圍控制在此頻率范圍內,我們最終得到的電路,其輸出才會是中心頻率為2.4 GHz的等幅信號。因此,我們可以得到以下參數:電路的總輸出相位噪聲應當小于-100 dBc/Hz,并且電路相位輸出誤差應當小于15°[4]。

3.2? ? 電路的PCB設計

首先,為了便于焊接,在控制芯片封裝時,芯片引腳的焊盤應比實際尺寸長0.5 mm和寬0.05 mm;其次,應盡可能在RF信號線、焊盤和芯片周圍增加接地銅皮,并連接到主接地端。此外,為了減少時鐘信號的干擾,可以對時鐘線進行封裝和處理;最后,在設計的過程中,為了減少信號反射,可以將ADF4360-0 RF的輸出線阻抗設置為50 Ω[5]。

3.3? ? 仿真結果

使用ADISimPLL對該電路進行仿真。

在計算環路濾波器的電阻和電容參數時,系統自動生成環路濾波器參數仿真原理圖。通過對圖中設備參數的分析可知,仿真結果滿足我們設計的頻率要求。通過時域環路濾波器的輸出相位誤差圖可知,大約在1.75 ms后,可以滿足設計要求,環路濾波器的輸出相位誤差為0。

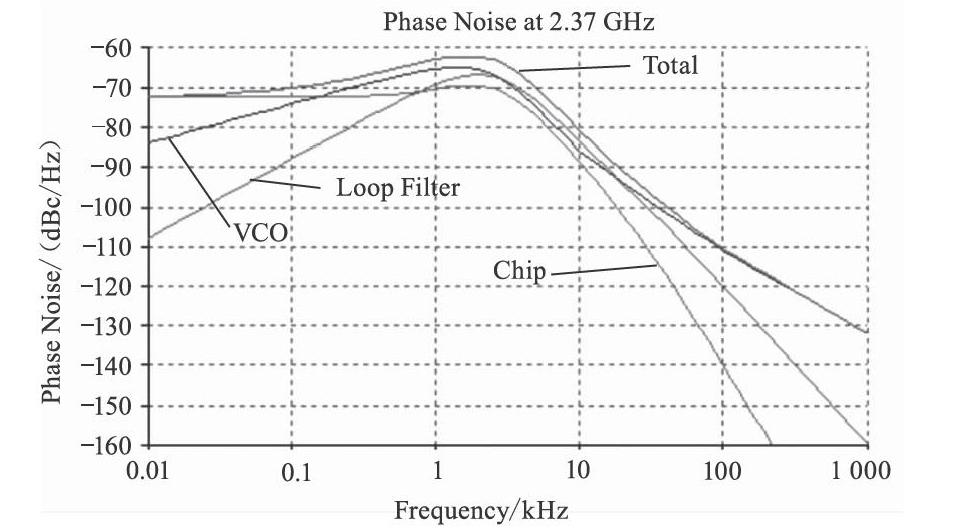

圖1中包括環路濾波器、芯片本身、內部VCO以及2.37 GHz處的總相位噪聲與頻率之間的關系。我們可以從圖中清楚地看到,當頻率大于1 MHz時,所有的相位噪聲都處于-160 dBc/Hz附近,這就表明該設計符合我們之前的設計要求。

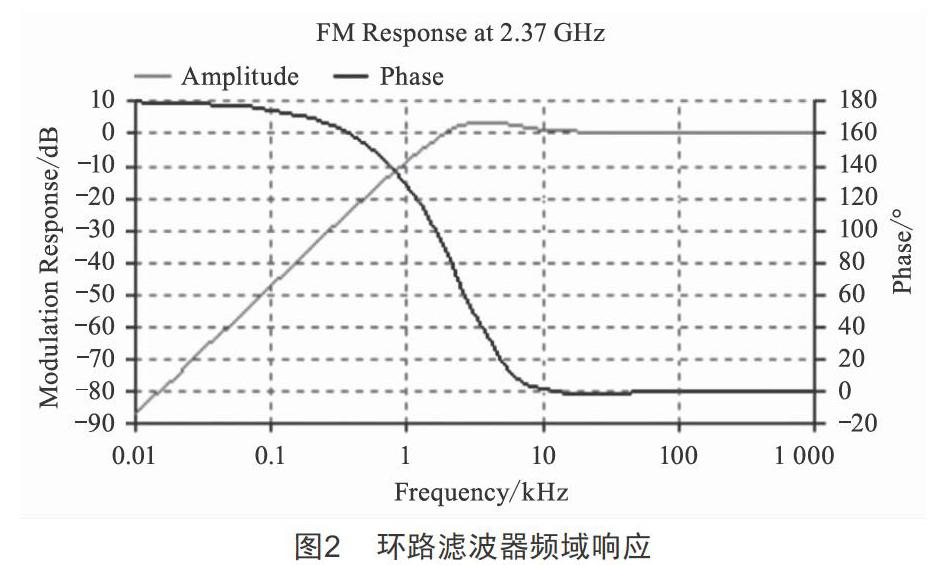

如圖2所示,從圖中我們可以明顯看出,當頻率超過10 kHz的時候,掃描信號發生器的輸出保持恒幅信號不變,此時相位也保持不變,因為工作頻率要求為2.4 GHz,這就表明該設計可以滿足我們的設計要求[6]。

4? ? 結語

在此設計中,ADF4360-0輸出掃描信號的中心頻率設置為2.4 GHz,由于通過常規方法生成RF信號源非常困難,因此設計掃頻發生器與頻率合成器ADF4360-0。通過仿真分析,我們可以得出結論:該設計可以滿足我們的設計要求。

[參考文獻]

[1] 樊秀云,張合敏.基于DDS的掃頻信號發生器[J].山西電子技術,2002(5):33-35.

[2] 沈偉,文必洋,馬志剛,等.基于ADF4360-7的寬帶雷達信號源設計[J].現代雷達,2006,28(8):39-42.

[3] Integarted Synthesizer and VCO ADF4360-0.Pdf ANALOG DEVICES[Z].

[4] 陳景文.基于ADF4360_4鎖相頻率合成器的混頻器本振源電路設計[J].電子元器件應用,2007,9(10):27-29.

[5] 魏洪興.嵌入式系統設計師教程[M].北京:清華大學出版社,2006.

[6] ADSP-BF533 EZ-KIT LiteTM Evaluation System Manual, ANALOG DEVICES[Z].

收稿日期:2019-12-12

作者簡介:陳肇南(1995—),男,安徽淮南人,安徽理工大學在讀碩士,研究方向:電氣工程。