基于FPGA的時鐘同步功耗信息采集方法

宋 安,王 琴,谷大武,郭 箏,1b,劉軍榮,2,張 馳

(1.上海交通大學a.電子信息與電氣工程學院; b.網絡空間安全學院,上海 201100;2.智巡密碼(上海)檢測技術有限公司,上海 201100)

0 概述

旁路攻擊(Side Channel Attacks,SCA)是一種通過利用芯片泄露的物理信息并對其進行統計分析以獲得芯片內部敏感信息的攻擊方法[1]。旁路攻擊主要手段為功耗分析,是通過采集密碼系統運行時的功耗信息,并利用統計學和信號處理的方法找出數據中與密碼算法執行有關的信息,再結合電路的運行特征進行密鑰破解[2]。功耗分析是旁路攻擊研究的核心內容,而功耗采集則是功耗分析的基礎[3]。

傳統的采集方法是用示波器對待測芯片進行異步采集,即示波器的采集時鐘與待測芯片的時鐘完全獨立[4],示波器的采集時鐘一般使用內置的高頻時鐘,待測芯片的工作時鐘來源于晶振,因此采集時鐘和待測芯片工作時鐘之間存在不穩定的相位差。由于待測芯片多數在時鐘邊沿執行密碼運算,傳統的異步采集方法很難完全采集到待測芯片的密碼操作相關信息。為了得到充足的時鐘邊沿信息,傳統的異步采集方法需要增大示波器的采樣頻率,但同時獲得了大量冗余信息,增加了旁路分析的復雜度。此外,傳統異步方法采集的功耗信息的觸發時間是不對齊的,這極大地增加了旁路分析的時間成本。由文獻[5]可知,異步采集的功耗信息使得功耗分析難以完成。

針對以上問題,文獻[4]通過彎曲的磁線對待測芯片的功耗進行采集,嘗試獲得精準的功耗信息。文獻[5]通過電源注入的方法強制使內部振蕩器的頻率鎖定于外部時鐘的頻率。文獻[6]設計了包含鎖相環(Phase Lock Loop,PLL)的放大濾波電路,嘗試恢復出待測芯片內部的工作時鐘。然而,以上研究存在著明顯局限性:測評者需要熟悉待測芯片泄露功耗的電路,精確定位功耗泄露的采集位置,這是一項復雜且難度很高的工作[4];目前多數芯片使用穩定的晶振作為時鐘源,無法與外部時鐘鎖定,且未進行后續的旁路采集和功耗分析驗證,缺乏實驗支撐[5];由于存在放大和濾波通路,恢復出的時鐘會隨著待測芯片原本的工作時鐘的變化而產生不穩定的相位延時[6]。此外,文獻[4,6]的方法需要在專用的采集平臺(如Chipwhisper硬件[7])上實現,可供選擇的測評參數有限,并不適用于實際的測評。

為改善以上問題,需要一種通用的采集方法和采集平臺,既可大幅提升功耗分析的成功率,又能廣泛地應用在實際的測評中。為此,本文提出一種基于FPGA的時鐘同步功耗信息采集方法。

1 基于FPGA的時鐘同步設備的硬件實現

現場可編程門陣列(Field Programmable Gate Array,FPGA)具有速度快、效率高、組成形式靈活以及內部時延小的特點,可以大幅提升系統對信號的響應和處理時間,并且能進行現場設計、編程等,在高速數據處理方面起到了關鍵作用[8]。因此,本文選用FPGA進行硬件實現,設計了基于FPGA的時鐘同步設備,為數字示波器和待測設備提供狀態同步、相位可調、頻率可變、驅動能力強的時鐘信號。基于FPGA的時鐘同步設備具有以下優勢:

1)FPGA內部時鐘資源非常豐富,可構建穩定的多時鐘系統,內部產生的時鐘信號可通過眾多的時鐘管腳引出。

2)FPGA內置鎖相環模塊,內部時鐘的頻率和相位可調,測評者可根據需求自行調節,以滿足各種功耗信息采集場景的需求。傳統的采集方法中測評者難以控制待測設備和示波器的時鐘頻率和相位差。然而在基于FPGA的時鐘同步采集系統下,測評者可方便配置待測設備和示波器的時鐘頻率和相位,來獲得更高信噪比的功耗曲線,以達到最佳的采集效果。

3)FPGA可拓展性強。待測設備和示波器對外部信號的驅動能力有一定要求,若外部信號電平過低或不穩定會造成驅動不足的問題。本文采用的FPGA開發板的I/O管腳電平為3.3 V,且封裝良好,滿足待測設備和示波器對外部信號驅動能力的要求。

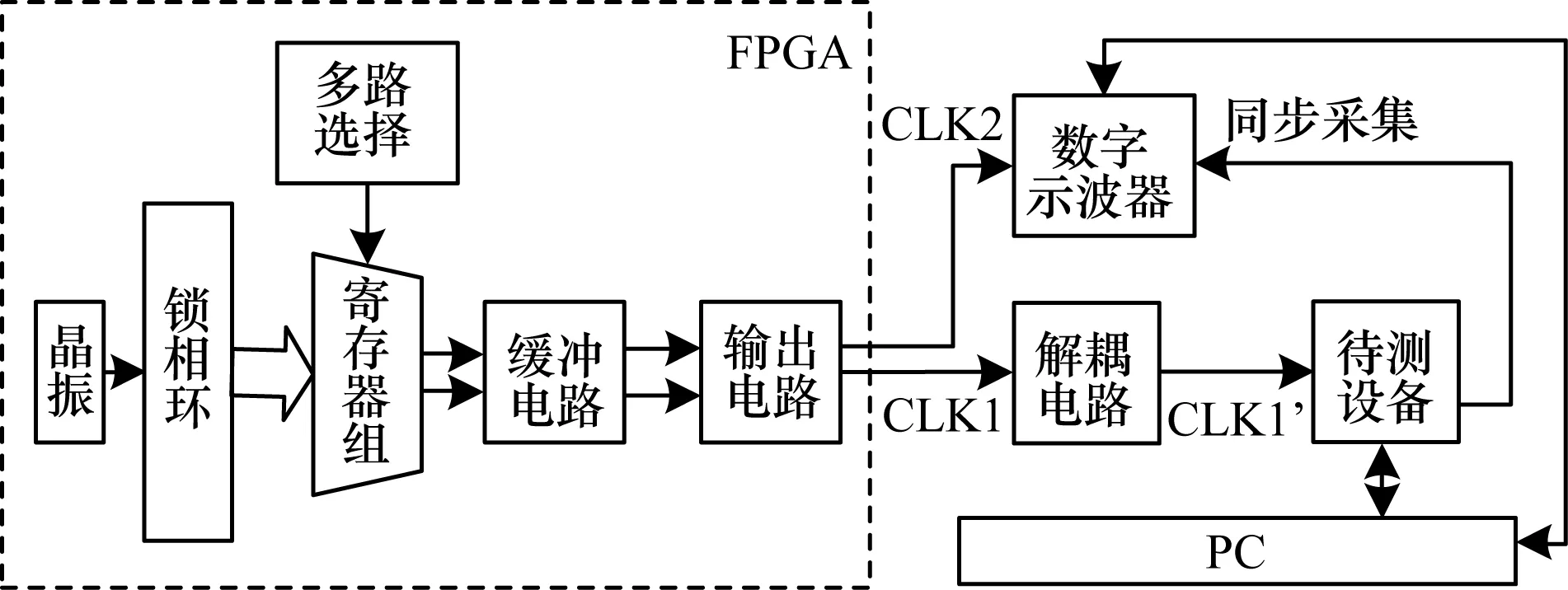

在本文的采集方法中,基于FPGA的時鐘同步設備產生狀態同步(即相位差穩定)的時鐘CLK1和CLK2,作為數字示波器的采集時鐘,經過解耦電路后作為待測設備的工作時鐘,然后進行后續的采集。

時鐘同步設備的硬件實現如圖 1的虛線框所示。狀態同步時鐘產生的基本原理是:來自晶振的時鐘經過鎖相環電路產生多個輸出時鐘,全部存儲到寄存器組中;多路電路選擇寄存器組中的時鐘后,經過緩沖電路、輸出電路,由設備的I/O引出。

圖1 時鐘同步采集系統

硬件的設計基于硬件描述語言Verilog HDL,采用的EDA平臺為Xilinx公司的Vivado套件[9],FPGA開發板采用Airtex-7系列FPGA的 Basys3開發板[10]。保證狀態同步的時鐘的正確產生是硬件設計的關鍵。硬件設計包含以下關鍵電路:

1)鎖相環電路

若采用邏輯電路來產生時鐘信號,時鐘信號的相位將不穩定,且在實際的電路中會存在毛刺和抖動。然而,鎖相環電路能很好地解決這一問題。鎖相環電路不僅為FPGA提供靈活可變的時鐘,還有消除時鐘抖動和抗時鐘歪斜的作用。鎖相環電路包括鑒相器、環路濾波器、壓控振蕩器、分頻器等。首先鑒相器比較輸入時鐘和分頻器的反饋時鐘的相位和頻率,產生比例信號。然后比例信號驅動環路濾波器,并把參考電壓傳輸到壓控振蕩器,以此決定壓控振蕩器是否運行在更高或更低的頻率[11]。

本文鎖相環電路的實現調用了Vivado內置的IP核,在配置分頻和倍頻等參數后,得到多個頻率的輸出時鐘。

2)多路選擇電路

多路選擇電路提供選擇信號,用于控制產生不同頻率和相位的時鐘信號,保證了時鐘信號的可調性。對于Airtex-7系列FPGA,鎖相環電路最多提供6個時鐘輸出,進入寄存器的多個時鐘等待多路選擇電路的控制信號,最后產生兩個輸出時鐘。

多路選擇電路的實現用到了累加器,每當外圍電路的按鍵按下時,多路選擇電路的選擇信號就累加一次,將累加結果作為選擇信號。

3)緩沖電路和輸出電路

緩沖電路用于保證各電路之間時鐘信號的正常驅動。輸出電路的作用是將FPGA內部產生的時鐘通過I/O引出。

緩沖電路調用了Vivado內置的buffer函數;輸出電路調用了原語,在配置雙倍數據速率輸出(Output Double Data Rate,ODDR)電路參數后,實現了FPGA內部邏輯電平到輸出模擬時鐘的轉換。

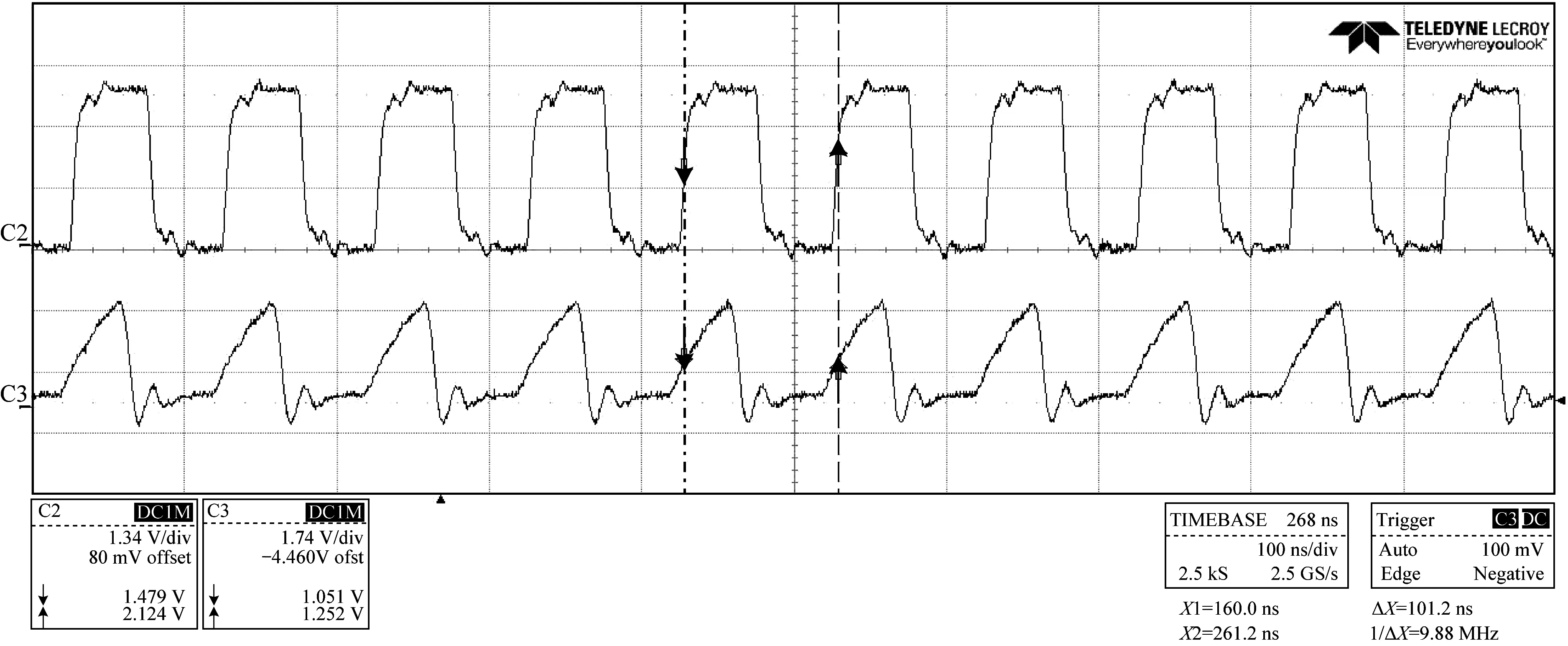

在完成基于FPGA時鐘同步設備的硬件設計后,編譯Verilog代碼,并將編譯后產生的比特流文件通過JTAG下載到Airtex-7 FPGA的Basys3中。用數字示波器對圖1的CLK1’(經過電氣解耦后的CLK1)、CLK2信號進行檢測,結果如圖2所示。其中,C2信道為采集參考時鐘CLK2,C3信道為工作時鐘CLK1’,其相位差穩定在-1°~+1°范圍內。

圖2 采樣時鐘與工作時鐘

2 同步采集平臺設計

本文選擇專用安全FPGA芯片SAKURA-G作為待測設備。SAKURA-G開發板用于硬件安全領域的研究和開發,如旁路攻擊、故障注入攻擊、物理不可克隆函數等[12]。

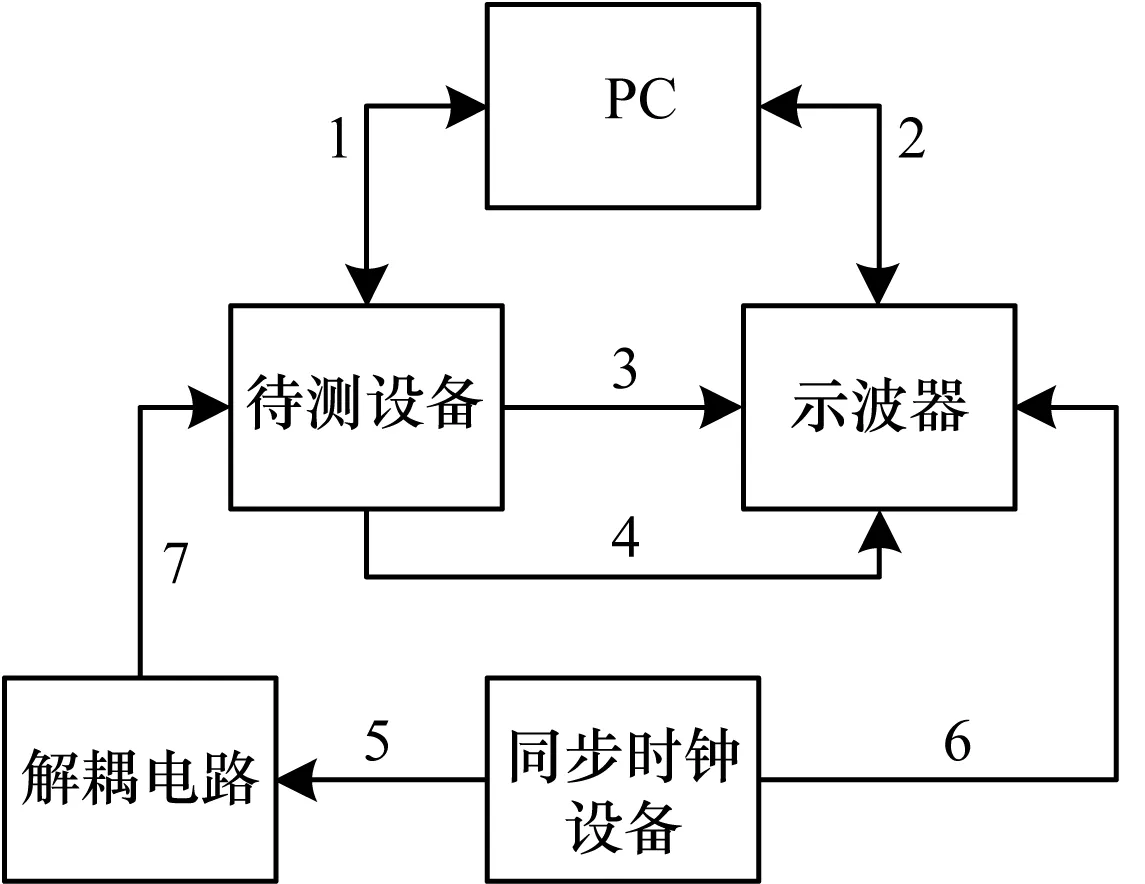

與傳統采集方式相比,本文設計的同步采集方法主要在待測設備和示波器上體現差異。在傳統方法異步采集時,待測設備的工作時鐘來源于晶振,而在同步采集時,待測設備的工作時鐘由基于FPGA的時鐘同步設備提供并通過SAKURA-G上的I/O引腳引入。傳統方法異步采集時,示波器一般使用內置的采集時鐘,而在同步采集時,數字示波器的采集時鐘由基于FPGA的時鐘同步設備提供并通過示波器外部組件WR6Zi-ExtRef-IN/OUT[13]引入。該組件可以接受外部參考時鐘,使內部采集時鐘與外部參考時鐘相位一致,且示波器內部采集時鐘頻率可任意調節,如圖3所示。

圖3 實驗采集流程

本文設計的同步采集步驟如下:

步驟1按照測評需求調節時鐘頻率的大小(由外圍電路按鍵控制),時鐘同步設備產生CLK1(序號5),經過解耦電路后的CLK1’作為待測設備的工作時鐘(序號7);時鐘同步設備產生CLK2,經過幅值調整后作為示波器的采集參考時鐘(序號6)。

步驟2PC向待測設備發送明文(或密文)、隨機數等指令,等待待測設備傳回密文(序號1)。

步驟3待測設備開始加密(或解密),將觸發信號傳給示波器(序號3)。

步驟4PC向示波器發送采樣率、觸發延時、幅值分量等參數,等待示波器傳回功耗曲線(序號2)。

步驟5示波器對待測設備的功耗進行采集(序號4)。

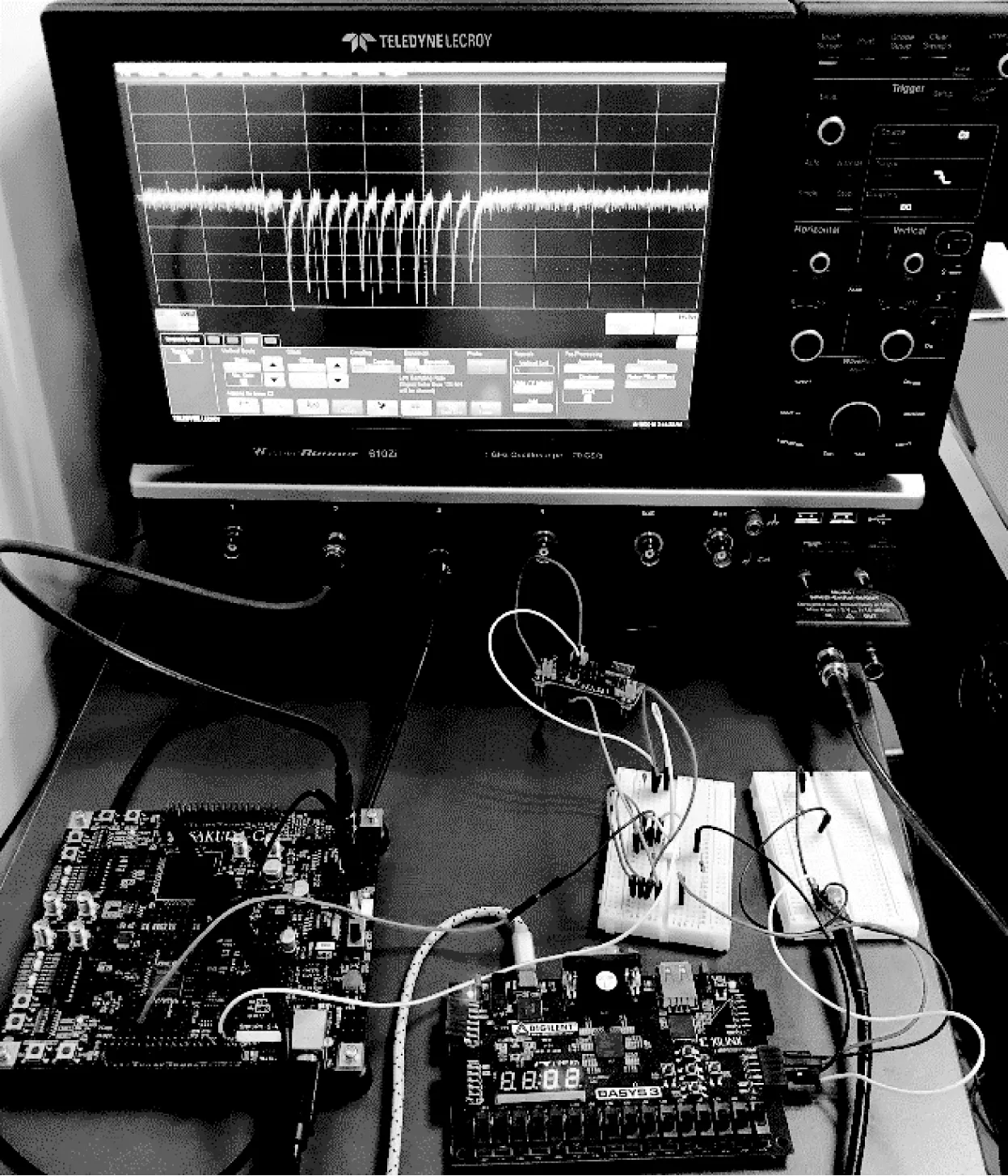

傳統的異步采集方法包含序號1~序號4,最終采集到的功耗曲線信噪比較低。本文的同步采集在傳統異步采集方法的基礎上增加了序號5~序號7部分,不僅實現了同步采集,還解決了噪聲問題。按照設計的同步采集方法搭建采集平臺,同步采集示意圖如圖4所示。

圖4 同步采集示意圖

3 實驗設計與分析

為驗證本文提出的同步采集方法的效果,本文的實驗設計主要基于相關功耗分析(Correlation Power Analysis,CPA)攻擊。

3.1 CPA攻擊

CPA是一種非建模類的功耗分析方法[14]。CPA攻擊由差分功率分析(Differential Power Analysis,DPA)[15]演變而來,在本文實驗場景下,相比其他功耗分析方法,如SPA[16]、TA[17]等,CPA更加快速和有效。

vi,j=Sbox(di⊕kj)

(1)

li,j=L(vi,j)

(2)

(3)

3.2 無防護AES功耗曲線的CPA攻擊

同步采集對異步采集的提升率計算公式可以表示為:

(4)

其中,Cs表示異步功耗曲線的密鑰相關性,Ca表示同步功耗曲線的密鑰相關性。

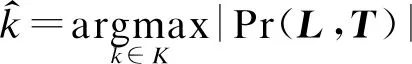

選擇10 000條無防護的AES功耗曲線(待測芯片工作頻率為10 MHz)進行單字節功耗分析,分析平臺為Matlab[18]。圖5(a)給出示波器采樣率為25 MS/s時異步和同步采集的功耗曲線的密鑰相關性示意圖。灰色實線代表錯誤密鑰的相關性,黑色虛線表示異步的正確密鑰的相關性曲線,黑色實線表示同步的正確密鑰的相關性曲線(圖5(b)、圖5(c)、圖5(d)的表示相同)。黑色虛線在時刻45附近出現了尖峰,最高相關性-0.03左右,但未與灰色實線區分開。黑色實線在時刻45附近產生了明顯的尖峰,最高相關性提升至-0.05,且泄露點數量增加。按照式(4),同步采集的功耗分析的提升率δ為66.7%。

圖5(b)給出示波器采樣率為100 MS/s時異步和同步采集的功耗曲線的密鑰相關性示意圖。在時刻255附近,黑色虛線的最大相關性為-0.10,而黑色實線的最大相關性提升到-0.13,同步采集的提升率δ為30%。

圖5 不同采樣頻率的CPA攻擊結果

3.3 帶防護DES功耗曲線的CPA攻擊

DES的分析與AES類似,由于DES算法存在掩碼防護,需要更多的功耗曲線。在此場景下,選擇150 000條功耗曲線(待測芯片工作頻率為10 MHz)進行單字節功耗分析,分析平臺為Matlab。圖5(c)給出示波器采樣率為25 MS/s時異步和同步采集的功耗曲線的密鑰相關性示意圖。黑色虛線的相關性最大值為-0.075,黑色實線的相關性最大值達到-0.10。按照最高相關性計算提升率,同步采集的功耗分析的提升率δ為33.3%。

圖5(d)給出了250 MS/s異步和同步采集的相關性示意圖。黑色虛曲線最大相關性為-0.16,且在時刻105和時刻120時與灰色實線有所重疊。黑色實線最大相關性提升到-0.19,在時刻105和時刻120仍與錯誤曲線有很好的區分度,信息泄露更為明顯。同步采集的功耗分析的提升率δ為18.75%。

3.4 結果分析

3.2節、3.3節分別對AES和DES進行單個字節的CPA攻擊,本節將給出所有字節的CPA攻擊的綜合結果。

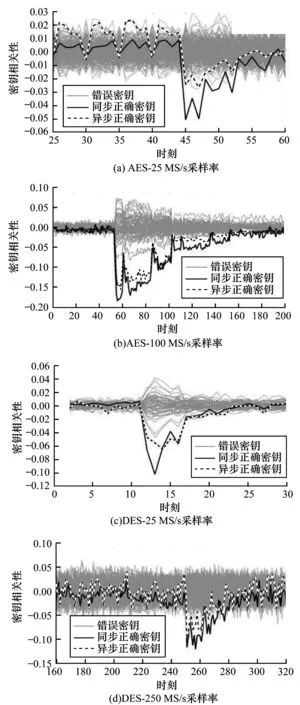

以圖5(b)中時刻250處的泄露點進行CPA分析為例(以5(a)、圖5(c)、圖5(d)為例也能得到類似的結論),結果如圖6所示。其中,橫坐標表示功耗曲線數量,縱坐標表示密鑰相關性,每一條曲線代表每一種假設密鑰的相關性。

圖6 相關性與曲線數量的關系

當功耗曲線數量較少時,虛線和實線都未能與灰色曲線區分;隨著使用功耗曲線的數量增加,正確曲線的相關性與錯誤曲線區分增大。當功耗曲線數量達到600條時,正確密鑰曲線開始與錯誤曲線區分,最終灰色曲線的相關性的收斂于±0.06,虛線的最高相關性為-0.08,實線的最高相關性為-0.12。

從圖6還可以發現,虛線在曲線數量為1 800時與灰色曲線有重合部分,然而實線從500條開始就與錯誤曲線產生了良好的區分度。結果表明,本文采用的同步采集比異步采集更容易產生泄露,只需利用較少的功耗曲線即可攻擊出正確密鑰。

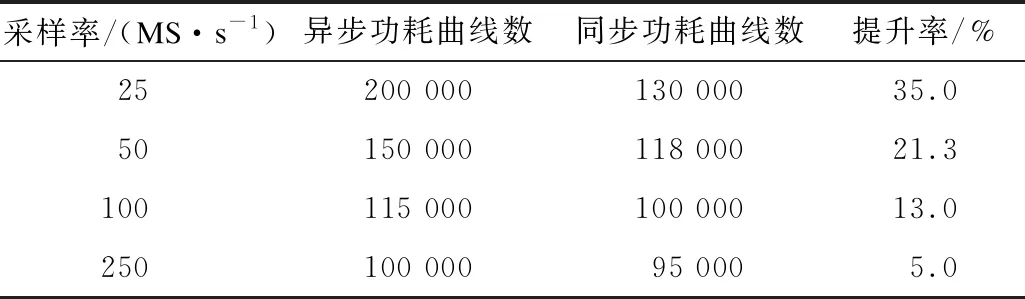

上文為單字節CPA分析,下面將剩余所有字節進行CPA攻擊,統計攻擊出所有正確密鑰所需的曲線數如表1、表2所示(考慮實驗環境對功耗曲線的微小影響,表中曲線數為多次實驗統計的近似結果)。其中,表1 是未防護的AES算法的攻擊結果,表2是帶防護的DES算法的攻擊結果。

表1 未防護的AES的攻擊結果

表2 帶防護的DES的攻擊結果

如表1所示,當示波器的采樣率為250 MS/s時,同步采集的功耗分析提升率為7.1%,這是由于采樣率遠高于待測芯片工作時鐘后,每條功耗曲線的泄漏點增多,異步采集的不良效應被稀釋。然而,隨著示波器采樣率的降低,提升率迅速上升,在采樣率為25 MS/s時產生了最佳的效果,同步采集相比異步采集減少了37.5%的功耗曲線數量。

表2與表1的結果類似。當示波器采樣率為250 MS/s時,功耗曲線的CPA攻擊提升率為5.0%。隨著示波器采樣率的降低,提升率迅速上升,在采樣率為25 MS/s時產生了最佳的效果,同步采樣相比異步采樣減少了35.0%的功耗曲線數量。

3.5 信噪比

在早期實驗時發現采集過程中出現明顯的噪聲,這是由于待測芯片使用了外部時鐘。較差的信噪比將影響功耗分析的成功率。下文討論耦合噪聲對功耗曲線的影響。

每條功耗曲線lk都由n個功耗點組成,公式表達如下:

(5)

其中,lk(t)為示波器在第t時刻采集的功耗點的值,它的大小由待測芯片中的密碼算法產生的中間值δ(t)和噪聲ε決定,即:

lk(t)=δ(t)+ε

(6)

其中,δ(t)為S盒的輸出產生的功耗,與明文和密鑰k相關,ε的大小獨立于δ(t),與外部設備的時鐘頻率相關(暫不考慮待測芯片內部的其他噪聲)。在給定的場景中,功耗曲線lk第t個點的信噪比的計算公式如下[19]:

(7)

其中,Var(·)表示方差,Var(δ(t))量化了可利用的信號造成的功耗點的變化大小,Var(ε)量化了由噪聲導致的該點的變化。

為提升功耗曲線的信噪比,有以下兩種減少ε的方法:1)為外部時鐘設備提供高質量的穩壓電源,把電源噪聲的影響降至最低,但此方法對信噪比的改善不明顯;2)對時鐘信號進行電氣解耦處理,屏蔽其對待測芯片的影響。

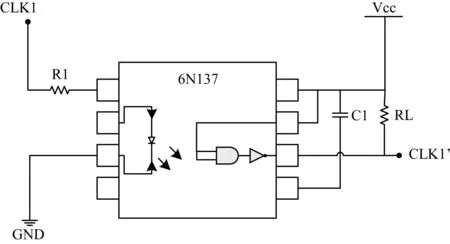

考慮成本和性能,本文使用高速光耦6N137作為信號隔離器[20]。光耦的輸入端連接發光二極管,電信號驅動半導體發光器件發光,而接收端的光敏管將接收到的光信號轉換為電信號輸出。6N137具備比普通光耦更快的速度和更強的驅動能力。將光耦元件應用在時鐘同步設備輸出端(如圖1所示解耦電路的輸入端),其電路如圖7所示。其中,CLK1代表輸入端,CLK1’代表輸出端。調整電阻和電容的大小至最佳性能后,完成功耗曲線的采集。

圖7 解耦電路示意圖

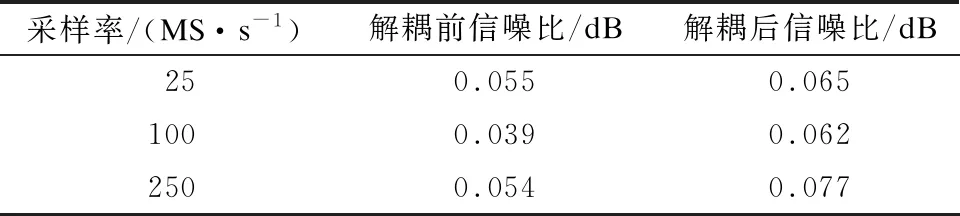

選擇功耗曲線中包含密鑰信息量最大的點,根據式(7),計算功耗曲線解耦前后的信噪比,結果如表3所示。

表3 功耗點信噪比對比

由于待測設備的算法是硬件實現,且芯片內部存在其他電子噪聲,導致信噪比相對較低。經過解耦處理后的功耗曲線,信噪比得到明顯改善。

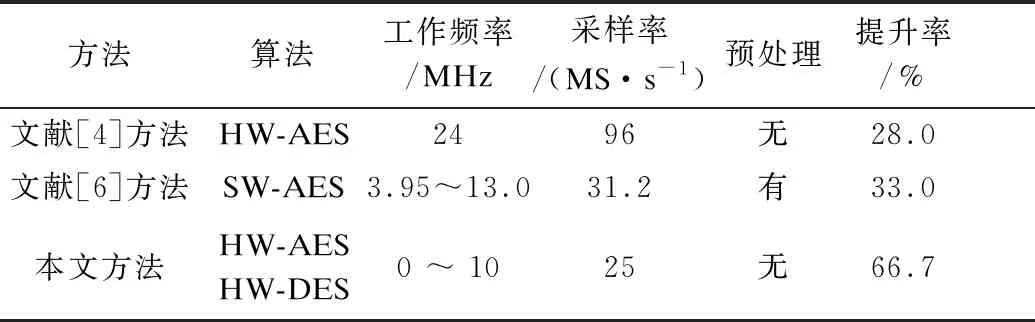

4 性能比較

表4列出了目前相關研究的關鍵指標。待測芯片執行的算法包括軟件實現(SW)和硬件實現(HW)的AES和DES算法等,本文進行了硬件AES算法和硬件DES算法的功耗分析實驗,證明了本文方法的提升效果。

表4 相關方法性能對比

工作頻率是待測芯片執行密碼算法時的工作時鐘頻率。本文的同步采集方法對待測芯片的工作頻率最高為10 MHz(受限于6N137光耦器件的最高信號轉換頻率,性能更優的光耦器件會提升此參數)。

采樣頻率是采集設備的時鐘頻率。文獻[4]采集設備的采樣頻率為96 MS/s時達到了最優;文獻[6]采集設備的采樣頻率為31.2 MS/s時達到了最優;本文在示波器采樣頻率為25 MS/s時達到最優。因此,本文對采集設備的采樣頻率要求最低,降低了對采集設備的成本要求。

預處理包括功耗曲線的再對齊、調整等優化操作。本文無需對功耗曲線進行處理,減少了分析的復雜度。

提升率利用了CPA攻擊的結果,此列數據是各自采集環境下的計算結果(文獻[4,6]未具體給出提升率,但可結合原文圖表近似計算得到提升率)。本文方法的提升率最高達到66.7%。

5 結束語

本文提出一種基于FPGA的時鐘同步功耗信息采集方法。運用該方法設計同步采集平臺,實現了同步功耗信息的采集。通過相關功耗分析進行實驗驗證,結果表明,與AES和DES算法相比,本文同步采集方法功耗分析的成功率有較大提升。本文利用光電解耦原理改善了采集過程中的噪聲問題,使信噪比得到一定提升,為解決功耗信息采集過程中的噪聲問題提供了新思路。本文時鐘同步設備和耦合電路是分離的,下一步通過將其合理整合并制板,以進一步提升采集的信噪比。