基于LT spice 的傳輸線波狀態分析

2020-05-20 06:39:36宋仕澤孫椿凱呂顯學

數字通信世界 2020年4期

任 聰,宋仕澤,朱 杰,孫椿凱,呂顯學

(山東科技大學,濟南 250031)

1 理論概述

傳輸線是一種用以引導電磁波,最大效率的將電磁能或電磁信號從一點定向地傳輸到另一點的電磁器件,廣泛應用于通信系統中。一般情況下,傳輸線的長度大于波長長度,需要考慮電磁波沿線傳播所需的時間和滯后效應,故通過采用多個集總電路級聯的方式來模擬傳輸線[1]。

集總電路是一種由電阻、電感、電容等元件組成的理想化電路模型。集總元件是指元件大小遠小于電路工作頻率相對之波長時,對所有元件之統稱。對于信號而言,不論任何時刻,元件特性始終保持固定,與頻率無關[2]。

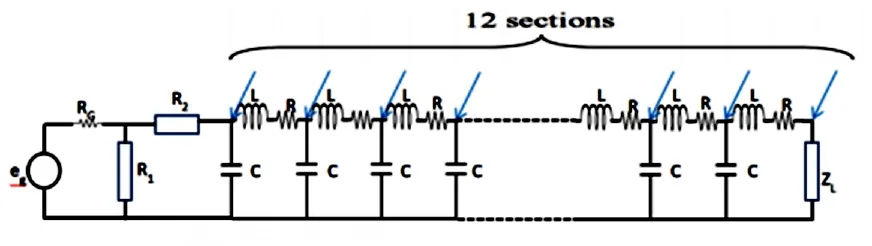

本文采用由12個具有相同集總參數的L-C 電路組成的模擬傳輸線進行實驗。在LTspice 中構建傳輸線仿真電路(εr=2.25,l=5368m),如圖1。

圖1 仿真原理圖

2 仿真測試

2.1 實現傳輸線特征阻抗匹配

2.2 不同終端負載情況下的狀態分析

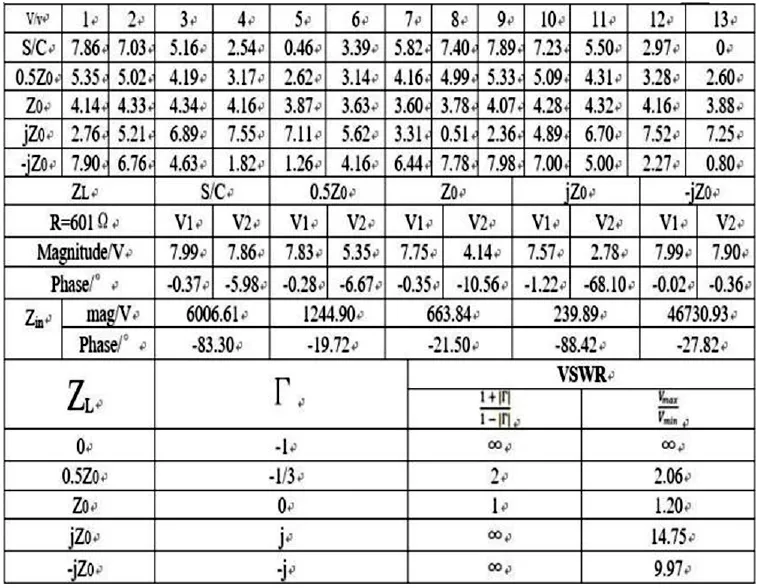

使用差分法(同3.1)計算Zin,設置不同的負載阻抗(電抗)ZL,通過差分法計算Zin,在不同ZL值下測得的V1、V2及計算得出的Zin(見表1)。

表1 數據結果匯總表

通過比較可以看出ZL=0、ZL=0.5Z0和ZL=Z0的情況下,VSWR 的實際值與理論值誤差很小,符合我們的預期。在ZL=jZ0和ZL=-jZ0也就是負載為電抗的情況下,理論值與仿真結果有較大差距。

結論:當負載匹配時,電壓駐波比VSWR=0,則狀態為行波;當終端開路、短路或有電抗存在時,電壓駐波比VSWR ∞,則狀態為駐波;當1 在傳輸線保持低損耗的條件下,可以采用多個集總電路級聯的方式來模擬傳輸線,通過LTspice 軟件仿真,驗證了特征阻抗的值。進行不同終端負載情況下的狀態分析,系統的說明了傳輸線源端阻抗和終端負載阻抗對電磁波狀態的影響。3 結束語