基于SPI接口的1394總線配置表加載設計與實現

魏艷艷 袁曉軍 蔡葉芳 牛少平

摘? ?要:為了滿足飛管系統對1394總線配置表存儲器存儲容量大、讀取速度快、封裝小、功耗低等要求,文章提出了采用SPI串行Flash存儲1394總線配置表。在對SPI協議和SPI串行Flash充分研究的基礎上進行了1394總線配置表加載的系統設計、關鍵功能分析設計和RTL設計實現,最后通過虛擬仿真驗證、FPGA原型驗證及后仿真驗證,結果表明該設計各項功能正確,性能滿足系統要求。

關鍵詞:串行外設接口;1394;配置表;循環冗余

軍用1394總線能夠滿足航空航天等高安全領域對總線高可靠、低延遲、確定性的需求,目前已經成功應用于航電和飛管系統中。楊峰等[1]、王宣明等[2]、馬寧等[3]對1394總線協議、AS5643協議進行了研究并突破了關鍵技術,還進行了機上產品的研發。飛管系統1394總線網絡中控制計算機(Control Computer,CC)節點和遠程節點(Remote Node,RN)的通信都是基于1394總線配置表進行消息收發調度控制的,因此1394總線配置表的定義、管理、維護和存儲在飛管系統網絡通信中起著至關重要的作用。

中航工業西安航空計算技術研究所正在進行RN芯片的研制,1394總線配置表加載設計是其中一部分,為滿足1394總線配置表存儲器的存儲容量大、讀取速度快、封裝小、功耗低等要求,設計上提出采用串行外設接口(Serial Peripheral Interface,SPI)串行Flash進行1394總線配置表的存儲,并在充分研究SPI協議和SPI串行Flash手冊的基礎上進行了1394總線配置表的加載設計實現。

1? ? 系統設計

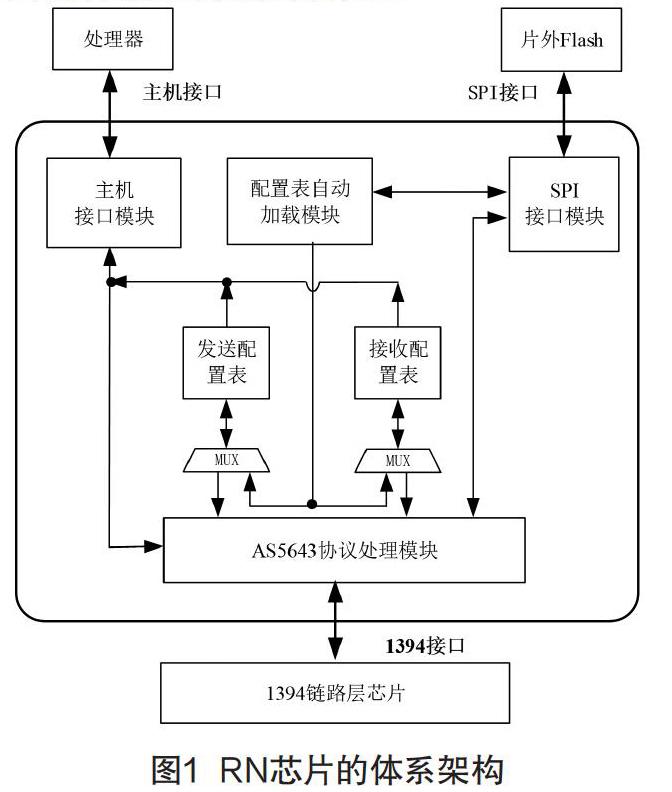

1394總線網絡中RN芯片主要實現了AS5643協議處理功能以及與主機接口、與鏈路層芯片接口、與SPI接口通信等功能。RN芯片的體系架構如圖1所示。

SPI接口模塊主要實現了主機接口與SPI接口的時序轉換及SPI控制器功能。SPI控制器支持主設備,支持4種傳輸模式,時鐘頻率可編程,最大傳輸數據位128 bit。

配置表自動加載模塊主要實現芯片一上電通過SPI接口自動從片外Flash中讀取配置表內容,然后加載到寄存器以及發送配置表和接收配置表中,并支持對配置表內容進行循環冗余(Cyclic Redundancy Check,CRC)校驗功能。

AS5643協議處理模塊主要實現AS5643協議規定的RN協議處理功能以及主機軟件在獲得訪問片外Flash的權限下通過SPI接口對片外Flash進行讀寫功能。

主機接口模塊主要實現處理器對芯片內部寄存器、存儲器資源的訪問。

發送配置表和接收配置表分別用于存儲發送消息、接收消息的配置信息,大小為32×32 bit,支持主機讀訪問和邏輯讀寫訪問。

2? ? 關鍵功能設計

2.1? 配置表內容

系統出于可生產以及可維護性考慮,將網絡中所有RN的配置信息都保存在一個配置表中,上電時給RN一個可唯一識別的設備號,芯片根據該設備號選擇對應的配置表進行加載。配置表包含配置表頭和配置表兩部分,配置表頭規定了配置表版本號、STOF周期、STOF門限、1394總線傳輸速度、消息偏移等,配置表規定了每個設備的消息數目,每條消息的配置信息等。

2.2? 自動加載

配置表自動加載具體操作如下:首先,芯片上電后通過SPI接口進行SPI初始化配置。芯片作為主設備,應該與從設備片外Flash的配置相符才可以通信。其次,加載配置表頭,將配置表頭的信息存入相應的寄存器中。最后,加載配置表,將消息的配置信息分別存入發送配置表和接收配置表中,其他配置表信息存入寄存器中。

2.3? 在線加載

設計上支持主機通過SPI接口對片外Flash進行在線加載配置表,這樣便于機上產品設備配置表的更新和維護,而不用拆卸設備。

主機在線加載配置表的過程中,芯片保持在原工作模式,新的配置表內容在芯片復位后才會起作用。主機必須獲得訪問片外Flash的權限,才可以讀寫片外Flash,從而實現在線加載功能。

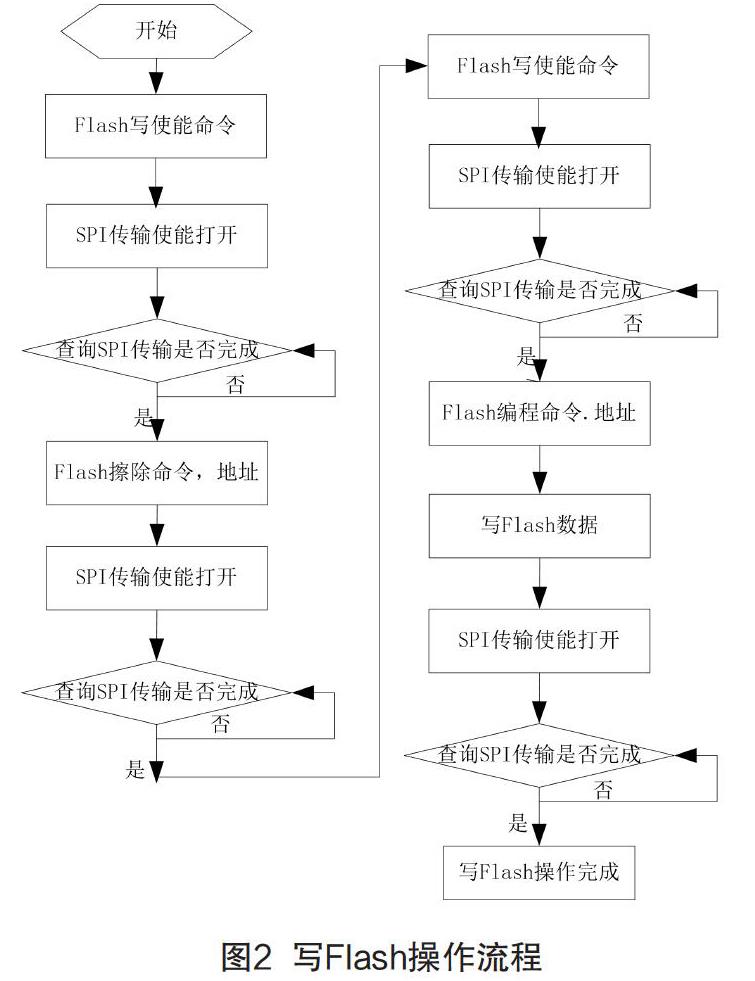

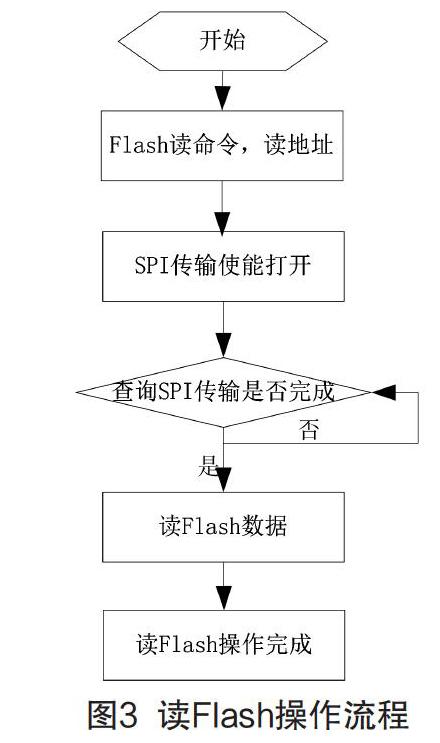

在線加載任務主要包括:通過操作SPI寄存器,進行讀Flash操作、寫Flash操作,將總線配置表數據存儲在片外Flash芯片中。寫Flash操作首先要對Flash進行擦除操作(包含輸入寫使能命令、擦除命令),才能進行寫操作(包含輸入寫使能命令、編程命令、寫Flash數據),如圖2所示。讀Flash操作,輸入讀指令和讀地址后,數據即從Flash中輸出,如圖3所示。

2.4? CRC校驗

配置表數據的正確性影響著1394總線網絡節點通信的可靠性和安全性,因此必須在設計中增加校驗功能,檢測配置表數據是否發生錯誤。由于CRC能同時檢測和抗干擾,是一種高效、可靠的差錯校驗法[4],故該設計對配置表進行了CRC校驗。

CRC校驗算法的多項式為X16+X15+X2+1。從Flash讀數據的同時,CRC校驗也同時進行。配置表連續加載3次,若3次CRC都校驗錯誤,則芯片不能收發消息。

3? ? 仿真驗證

文章采用Verilog硬件語言硬件描述語言(Hardware Description Language,HDL)實現了寄存器轉換級電路(Register Transfer Level,RTL)設計,并搭建虛擬仿真平臺編寫測試用例進行功能驗證,使用Xilinx XC5VLX330T進行現場可編程門陣列(Field-Programmable Gate Array,FPGA)綜合生成可編程文件,外接MPC8245處理器,模擬主機運行測試程序在FPGA原型驗證平臺上進行功能驗證。最后采用CMOS 0.13 μm工藝進行專用集成電路(Application Specific Integrated Circuit,ASIC)綜合,將生成的門級網表加入SDF文件后進行后仿真驗證。

4? ? 結語

文章基于系統要求提出了采用SPI串行Flash存儲1394總線配置表,并進行了系統設計,對關鍵功能進行了分析,通過虛擬平臺驗證,FPGA原型驗證和后仿真驗證,該設計各項功能都正確,性能也滿足系統要求。該設計已經應用在RN芯片研制中,現已成功流片,下一步工作主要是樣片驗證和系統應用測試。

[參考文獻]

[1]楊峰,陳偉,王宣明,等.1394總線關鍵協議分析與研究[J].電子技術與應用,2016(6):7-10.

[2]王宣明,田澤,魏艷艷,等.SAE AS5643協議分析及設計實現[J].計算機技術與發展,2015(7):213-216.

[3]馬寧,王宣明,鄭斐.飛機管理系統1394 總線AS5643協議的設計與實現[J].航空計算技術,2013(6):122-124.

[4]強小燕,史興強,劉夢影.CRC校驗在SPI接口設計中的實現[J].電子與封裝,2018(11):30-35.

Design and implementation of 1394 bus configuration table loading based on the SPI interface

Wei Yanyan, Yuan Xiaojun, Cai Yefang, Niu Shaoping

(Xian Aeronautics Computing Technique Research Institute, AVIC, Xian 710068, China)

Abstract:In order to meet the requirements of flight control system on 1394 bus configuration table memory, such as large storage capacity, fast reading speed, small package and low power consumption, SPI serial Flash was proposed to store 1394 bus configuration table in this paper. On the basis of full research on the SPI protocol and SPI serial Flash, the system design, the key function analysis and design and the RTL design of the 1394 bus configuration table loading were carried out. Finally, though the virtual simulation verification, the FPGA prototype verification and the post simulation verification, the results showed that the design was correct in various functions and the performance met the requirements of the system.

Key words:serial peripheral interface; 1394; configuration table; cyclic redundancy check