基于DDS 信號(hào)生成原理的壓電驅(qū)動(dòng)裝置電源設(shè)計(jì)*

韓 碩,賈丹平,張 濤,王海燕

(1.沈陽工業(yè)大學(xué)信息科學(xué)與工程學(xué)院,遼寧 沈陽 110870;2.中國(guó)科學(xué)院網(wǎng)絡(luò)化控制系統(tǒng)重點(diǎn)實(shí)驗(yàn)室,遼寧 沈陽 110016;3.大連理工大學(xué)電氣工程學(xué)院,遼寧 大連 116024;4.沈陽白云機(jī)械有限公司,遼寧 沈陽 110000;5.中國(guó)科學(xué)院沈陽自動(dòng)化研究所,遼寧 沈陽 110016;6.中國(guó)科學(xué)院機(jī)器人與智能制造創(chuàng)新研究院,遼寧 沈陽 110169)

0 引 言

壓電驅(qū)動(dòng)裝置是一種由新型智能材料壓電陶瓷元件[1-2]制成的高精度運(yùn)動(dòng)電機(jī)設(shè)備[3-4],它具有體積小、推力大、噪聲小和發(fā)熱率低等特點(diǎn),被廣泛應(yīng)用在微電子測(cè)量、光學(xué)儀器和納米技術(shù)等領(lǐng)域[5]。依據(jù)電路原理分類可知,壓電陶瓷元件屬于一種容性負(fù)載。在理想的條件下,壓電陶瓷元件伸縮長(zhǎng)度跟輸入兩端的電壓成線性關(guān)系,響應(yīng)速度跟信號(hào)的輸入頻率有關(guān)。本文綜合大量的理論研究,設(shè)計(jì)了一種驅(qū)動(dòng)該負(fù)載的電源。

傳統(tǒng)頻率合成技術(shù)是依靠振蕩器產(chǎn)生單一頻率信號(hào),只能在很小范圍內(nèi)可微調(diào)而無法滿足頻率源的穩(wěn)定度和精確度的要求。基于DDS 原理生成的信號(hào)具有極高的輸出分辨率。當(dāng)頻率發(fā)生改變時(shí)相位連續(xù)、相位噪聲低、集成度高以及可靈活產(chǎn)生多種信號(hào)等。與傳統(tǒng)頻率合成技術(shù)相比具有無法可比擬的優(yōu)點(diǎn)[6]。現(xiàn)已經(jīng)被廣泛的應(yīng)用到通訊、航天、軍事、現(xiàn)代儀器儀表檢測(cè)以及生物醫(yī)學(xué)檢測(cè)等領(lǐng)域。本文將該理論應(yīng)用到壓電陶瓷元件驅(qū)動(dòng)領(lǐng)域,在大電壓±250V 下產(chǎn)生了頻率高達(dá)1.5KHz 任意信號(hào),保證了在65nf 容性負(fù)載下的壓電驅(qū)動(dòng)裝置波形不失真。實(shí)現(xiàn)了壓電驅(qū)動(dòng)裝置大量程和高響應(yīng)運(yùn)動(dòng)的功能。且通過搭建實(shí)驗(yàn)的方式驗(yàn)證了采用DDS 信號(hào)生成原理的驅(qū)動(dòng)電源的有效性和實(shí)用性。

1 DDS 信號(hào)生成原理

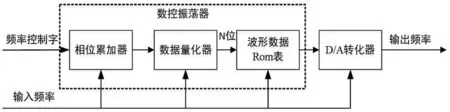

DDS 信號(hào)產(chǎn)生的理論基礎(chǔ)是“奈奎斯特采樣定理”[7]。在定理中可知當(dāng)抽樣頻率大于等于模擬信號(hào)最高頻率兩倍時(shí),就可以從離散序列無失真的信號(hào)中恢復(fù)出原始模擬信號(hào)。DDS 信號(hào)生成原理是對(duì)模擬信號(hào)進(jìn)行抽樣。當(dāng)一個(gè)抽樣過程已經(jīng)發(fā)生且抽樣值已經(jīng)量化完成,從量化數(shù)值重建原始模擬信號(hào)。基本的 DDS 結(jié)構(gòu)主要由相位累加器、波形量化數(shù)據(jù)存儲(chǔ)器、D/A 轉(zhuǎn)換器組成。其中相位累加器和波形量化數(shù)據(jù)存儲(chǔ)器稱為數(shù)控振蕩器,是 DDS 結(jié)構(gòu)中的數(shù)字部分。DDS 基本結(jié)構(gòu)原理如圖1 所示。

圖1 DDS 基本結(jié)構(gòu)原理

其中圖中的輸入頻率為基準(zhǔn)時(shí)鐘頻率,即fc。頻率控制字為K。數(shù)據(jù)量化后的數(shù)據(jù)地址位數(shù)為N位,也是ROM 數(shù)據(jù)線位數(shù)。輸出頻率為fo。則輸出信號(hào)頻率與基準(zhǔn)時(shí)鐘頻率之間的關(guān)系如下:

由式(1)可知,DDS 信號(hào)的最小分辨為:

結(jié)合式(1)和(2)可知,當(dāng)改變輸入的頻率控制字就會(huì)改變DDS 合成輸出的頻率,但不能改變輸出信號(hào)的最小分辨率。

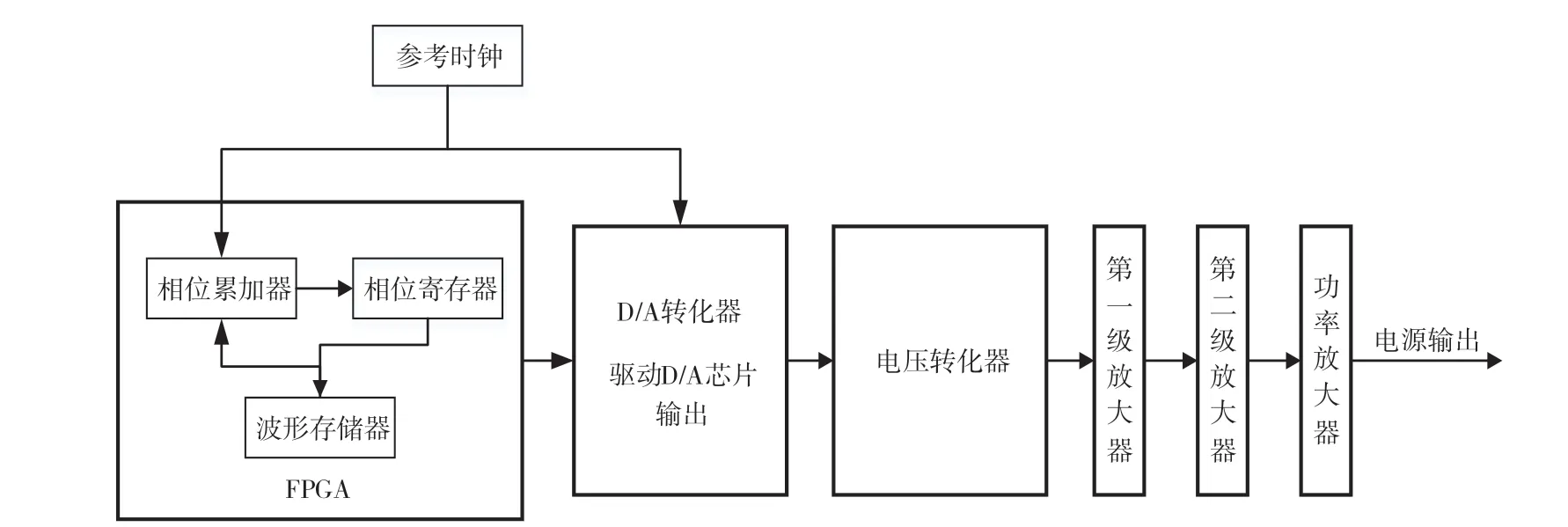

DDS 信號(hào)發(fā)生器的數(shù)控振蕩器部分主要是在FPGA 中實(shí)現(xiàn)的,也是DDS 信號(hào)產(chǎn)生的核心部分。本文中的驅(qū)動(dòng)信號(hào)電源是基于DDS 信號(hào)產(chǎn)生原理設(shè)計(jì)的,其中基本的驅(qū)動(dòng)電源設(shè)計(jì)流程結(jié)構(gòu)圖如下圖2 所示。

DDS 信號(hào)發(fā)生部分是在FPGA 硬核中實(shí)現(xiàn)的。其中包括ROM IP 核、相位累加器和相位寄存器。D/A 轉(zhuǎn)化器主要是采用FPGA 驅(qū)動(dòng)PCM1702 構(gòu)建的DDS 信號(hào)發(fā)生電路組成。其中PCM1702 是20 位高分辨率的信號(hào)輸出芯片。ROM IP 核中量化的數(shù)據(jù)點(diǎn)越多,離散信號(hào)的線性度越好,信號(hào)輸出的質(zhì)量越高。但是數(shù)據(jù)點(diǎn)的多少受控于ROM 的數(shù)據(jù)線位數(shù)。本設(shè)計(jì)采用N=20,參考時(shí)鐘fc=50 MHz,輸出信頻率為1.5 KHz,D/A 轉(zhuǎn)化器輸出電流信號(hào)為±1.2 mA。產(chǎn)生壓電驅(qū)動(dòng)裝置所需要的驅(qū)動(dòng)信號(hào)梯形波。

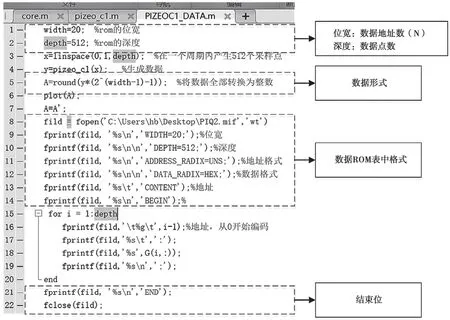

原Altera 公司的Quartus16.0 開發(fā)軟件中提供了現(xiàn)成的ROM IP 核,其中需要加載(.mif 文件)文件中的數(shù)據(jù)應(yīng)用到IP 核中,波形存儲(chǔ)器初始化數(shù)據(jù)形式后,對(duì)數(shù)據(jù)進(jìn)行整數(shù)化處理,以滿足所輸出的信號(hào)數(shù)據(jù)要求。.mif 文件中數(shù)據(jù)內(nèi)容格式是使用MATLAB 工具生成所需要的信號(hào)數(shù)據(jù),然后主控核心板FPGA 調(diào)用ROM 核填充文件的數(shù)據(jù)點(diǎn)。.mif 文件內(nèi)容格式解析如下圖3 所示。

圖2 驅(qū)動(dòng)電源設(shè)計(jì)流程結(jié)構(gòu)

圖3 .mif 文件內(nèi)容格式解析

通過查表地址的方式,F(xiàn)PGA 實(shí)現(xiàn)了對(duì)于ROM IP 核中的數(shù)據(jù)調(diào)用。ROM 表尺寸與數(shù)據(jù)位數(shù)成2N指數(shù)增長(zhǎng)關(guān)系,采用縮減查表地址和壓縮ROM 表尺寸的方法可節(jié)省資源[8]。D/A 發(fā)生器應(yīng)用Verilog語言程序驅(qū)動(dòng)D/A 芯片生成所需的模擬電流信號(hào),即將量化后的數(shù)據(jù)還原成波形輸出。電流信號(hào)生成的參考時(shí)鐘是50MHz,產(chǎn)生頻率為1.5KHz。

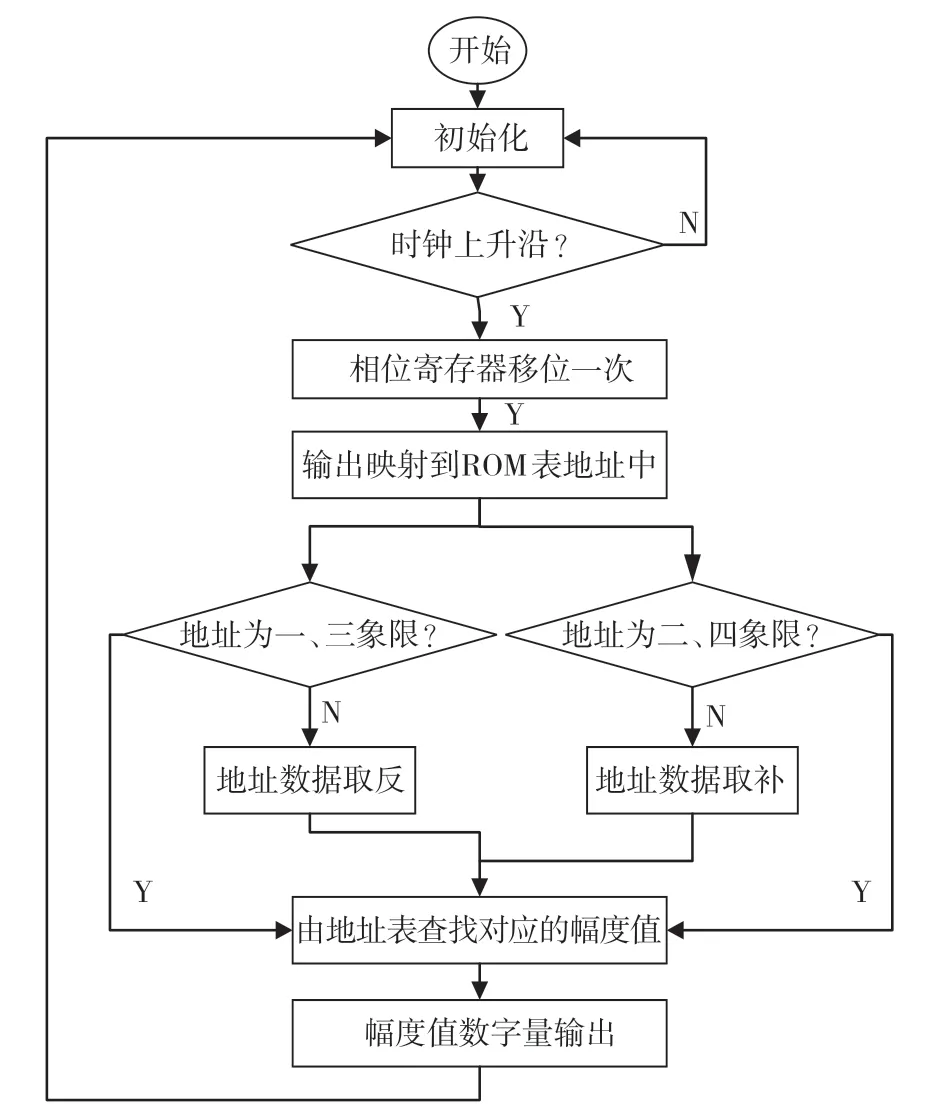

以生成的梯形波為例,基于Verilog 語言的ROM IP 核數(shù)據(jù)輸出的DDS 軟件流程圖如下圖4 所示。

ROM IP 核完成1/4 梯形函數(shù)的數(shù)據(jù)存儲(chǔ)后,需要設(shè)計(jì)地址擴(kuò)展來生成其余3/4 的波形數(shù)據(jù)。正如圖4 所示,當(dāng)系統(tǒng)復(fù)位完成后,一旦檢測(cè)到時(shí)鐘上升沿,相位寄存器移位一步,累加器就累加一個(gè)步長(zhǎng),得到的相位數(shù)據(jù)值映射到地址查表中。第一、三象限地址取反,第二、四象限地址取補(bǔ)。其中數(shù)據(jù)寬度為20 位,以524,287 為中心分別輸出正負(fù)半軸的波形量化幅度值數(shù)字量。

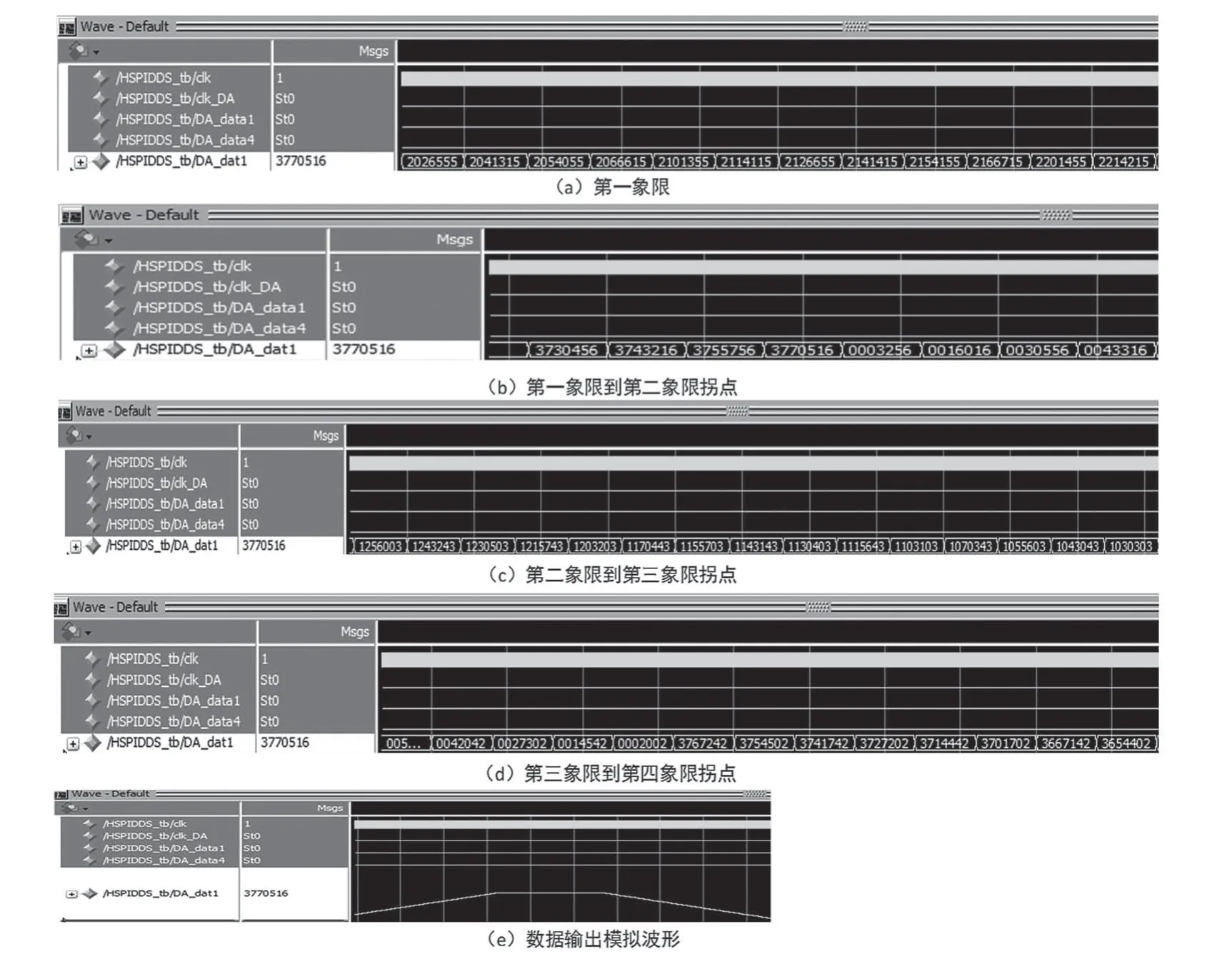

應(yīng)用Quartus16.0 軟件進(jìn)行功能仿真得到的波形數(shù)字量如圖5所示。其中clk為輸入的參考時(shí)鐘(晶振時(shí)鐘),DA_dat1 為輸出信號(hào)。改變相位增量可調(diào)節(jié)輸出信號(hào)的頻率,改變波形存儲(chǔ)表內(nèi)容可得到任意波形,仿真圖中頻率控制確定。由(1)式可知頻率控制字可改變DDS 信號(hào)頻率,在程序設(shè)計(jì)的過程中通常使頻率控制字作為輸入變量[9-11],進(jìn)而實(shí)現(xiàn)了不同頻率DDS 信號(hào)輸出。

圖4 DDS 軟件流程

圖5 中(a)、(b)、(c)、(d)圖是以十進(jìn)制無符號(hào)的形式展現(xiàn)。隨著上升沿信號(hào)的觸發(fā)使得ROM IP 核中數(shù)據(jù)開始輸出。各個(gè)圖中的數(shù)據(jù)量化點(diǎn)代表各個(gè)象限的數(shù)據(jù)離散點(diǎn)。(e)連續(xù)信號(hào),是由各個(gè)離散點(diǎn)線性化組成的模擬信號(hào)。

2 驅(qū)動(dòng)電路硬件設(shè)計(jì)

2.1 D/A 轉(zhuǎn)化器設(shè)計(jì)

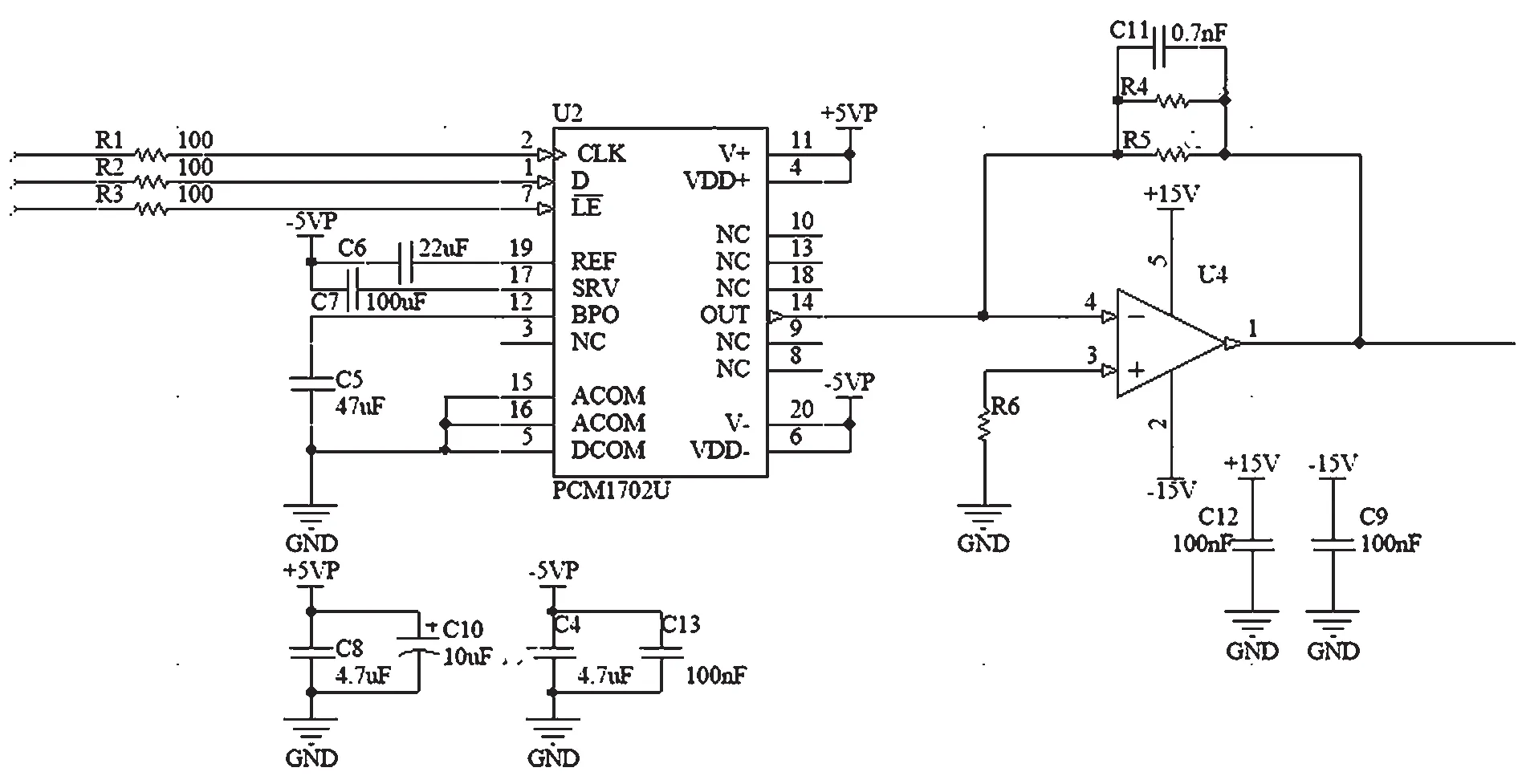

由查找表中讀出的數(shù)字量幅度值是一串?dāng)?shù)字序列,最終要經(jīng)過 D/A 轉(zhuǎn)換器才能轉(zhuǎn)換成相應(yīng)的模擬波形輸出。為了解決數(shù)據(jù)處理的準(zhǔn)確性和模擬波形信號(hào)的質(zhì)量問題,D/A 轉(zhuǎn)換器必須有足夠的轉(zhuǎn)換精度。為了考慮 D/A 轉(zhuǎn)換器的非線性和噪聲特性,綜合了各方面的因素之后,本文設(shè)計(jì)采用 PCM1702為波形發(fā)生主芯片。PCM1702 是一種高速處理芯片,其中信號(hào)以電流的形式輸出。輸出電流幅度值為±1.2mA。D/A 轉(zhuǎn)換器硬件電路設(shè)計(jì)如圖6 所示。

D/A 波形產(chǎn)生電路早期應(yīng)用在音頻放大電路中,具有響應(yīng)時(shí)間快、低噪聲干擾以及輸出精度高等特點(diǎn)。為了實(shí)現(xiàn)信號(hào)的降噪和濾波作用,在電流信號(hào)經(jīng)過電壓轉(zhuǎn)化器后,采用前級(jí)放大芯片OPA137 作為反向電壓跟隨器,構(gòu)成的跟隨電路具有濾波和降噪的功能。信號(hào)放大到±10V 輸出。

圖5 波形仿真數(shù)字量圖

2.2 功率放大電路

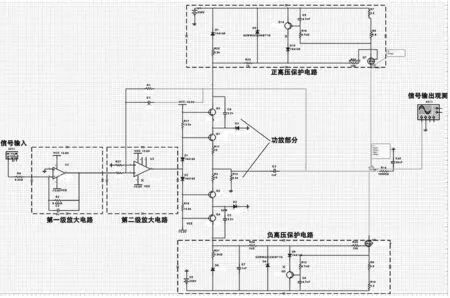

利用LM356 放大芯片進(jìn)行了第二次反向放大,從而完成了整個(gè)前端信號(hào)發(fā)生電路的設(shè)計(jì)。為了驅(qū)動(dòng)對(duì)象運(yùn)行,需要對(duì)驅(qū)動(dòng)信號(hào)進(jìn)行功率放大。在本文中設(shè)計(jì)了一種高電壓,小電流的功放模塊。該放大模塊是應(yīng)用三極管的放大原理設(shè)計(jì)的,其中原因有兩點(diǎn),其一是信號(hào)頻率較大,其二是信號(hào)的電壓大電流小。且搭建了高電壓信號(hào)保護(hù)電路。使用仿真軟件Multisim14.0 對(duì)電路進(jìn)行仿真和各個(gè)電壓檢測(cè)點(diǎn)進(jìn)行觀測(cè)。如圖7 所示。

圖6 硬件電路設(shè)計(jì)

圖7 Multisim14.0 仿真電路

功放部分電路圖由第一級(jí)放大開始,最后輸出±250V 的電壓信號(hào)。由于信號(hào)的頻率較高,電路設(shè)計(jì)采用甲乙類三極管放大設(shè)計(jì)。為了滿足整個(gè)實(shí)驗(yàn)的高電壓輸出的需求,采用高電壓MOS 管對(duì)電壓信號(hào)進(jìn)行放大從而得到高電壓任意波形信號(hào)。其中整個(gè)系統(tǒng)的增益放大倍數(shù)如下式(3)所示:

其中Gf為功放系統(tǒng)的增益放大倍數(shù)。Rf為放大增益電阻對(duì)應(yīng)仿真圖中的R1阻值。Ri為信號(hào)輸入電阻對(duì)應(yīng)仿真圖中的R27阻值。在一定條件下,由電路仿真與設(shè)計(jì)可知Rf與Ri電阻比決定了功放部分電路中的放大倍數(shù)。本文按照實(shí)際要求放大到27 倍左右。

3 系統(tǒng)實(shí)驗(yàn)與信號(hào)分析

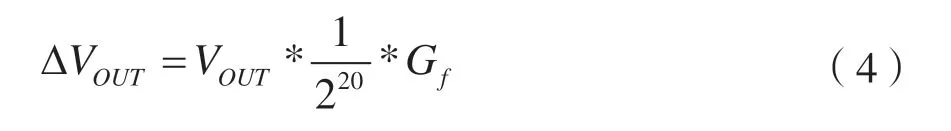

本文為了滿足輸出壓電驅(qū)動(dòng)裝置運(yùn)動(dòng)的電源信號(hào)。頻率控制字K 為固定的值,則相位增量就會(huì)相同,輸出頻率不變,當(dāng)相位累加器的字長(zhǎng)N 取32位時(shí),將ROM 地址線位數(shù)定最高20 位。當(dāng)設(shè)計(jì)中采用50 MHz 晶振,無倍頻的情況下,頻率分辨率達(dá)到0.012 Hz。由此如下式(4)得到的輸出幅度分辨率為:

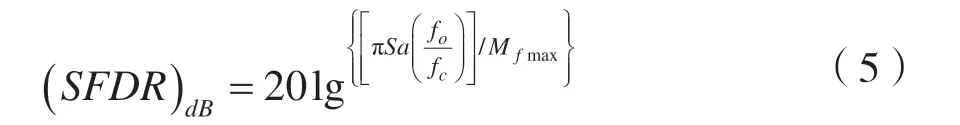

其中ΔVOUT幅度最小分辨率,VOUT數(shù)字量化電壓,Gf為功放系統(tǒng)的增益放大倍數(shù)(與式3 中等意義)。為了驗(yàn)證應(yīng)用DDS 原理信號(hào)質(zhì)量問題,由相位截?cái)嗾`差引入的DDS 無雜散動(dòng)態(tài)范圍SFDR 為[12-14]:

其中為了滿足功放模塊的性能指標(biāo)。綜合壓電裝置的動(dòng)態(tài)響應(yīng)和實(shí)際狀況,得到輸出頻率為fo=1.5 KHz。由綜合式(5)可以近似得到DDS 無雜散動(dòng)態(tài)范圍SFDR 為[15]:

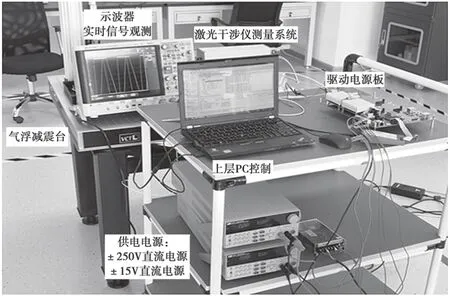

其中本文取N 和B 取值分別為32、20。可知DDS 無雜散動(dòng)態(tài)大于等于72.24 dB,滿足信號(hào)輸出質(zhì)量要求。為了驗(yàn)證基于DDS 原理設(shè)計(jì)的壓電驅(qū)動(dòng)裝置電源能夠達(dá)到壓電驅(qū)動(dòng)裝置正常運(yùn)行的目的。建立如下圖8 所示的系統(tǒng)實(shí)驗(yàn)平臺(tái)。

圖8 系統(tǒng)實(shí)驗(yàn)平臺(tái)

該實(shí)驗(yàn)平臺(tái)主要由電源部分、驅(qū)動(dòng)器和檢測(cè)系統(tǒng)組成。電源采用±250 V 線性可編程電源和±15 V開關(guān)電源分別供電功率放大模塊以及運(yùn)放供電部分。驅(qū)動(dòng)器由多核處理器、FPGA 和DDS 信號(hào)發(fā)生器組成。由上層的PC 控制驅(qū)動(dòng)信號(hào)輸出和觀測(cè)運(yùn)動(dòng)實(shí)際軌跡曲線,其中輸出驅(qū)動(dòng)信號(hào)由示波器進(jìn)行觀測(cè),示波器型號(hào)為KEYSIGHT。應(yīng)用激光干涉儀作為位移測(cè)量系統(tǒng)。為了驗(yàn)證該電源的信號(hào)質(zhì)量,應(yīng)用示波器觀察驅(qū)動(dòng)信號(hào)輸出如圖9 所示。

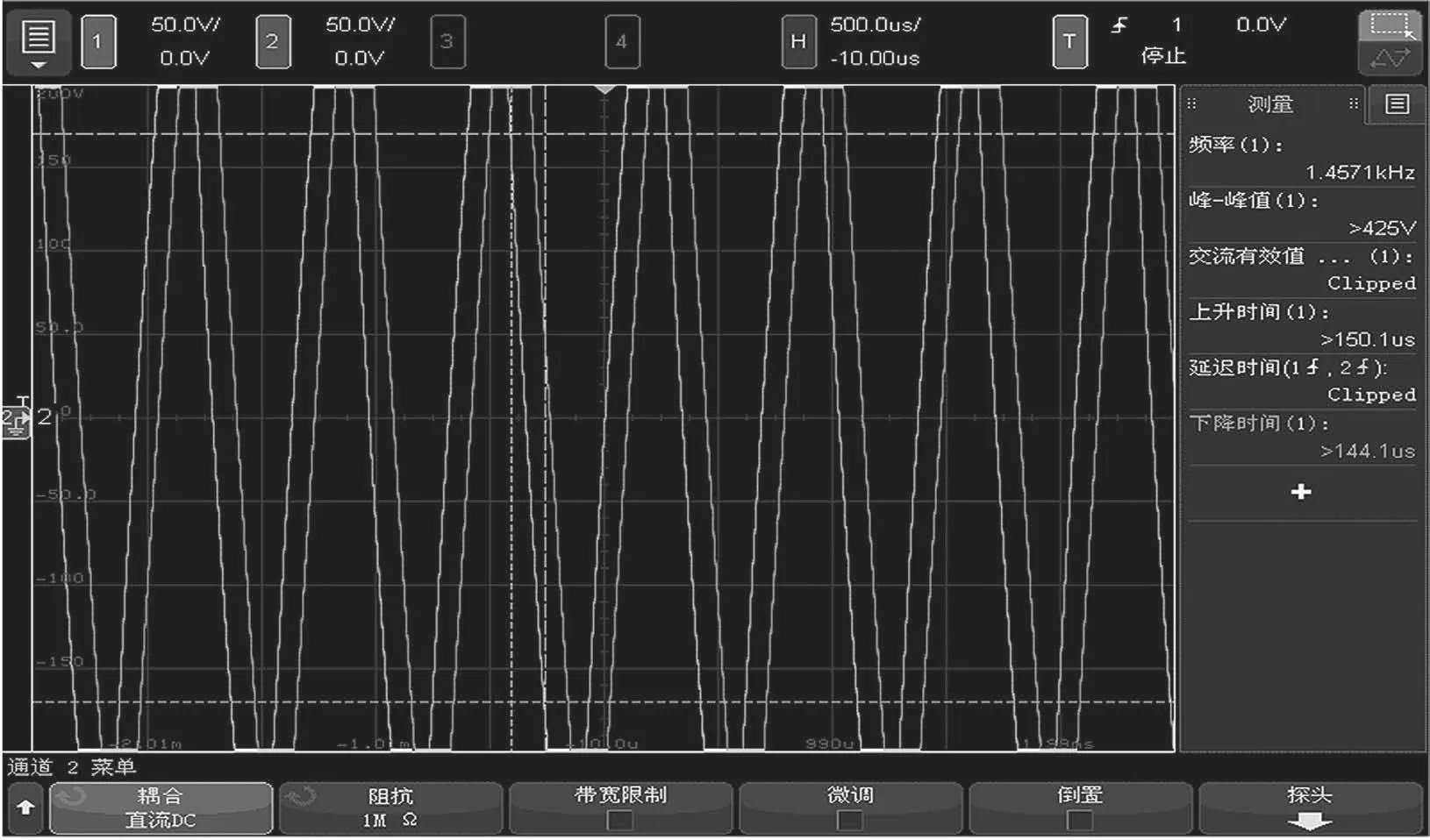

圖9 DDS 信號(hào)梯形波

依據(jù)圖9 示波器觀測(cè)到的梯形波信號(hào),實(shí)際測(cè)量輸出頻率為1.4571 KHz,其中頻率精度誤差為0.98%左右。在±250 V 電壓輸入的情況下,實(shí)際測(cè)量的電壓輸出峰峰值為495.5 V。其中輸出電壓精度誤差為0.9%。因此證明了DDS 信號(hào)生成原理的驅(qū)動(dòng)電源是具有可行性的,所帶來的誤差可能是信號(hào)線纜引起的。

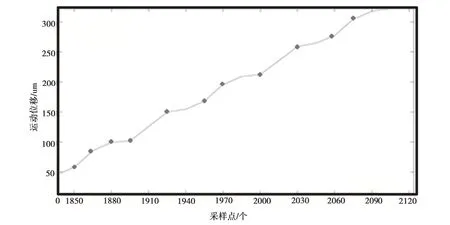

應(yīng)用激光干涉儀測(cè)得壓電驅(qū)動(dòng)裝置的運(yùn)動(dòng)軌跡圖如圖下10 所示。其中檢測(cè)裝置采用的是高精度4 Khz采樣率的激光干涉儀設(shè)備對(duì)運(yùn)動(dòng)步長(zhǎng)進(jìn)行位移采集。

圖10 壓電驅(qū)動(dòng)裝置運(yùn)動(dòng)軌跡

由圖10 可知應(yīng)用DDS 原理設(shè)計(jì)的信號(hào)驅(qū)動(dòng)電源驅(qū)動(dòng)了壓電驅(qū)動(dòng)裝置運(yùn)動(dòng),應(yīng)用本文的方案解決了壓電裝置的運(yùn)動(dòng)問題。

4 結(jié) 語

本文完成了基于DDS 原理設(shè)計(jì)的壓電驅(qū)動(dòng)裝置電源。使用FPGA 實(shí)現(xiàn)了DDS 結(jié)構(gòu)系統(tǒng)的整體過程。通過實(shí)驗(yàn)和理論證明,應(yīng)用本文的方案可以驅(qū)動(dòng)壓電裝置運(yùn)行。實(shí)現(xiàn)了±250 V 信號(hào)輸出,頻率最高可達(dá)1.5 KHz 梯形波信號(hào)。搭建驅(qū)動(dòng)電源測(cè)試平臺(tái)中,證明了信號(hào)輸出的質(zhì)量高和精度高,驗(yàn)證了采用DDS 信號(hào)生成原理的驅(qū)動(dòng)電源的有效性和實(shí)用性。