可編程邏輯器件在數電實驗中的應用研究

車沛強

(閩南科技學院,南安 362332)

0 引言

對于目前的數字電路實驗裝置而言,大部分的數字實驗裝置都是使用的中規模邏輯芯片,而這種邏輯芯片的使用就會導致實驗裝置具有較多的插座,而且插座的規模較多,使實驗變得復雜化,除此之外使用該裝置還會占據大量的空間,使用的引線較長較多,會對實驗的操作造成一定的影響,而且會使得實驗的成本增加,而且該實驗裝置無法適用于復雜、高速的邏輯實驗,在使用以及維修方面都有著不小的困難[1]。而單片機和可編程邏輯器件的使用能夠使得實驗裝置使用的成本下降,從而為研制低成本又功能繁多的數字實驗裝置提供了有利的條件。

1 單片機的特點以及工作原理

所謂的單片機,又可稱為單片微控制器,是一種集成電路芯片,將一個計算機系統集成到一個芯片上,近似于一個微型的計算機,只是缺少了I/O設備[2]。單片機具有體積小、重量輕以及價格便宜等優點,能夠為學習、開發和應用提供良好的便利條件。目前,對于單片機的使用已經十分廣泛,各個領域都有著單片機的應用,比如通信設備、家用電器、智能手表以及導航系統等[3]。

隨著科學技術的不斷發展,人們對于單片機的應用逐漸滲透到各個領域。現如今,人們越來越重視單片機的開發與應用,而電子信息技術與單片機技術的融合更是顯著的提高了單片機的應用效果[4]。作為計算機技術中的一個分支,單片機廣泛的應用于電子產品領域,豐富了電子產品的功能,使智能化電子設備的創新與發展得到了有效的實現。

簡而言之,單片機就是一塊由系統組成的芯片,其通過集成電路技術將數據運算和處理能力集成到芯片之中,從而能夠對數據進行高速化的處理[5]。

作為一種現代化電子信息技術的產物,單片機具有其獨特的特征。單片機具有較小的體積,其內部的芯片雖然是結構簡單的計算機系統,但卻具有完善的功能,能夠十分方便簡潔的進行使用,還能夠進行模塊化的應用。另一方面,單片機具有較高的集成度以及較強的可靠性,即便進行了長時間的工作,單片機也不會發生什么故障。并且在使用的時候,單片機消耗的能量較低,給人們的生產與研發帶來了不小的便利,人們在日常生活中首先會對單片機進行選擇。除此之外,對于數據處理能力以及運算能力,單片機也較強,能夠應用在各種環境之中,而且其控制能力也較為突出。

對于單片機,由于其從內部的硬件到軟件具有一整套按位操作系統,其處理的對象是位而不是字以及字節,這就使得其不但能夠對寄存器的某位進行有效的處理,還可以對位進行邏輯運算,具有十分完備的功能。而片內的RAM區間開辟的雙重功能地址區間還使得使用十分靈活,給使用者提供了不小的便利。除此之外,乘法和除法指令也使得編程變得更加的方便。

CPLD即復雜可編程邏輯器件,是一種用戶根據各自需要而自行構造邏輯功能的數字集成電路。其基本設計方法是借助集成開發軟件平臺,用原理圖、硬件描述語言等方法,生成相應的目標文件,通過下載電纜(“在系統”編程)將代碼傳送到目標芯片中,實現設計的數字系統。

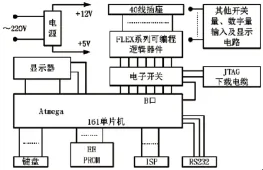

而在數字集成電路實驗當中,AVR單片機負責控制實驗裝置,并且快速對CPLD進行配置,而CPLD器件則是負責實現邏輯功能。

圖1 電路連接圖

單片機會在上電后進行復位自檢,電子開關閉合,接通單片機到CPLD器件的編程線,于顯示器上顯示出等待標志,然后通過掃描鍵盤等待鍵盤輸入所需的邏輯器件編號。鍵入編號后,單片機則是將與器件對應的編程數據編程到CPLD器件中,使得CPLD具備了所選器件的邏輯功能[6]。

其中,對于單片機的選擇,為ATMEL的Atmega161系列。采用哈佛結構的這種單片機中具有1K字節RAM、512字節的串行EEPRPM、一個增強性能的RISC8位CPU以及16K字節的Flash程序儲存器等大量的資源。另外,這種單片機具有較快的運行速度,平均下來,對于一條指令的執行大概在一個時鐘周期,而且在8MHz時鐘下的運行速度能夠達到8MIPS,對于CPLD的配置能夠快速的完成[7]。

按照所設計的邏輯功能將可編程邏輯器件的編程數據排列成表格放在單片機程序的存儲器以及擴展的EEPROM存儲器中,再將單片機讀入鍵盤狀態后根據鍵值對邏輯功能所對應的數據進行尋找,然后傳送到可編程邏輯器件中,就使得對于所選擇的邏輯功能,可編程邏輯器件已經具備,從而能夠進行數字電路實驗。

2 單片機的軟件設計

對于整個實驗裝置而言,單片機軟件是一個十分重要的組成部分。對于單片機設計,根據系統功能的要求是采用了模塊化的結構,其主要構成成分為主程序、通信模塊、CPLD編程模塊以及EEPROM讀寫模塊等[8]。

在主程序之中主要包括打開編程開關、系統參數初始化以及鍵盤掃描顯示驅動等;而對于CPLD編程而言,要根據所選的器件序號,將編程數據寫到CPLD器件中時需要按照CPLD器編程的時序要求,從而對CPLD進行編程,并關閉編程開關。軟件編程則是對單片機的串行同步接口SPI進行了使用,將單片機設置為主機模式,只要在主CPU的SPI數據寄存器中將編程數據的一個字節寫入,就能夠將SPI的時鐘生成器啟動,從而以PB5引腳將數據移出。移出一個字節后,SPI時鐘生成器會停止工作,對停止標志位(SOIF)進行設置后再繼續下一個數據編程,直到編程數據結束標志。對于軟件的編寫,是在Avrstudio環境下進行語言的匯編,這樣可以顯著的提高CPLD的配置速度。對于上位機的通信,通信模塊在完成之后會配合EEPROM讀寫模塊對上位機已經綜合好的配置文件進行下載,并導入到EEPROM當中。

圖2 工作流程

3 可編程邏輯器的選擇

對于可編程邏輯器件(CPLD)的選擇,是選擇ATMEL公司的FLEX系列,因為對于這個系列的可編程邏輯器件的制造,是采用高性能的CMOS技術進行的。通過這個技術,編程數據被存放在RAM中,從而使得重復編程變得高效快速,系統的時鐘可達130 MHz,具有快速的運行速度,對于高速數字電路實驗的要求能夠進行很好的滿足[9]。對于可編程邏輯器件的引腳,按照高速數字電路等長度引線的要求將其引到一個模擬插座上,并對這個模擬插座進行相應的標識,對于實驗所用的數字電路型號的選擇,根據鍵盤進行,然后對對應的標識進行更換,從而能夠有效的模擬74LS系列或者其他的邏輯器件的數字電路實驗。

而獲取可編程邏輯器件的配置數據,首先是要得到配置數據文件,這需要在PD機上使用VHDL語言或者是采用GDF原理圖法按照不同型號的數字集成電路的功能進行邏輯設計編程綜合,通過仿真才能夠實現。之后對于頭尾標志的添加,需要根據可編程器件編程的要求以及該數據文件的結構采用C語言程序轉化為AVR系列單機片所要求的數據格式,然后將其與單片機程序一起編程到單片機。除此之外,為了更好的擴展實驗的個數,將常用期間的編程數據存放在單片機的程序存儲器之中,而在外擴的EEPROM中存放將其他器件編程數據,對于實驗的內容以及數量的更改,只要與上位機通信刷新EEPROM內容就能夠簡單得到實現。

4 實驗功能的擴展

可以利用單片機的ISP編程接口對本文所述的數字電路實驗裝置的單片機的控制功能進行自由的更換,從而使得軟件可編程數字電路實驗裝置得到了真正的實現。除此之外,對于數字邏輯實驗,除了能夠完成74LS系列的之外,本文所述的數字電路實驗裝置還能夠進行可編程邏輯器件實驗以及AVR系列單片機實驗,并且具有價格低廉、靈活高效以及一機多用等優點,大大降低了實驗的成本與難度,充分滿足了高等學校日益發展的教學要求。

5 結束語

對于數字電路實驗,由于傳統的數字電路實驗裝置存在著功能單一、規模較小且接線復雜,因此導致學生的數字電路實驗存在著一定的缺陷,無法滿足日益發展的教學要求。而隨著科學技術的發展,電子信息技術的不斷壯大,單片機的使用對于數字電路實驗的發展有著良好的推動作用。對于數字電路實驗裝置,在其中使用單片機使得數字電路實驗裝置的運行成本得到了降低,而且具有功能多,操作簡單等豐富的優點,為數字電路實驗的進行創造了有利的條件。