高性能小數(shù)分頻鎖相環(huán)的研究與實現(xiàn)?

謝 雷 陳海燕 陳建軍

(國防科技大學計算機學院 長沙 410073)

1 引言

鎖相環(huán)(PLL)技術最早起源于20 世紀30 年代,鎖相環(huán)隨著電子工藝的進步不斷發(fā)展.早期的鎖相環(huán)受限于成本太高,應用范圍僅限于接收機等精密儀器領域[1]。如今,隨著集成電路技術的不斷革新,PLL 作為提供時鐘的重要模塊,為芯片提供基準數(shù)字頻率,被廣泛應用于電子科技、有線和無線通信系統(tǒng)中;在多時鐘和高速數(shù)字系統(tǒng)中,基于PLL 的頻率合成器也起著提供時鐘信號的重要作用。

理論上,整數(shù)型PLL只能產(chǎn)生在頻譜上純凈和單一的N 倍于參考頻率Vref 的輸出頻率。受到頻率分辨率的限制,整數(shù)型PLL應用范圍有限。小數(shù)分頻PLL(Fractional PLL)可以很好地解決整數(shù)型PLL 遇到的諸如分辨率不夠以及切換頻率較慢等問題。

小數(shù)分頻PLL 在保留整數(shù)型PLL 的結構的同時通過動態(tài)的切換反饋分頻器分頻系數(shù),改變整數(shù)型PLL 的輸出來完成小數(shù)功能。但是此方法會引入大量的雜散噪聲,這對于PLL的噪聲性能是非常不利的[2]。

為了有效抑制雜散對PLL性能的影響,進一步提高PLL 的性能。本文提出基于DAC 的噪聲補償技術,并以此為基礎設計了一款高性能、低相噪、高分辨率的小數(shù)分頻PLL。

2 ΔΣ小數(shù)分頻PLL

2.1 傳統(tǒng)小數(shù)分頻PLL的實現(xiàn)及缺點

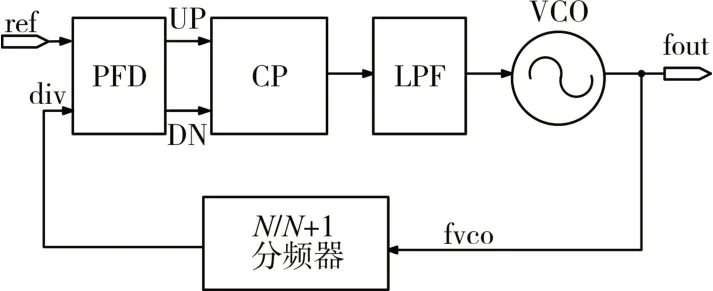

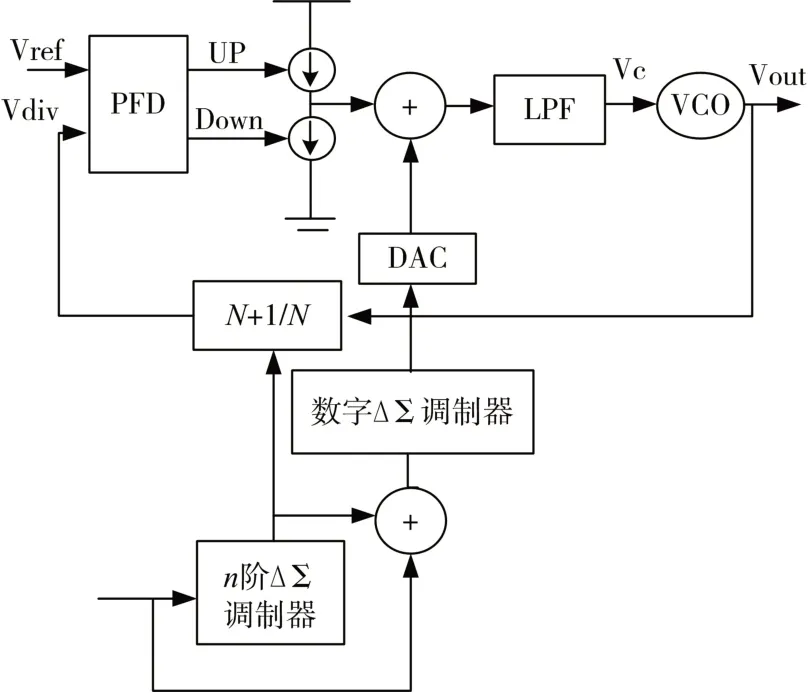

傳統(tǒng)的小數(shù)分頻PLL 通常采用累加器的方式實現(xiàn),圖1 給出了使用累加器的原理圖。小數(shù)a 為累加器的輸入,每個時鐘周期累加器將數(shù)值增加a,當累加數(shù)值不超過1 時累加器輸出為0,這時反饋分頻器進行N 分頻;當累加數(shù)值超過1 時,累加器溢出,輸出為1 并將累加數(shù)值減去1 重新開始累加,此時反饋分頻器進行N+1 分頻。在一定周期后,得到需要的小數(shù)分頻[3]。

利用累加器雖然可以實現(xiàn)小數(shù)分頻,但是會存在瞬時頻差。瞬時頻差會導致鑒相器的兩路信號出現(xiàn)相位差,相鄰的相位差相互積累導致鋸齒狀的相位誤差,形成嚴重的小數(shù)雜散。采用ΔΣ調(diào)制技術可以有效消除小數(shù)雜散。

圖1 傳統(tǒng)小數(shù)PLL結構圖

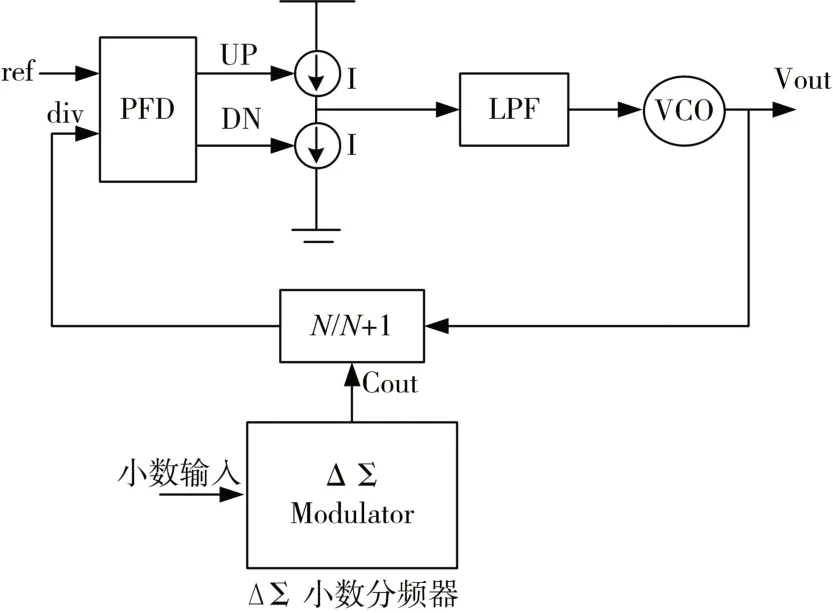

2.2 ΔΣ小數(shù)分頻PLL

基于ΔΣ調(diào)制技術的小數(shù)分頻PLL 是現(xiàn)階段應用最多、效果最好的一種小數(shù)分頻結構[4]。圖2 給出了ΔΣ小數(shù)分頻鎖相結構。它與傳統(tǒng)小數(shù)分頻PLL 主要的區(qū)別是在反饋分頻部分增加了ΔΣ調(diào)制器。小數(shù)值設置字FN 控制ΔΣ調(diào)制器動態(tài)產(chǎn)生輸出控制字Cout,Cout 可以控制反饋分頻器的系數(shù)發(fā)生變化,從而改變PLL的小數(shù)分頻值。

圖2 基于ΔΣ技術的小數(shù)分頻PLL

ΔΣ調(diào)制器的作用是產(chǎn)生瞬時整數(shù)分頻比,但是不同周期產(chǎn)生的整數(shù)分頻比不同,所以平均輸出值為小數(shù)。圖3 顯示了ΔΣ調(diào)制器產(chǎn)生N.a 分頻比的過程。圖中ΔΣ調(diào)制器輸入為0.a,輸出值為0 或1,其平均輸出為0.a。小數(shù)部分的輸出與整數(shù)部分N 相加即可得到瞬時分頻比。瞬時分頻比反饋回分頻器,控制分頻器分頻比值。

圖3 ΔΣ調(diào)制器控制小數(shù)

基于ΔΣ調(diào)制技術的小數(shù)分頻PLL 可以有效抑制噪聲,其原理是利用ΔΣ調(diào)制器對噪聲的整形特性,將小數(shù)分頻產(chǎn)生噪聲整形到高頻段,然后利用PLL 本身的低通特性對輸入噪聲進行有效濾除,改善小數(shù)分頻引起的噪聲[5]。

2.3 ΔΣ小數(shù)分頻PLL的雜散來源

理想情況下,PLL 輸出信號的能量都集中在單一頻點上,但在實際情況中,總會有功率能量分布在載波能量的兩側,這部分能量代表著噪聲。相位噪聲是隨機干擾對載波的調(diào)相引起的,具有隨機性。雜散也是噪聲的一種表現(xiàn)形式,但通常來自于外界周期性的干擾,具有周期性,且雜散在某些頻點有很高的能量[6]。因此能否有效的抑制雜散直接關系到PLL噪聲性能。

小數(shù)分頻PLL 中主要的噪聲源主要分為兩大類:參考雜散和小數(shù)雜散。

小數(shù)雜散是在PLL 的輸出端以輸出頻率為載波,以α倍的參考頻率為倍數(shù)的雜散形式,小數(shù)雜散主要來自于以下兩個方面:

1)交調(diào)分量對VCO 的調(diào)制導致的雜散。由于分頻器存在輸入信號的泄露,導致VCO 輸出頻率經(jīng)過反饋分頻器后部分泄露至PFD。泄露到PFD的頻率與參考頻率的n 次諧波混頻,產(chǎn)生對應的交調(diào)分量,其中小于PLL的環(huán)路帶寬的部分會通過低通濾波器,導致輸出信號頻譜出現(xiàn)雜散[7]。

2)小數(shù)分頻PLL 結構中數(shù)字ΔΣ調(diào)制器導致的雜散。ΔΣ調(diào)制器將輸出量轉化成模擬量時,因為電路的非理想性,ΔΣ調(diào)制器的量化噪聲會產(chǎn)生非線性失真,從而導致無法避免的雜散。常見的ΔΣ小數(shù)分頻PLL 大都采用數(shù)字ΔΣ調(diào)制器,數(shù)字ΔΣ調(diào)制器導致的雜散是PLL輸出噪聲的關鍵噪聲源[8]。

3 基于ΔΣ結構的DAC補償技術

盡管基于ΔΣ結構的小數(shù)分頻PLL 可以進行一定程度的噪聲整形,但其本身引入的量化噪聲,尤其是全數(shù)字ΔΣ調(diào)制器帶來的大量帶內(nèi)噪聲是不可忽略的[9]。通過犧牲環(huán)路帶寬可以濾除部分噪聲,但是環(huán)路帶寬設計過小會導致其他性能的惡化,因此帶寬對噪聲的抑制作用相對有限[10]。通過DAC噪聲補償技術可以大大提升PLL的帶內(nèi)噪聲性能。

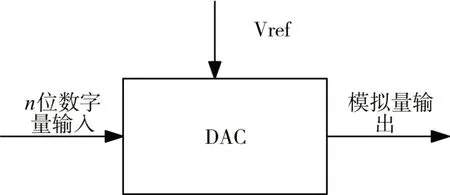

3.1 DAC技術

DAC 是數(shù)模轉換器(Digital-to-Analog Converter)的簡稱。DAC 完成將輸入的模擬量轉換為數(shù)字的輸出量的功能[11]。圖4 給出了一個簡單的DAC原理圖。DAC 輸入端接收到n位數(shù)字量,DAC 受參考頻率Vref的控制,逐拍輸出對應的模擬量。

圖4 DAC轉化原理圖

3.2 DAC噪聲補償技術在小數(shù)PLL中的應用

在小數(shù)PLL 中采用DAC 噪聲補償技術的主要目的通過補償ΔΣ調(diào)制器引入的量化噪聲,打破對帶寬的嚴格限制[12]。在PLL的設計過程中,帶寬始終是一個折衷的設計指標。就PLL系統(tǒng)而言,環(huán)路帶寬對VCO 的噪聲濾除效果呈現(xiàn)高通濾波特性,所以在不惡化其他性能的前提下,環(huán)路帶寬應盡可能地大。但是由于引入了ΔΣ調(diào)制器,ΔΣ調(diào)制器會使很多低頻噪聲抬升至高頻,此時一味的增大環(huán)路帶寬又會影響PLL的噪聲性能。

對于PLL系統(tǒng)來說,鑒相器和電荷泵引入的量化相相位誤差不僅與輸入頻率有關,而且受到反饋分頻器輸出的控制。在調(diào)制器穩(wěn)定工作的情況下,該誤差可以被預測。因此,可以通過在壓控振蕩器的輸入端注入補償量的方法消除相位誤差對輸出帶來的影響。

圖5 給出了一種采用DAC 補償技術的小數(shù)分頻型PLL 結構圖,在預測數(shù)字ΔΣ調(diào)制器產(chǎn)生量化噪聲后,通過DAC 向電荷泵注入補償電壓,從而改善PLL的噪聲性能。

在理想情況下,DAC補償技術可以完全消除量化誤差的影響。實際情況中,由于DAC 設計過程中存在的不匹配等問題,DAC在對量化噪聲補償?shù)耐瑫r,本身也在引入量化噪聲,使得補償效果達不到設計要求。ΔΣDAC 技術可以進一步提高補償效果。

圖5 使用DAC的小數(shù)分頻型PLL結構圖

ΔΣDAC 技術的核心思想是在不嚴重影響輸出精度的情況下,通過截位的方式把輸入的寬位數(shù)字量變?yōu)檎粩?shù)字量。減小數(shù)字量的位數(shù)既可以降低對DAC 精度的要求,又可以減小DAC 工作時的功耗。

其他如DAC 匹配技術、動態(tài)元件匹配技術等也常用于提升補償效果的設計中。

4 設計與仿真

4.1 PLL整體結構設計

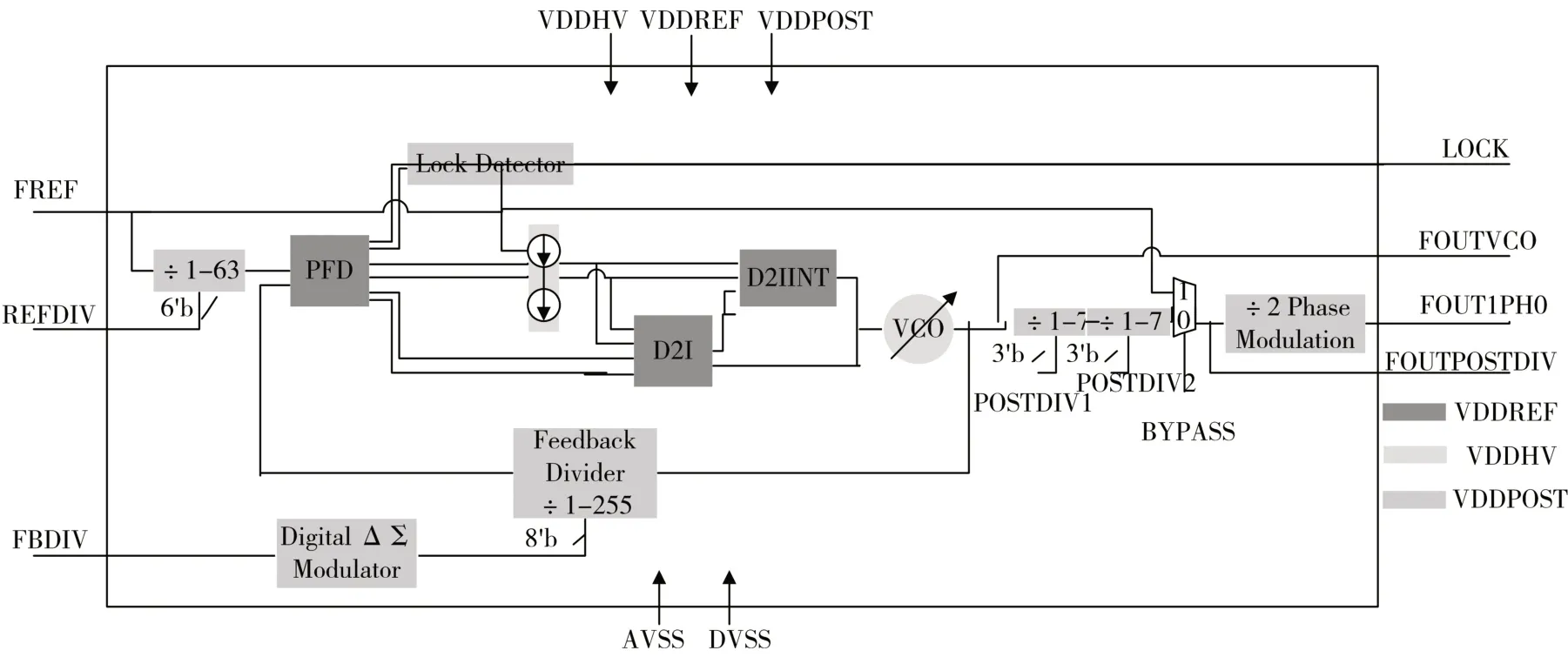

PLL 電路整體結構如圖6 所示。PLL 由前分頻器、鑒頻鑒相器、電荷泵、比例積分環(huán)路濾波器、壓控振蕩器、后分頻器、反饋分頻器組成。

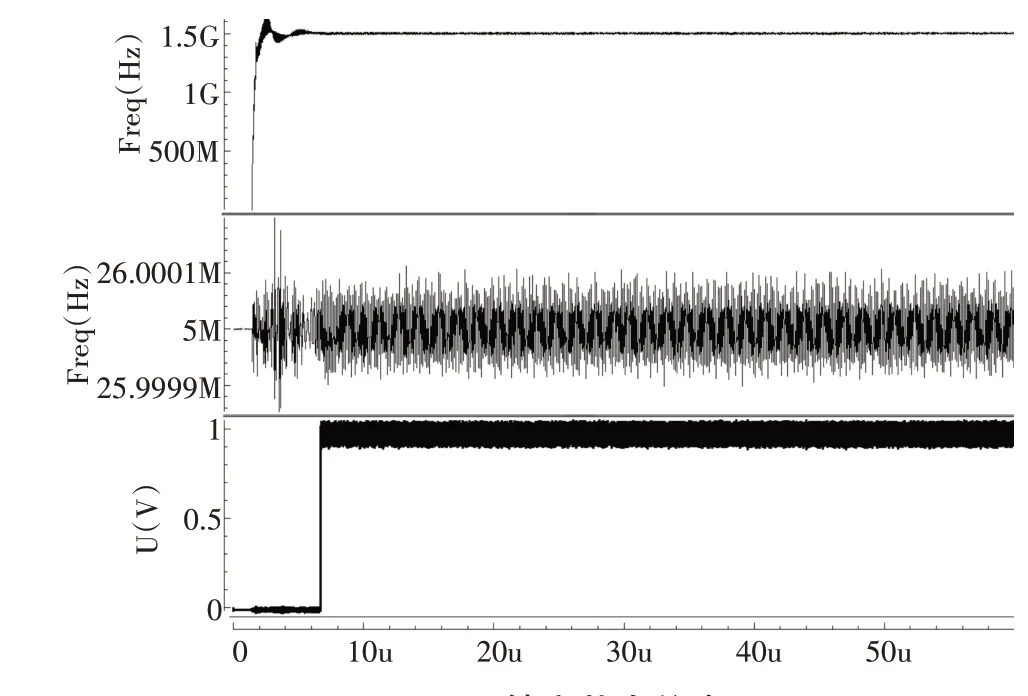

4.2 鎖定狀態(tài)仿真

在TT-corner 下對PLL 整體進行仿真,仿真結果如圖7 所示。在輸入?yún)⒖碱l率為26MHz 的情況下,PLL 正常鎖定在1.5GHz,滿足輸出要求。鎖定檢測模塊在6.69μs發(fā)出鎖定檢測信號,PLL 上電鎖定時間為1.83μs,滿足快速鎖定要求。

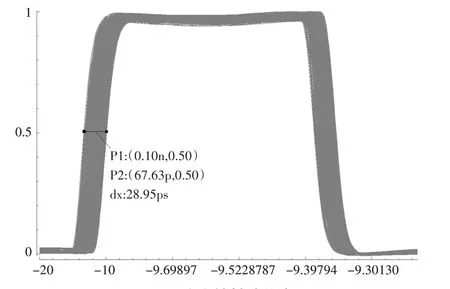

4.3 抖動性能仿真

抖動是數(shù)字系統(tǒng)信號完整性測試的核心內(nèi)容之一,是時鐘和串行信號最重要的測量參數(shù)。從時鐘抖動的來源分析,PLL 的抖動可以分為兩大類:確定性抖動和隨機抖動[13]。

確定性抖動是由各種可識別的干擾信號造成的,如EMI 輻射、電源噪聲、同步切換噪聲等,這種抖動幅度是有邊界的,而且可以通過電路設計優(yōu)化把干擾源消除或大幅降低。確定性抖動是可以重復的、可以預測的抖動。而隨機抖動因為沒有可以識別的模式,所以是不能預測的[14]。

圖6 PLL整體結構圖

圖7 PLL鎖定狀態(tài)仿真

圖8 給出了本款PLL 在TT-corner 下的確定性抖動仿真圖,確定性抖動為28.95ps。

圖8 確定性抖動仿真

4.4 相位噪聲仿真

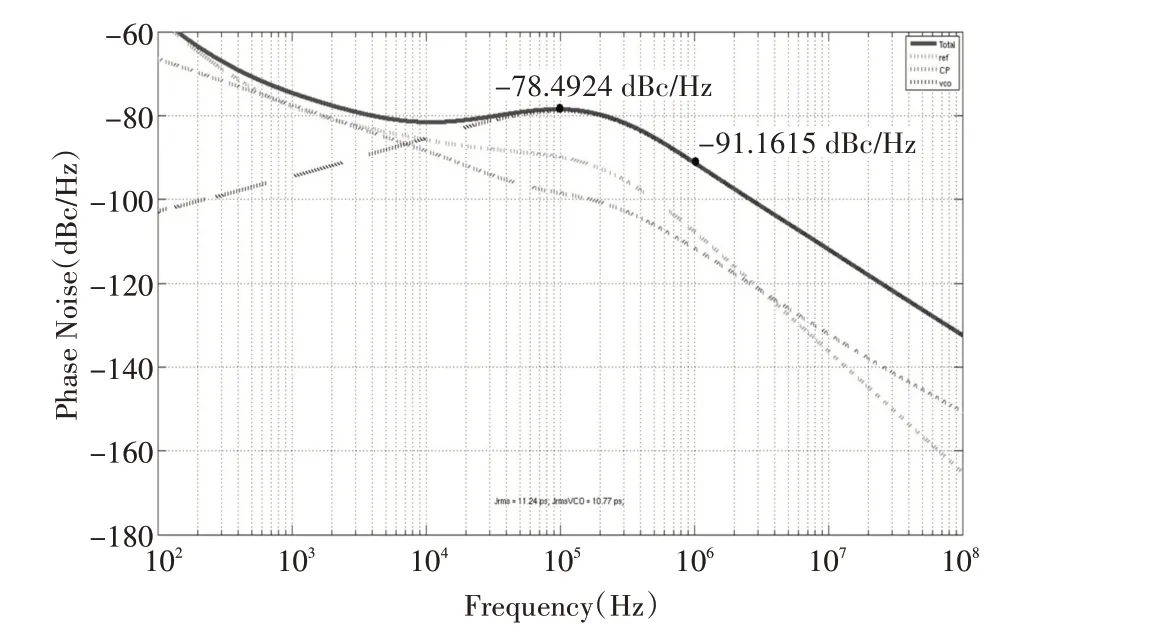

相位噪聲是對時鐘信號噪聲特性的頻域表征方式,表征時鐘信號頻率的穩(wěn)定度,是指偏離載波頻率處帶寬噪聲與載波信號總功率的比值,單位為dBc/Hz[15]。本 款PLL 相 位 噪 聲 如 下 圖 所 示,在100KHz 和1.0MHz 處的相位噪聲分別為-78.4924 dBc/Hz和-91.1615 dBc/Hz。

圖9 相位噪聲曲線

4.5 PLL版圖

本文實現(xiàn)的小數(shù)分頻PLL基于UMC28nm 標準工藝,版圖如圖10所示,芯片面積為0.06mm2。

圖10 PLL版圖

4.6 性能參數(shù)分析

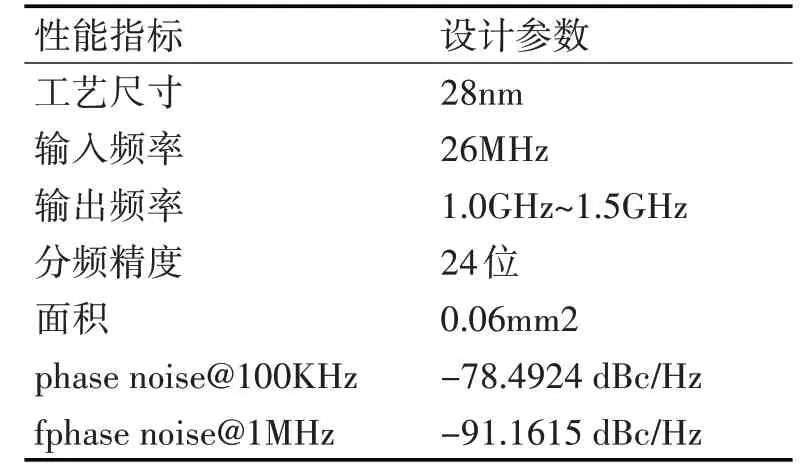

對版圖后帶寄生參數(shù)的電路進行仿真,得到如表1 所示的性能參數(shù)。本文基于UMC28nm 工藝設計了一款小數(shù)分頻PLL,PLL 可以穩(wěn)定工作在1.5GHz,分頻精度達24 位,在100kHz 頻偏處的相位噪聲僅為-78.4924dBc/Hz,充分證明本文采用的噪聲補償技術起到了很好的效果,鎖相環(huán)設計滿足高性能設計要求。

表1 性能參數(shù)列表

5 結語

本文在深入分析了ΔΣ小數(shù)分頻PLL 基本機構及其雜散來源的基礎上,著重研究了基于ΔΣ結構的DAC 噪聲補償技術,并基于此技術實現(xiàn)了一款高性能小數(shù)分頻PLL。仿真結果顯示,DAC 噪聲補償技術對PLL噪聲性能有明顯提升。