用于在片測(cè)試系統(tǒng)整體校準(zhǔn)的電阻標(biāo)準(zhǔn)件

丁晨 喬玉娥 劉巖 翟玉衛(wèi) 鄭世棋

摘要:為解決在片測(cè)試系統(tǒng)中1~1000Ω電阻無法進(jìn)行整體校準(zhǔn)問題,通過采用GaAs材料作為襯底,利用半導(dǎo)體工藝中薄膜濺射法,使用轟擊離子Ar+與靶材作用形成反應(yīng)層,激發(fā)出的濺射原子NiCr打至GaAs表面,制作薄膜電阻。采用方塊電阻為50Ω/塊,通過調(diào)節(jié)長與寬的比值,研制出1~1000Ω電阻標(biāo)準(zhǔn)件。為消除電阻測(cè)量過程中芯片內(nèi)部回路引線的影響,研制出相對(duì)應(yīng)的短路器。通過組建具有溫度控制系統(tǒng)的定標(biāo)裝置,在-40~100℃溫度下對(duì)標(biāo)準(zhǔn)件進(jìn)行定標(biāo),定標(biāo)結(jié)果表明電阻標(biāo)準(zhǔn)件的阻值與溫度具有良好的線性關(guān)系,短期重復(fù)性RSD優(yōu)于0.05%,年穩(wěn)定性RSD優(yōu)于0.1%,可以有效解決現(xiàn)有在片測(cè)試系統(tǒng)低值電阻參數(shù)的整體校準(zhǔn)問題。

關(guān)鍵詞:在片測(cè)試系統(tǒng);校準(zhǔn);薄膜濺射法;電阻標(biāo)準(zhǔn)件;短路器

中圖分類號(hào):TB971 文獻(xiàn)標(biāo)志碼:A 文章編號(hào):1674-5124(2019)07-0097-05

收稿日期:2018-10-10;收到修改稿日期:2018-12-03

作者簡介:丁晨(1991-),男,河北石家莊市人,助理工程師,主要從事電磁儀器計(jì)量技術(shù)研究。

0 引言

在片測(cè)試系統(tǒng)主要應(yīng)用于半導(dǎo)體、MEMS元器件等研發(fā)過程中的精密測(cè)量以及集成電路、封裝的測(cè)試。在片參數(shù)的準(zhǔn)確測(cè)量,可為研發(fā)人員提供可靠的測(cè)試數(shù)據(jù),降低封裝成本,縮短生產(chǎn)周期,保證最終器件的質(zhì)量可靠性[1]。電容、高值電阻、低值電阻3個(gè)在片電學(xué)參數(shù)測(cè)試是檢驗(yàn)元器件的準(zhǔn)確度和一致性的項(xiàng)目,也是監(jiān)測(cè)工藝質(zhì)量和成品率最重要和最直接的檢驗(yàn)環(huán)節(jié)。

目前國內(nèi)主要通過“拆分計(jì)量”方式,實(shí)現(xiàn)在片測(cè)試系統(tǒng)電學(xué)參數(shù)校準(zhǔn)。但是,拆分計(jì)量不僅給在片測(cè)試系統(tǒng)的穩(wěn)定性和準(zhǔn)確度帶來潛在風(fēng)險(xiǎn),而且無法消除從標(biāo)準(zhǔn)儀器端口至探針尖回路中由線纜、探針、矩陣開關(guān)、外界環(huán)境等因素引入的影響,導(dǎo)致探針端面測(cè)量結(jié)果的不準(zhǔn)確[2]。為了解決在片測(cè)試系統(tǒng)電學(xué)參數(shù)的整體校準(zhǔn)問題,喬玉娥[3]通過采用GaAs半導(dǎo)體材料硼離子注入后的高絕緣特性,研制出一種基于GaAs襯底的由2個(gè)金屬電極構(gòu)成的高值電阻標(biāo)準(zhǔn)件,解決了片上絕緣性能校準(zhǔn)問題;丁晨[4]通過利用MEMS梳齒電容工藝研制出電容標(biāo)準(zhǔn)件,解決了電容參數(shù)整體校準(zhǔn)問題。低值電阻在器件阻值測(cè)量、結(jié)構(gòu)導(dǎo)通特性檢測(cè)等方面有著極為重要的應(yīng)用,但目前尚無可用標(biāo)準(zhǔn)件解決系統(tǒng)中低值電阻參數(shù)的整體校準(zhǔn)問題。國際上,美國Cascade Microtech公司研制的校準(zhǔn)件當(dāng)中僅有50Q阻抗用于微波參數(shù)的校準(zhǔn)[5],并不適用于在片測(cè)試系統(tǒng)直流低值電阻的校準(zhǔn),因此無法滿足被校系統(tǒng)的需求。針對(duì)以上問題,本文利用半導(dǎo)體工藝中薄膜濺射法來制作薄膜電阻,研制出用于在片測(cè)試系統(tǒng)整體校準(zhǔn)的短路器、電阻標(biāo)準(zhǔn)件1~1000Ω,覆蓋了在片測(cè)試系統(tǒng)低值電阻測(cè)試范圍,組建可溯源至直流電阻參數(shù)國家最高基準(zhǔn)的定標(biāo)裝置對(duì)其進(jìn)行定標(biāo),解決了在片測(cè)試系統(tǒng)中1~1000Ω電阻的整體校準(zhǔn)問題。

1 標(biāo)準(zhǔn)件研制

1.1 標(biāo)準(zhǔn)件設(shè)計(jì)

制作電阻的工藝主要有MEMS體硅工藝和半導(dǎo)體工藝兩種。MEMS體硅工藝的主要優(yōu)勢(shì)是采用晶圓級(jí)封裝,受外界溫度影響小;缺點(diǎn)是成本高,且短路器的研制缺乏經(jīng)驗(yàn)。半導(dǎo)體工藝的主要優(yōu)勢(shì)是工藝線成熟,工藝偏差小;缺點(diǎn)是阻值受外界溫度影響大。在低值電阻測(cè)量方面,一般使用4線測(cè)量,可以有效消除引線、熱電勢(shì)的影響;為了解決低值電阻測(cè)量過程中芯片內(nèi)部回路引線對(duì)測(cè)量結(jié)果的影響,采用“短路補(bǔ)償”的方法固定系統(tǒng)誤差;消除零電阻的影響則需要研制短路器。半導(dǎo)體工藝在短路器制作方面更具有尺寸精準(zhǔn)、阻值偏差小等優(yōu)勢(shì),因此采用半導(dǎo)體工藝研制短路器及電阻標(biāo)準(zhǔn)件。

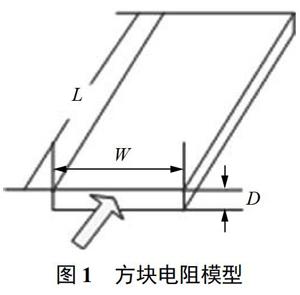

半導(dǎo)體工藝在制作電阻方面,常用的有摻雜法和薄膜濺射法[6]。摻雜法一般采用擴(kuò)散電阻法和離子注入法。擴(kuò)散電阻法精度較低,寄生效應(yīng)大;離子注入法需要一個(gè)高溫退火過程[7]。而薄膜濺射法則不需要高溫退火過程,這樣可以減少熱過程對(duì)微米級(jí)電路的不利影響,同時(shí)薄膜電阻的厚度更小,更能制作成較高精度的電阻,因此采用薄膜濺射法來制備電阻[8]。襯底可以選擇單晶si、SiC、GaAs,然而單晶si作為襯底制作電阻精度較差,SIC作為襯底制作電阻成本較高,GaAs作為襯底制作的電阻精度高且成本較低,因此采用GaAs材料作為襯底制作薄膜電阻[9]。濺射工藝制備的過程中,使用轟擊離子Ar與靶材作用形成反應(yīng)層,激發(fā)出的濺射原子NiCr打至GaAs表面,形成薄膜電阻[10-11]。根據(jù)研制的電阻范圍為1~1000Ω,因此工藝制作中選擇方塊電阻為50Ω/塊,模型如圖1所示。

電阻阻值計(jì)算公式如下所示:式中:L——電阻的長,μm;

W——電阻的寬,μm;

R1——方塊電阻的阻值,Ω。

制作過程中,首先固定方塊電阻R1的值為50Ω/塊不變,通過調(diào)節(jié)L與w的比值,達(dá)到目標(biāo)電阻R的制備。詳細(xì)長寬如表1所示。

1Ω電阻采用純金制作,總長度為1555μm,寬度為10μm,因此采用蛇形分布排列。

用于在片測(cè)試系統(tǒng)整體校準(zhǔn)的短路器、電阻標(biāo)準(zhǔn)件的尺寸設(shè)計(jì)為工藝平臺(tái)常用的10mm×10mm,整體結(jié)構(gòu)為單邊5PAD格式,每個(gè)PAD的尺寸為300μm×300μm。標(biāo)準(zhǔn)件版圖結(jié)構(gòu)設(shè)計(jì)如圖2所示。

使用4線測(cè)量可以有效消除引線、熱電勢(shì)的影響,但是為了解決電阻測(cè)量過程中芯片內(nèi)部回路引線對(duì)測(cè)量結(jié)果的影響,將電阻準(zhǔn)確定義在芯片的核心區(qū),即所測(cè)得的電阻值為去除引線后的值,則需要研制短路器。短路器的制作工藝與標(biāo)準(zhǔn)件相同,目標(biāo)電阻處由一根純金線連接,短路器結(jié)構(gòu)設(shè)計(jì)如圖3所示。

1.2 標(biāo)準(zhǔn)件制備

采用GaAs材料作為襯底,利用半導(dǎo)體工藝中薄膜濺射法,電阻標(biāo)準(zhǔn)件的制備流程如圖4所示。

首先對(duì)GaAs襯底進(jìn)行清洗;在襯底上淀積一層SiN介質(zhì)完成襯底的制備;制作電阻圖形光刻版進(jìn)行第1次光刻,將所需要的電阻圖形顯現(xiàn)出來;在電阻圖形上進(jìn)行薄膜濺射制作薄膜電阻;通過剝離的手段將不需要的材料去除;制作PAD圖形光刻版,進(jìn)行第2次光刻,將所需的PAD圖形顯現(xiàn)出來;在PAD圖形上利用電鍍工藝將金屬Au制作在PAD上;制作除PAD外的光刻版,進(jìn)行第3次光刻;最后通過淀積一層SiN介質(zhì)作為保護(hù)層,完成表面鈍化,最終完成整個(gè)器件的制作[12]。

在鈍化方面,半導(dǎo)體工藝屬于平面工藝,芯片是位于襯底之上薄薄的一層結(jié)構(gòu),這層結(jié)構(gòu)尺寸微小且容易被外界空氣氧化導(dǎo)致器件失效,因此芯片表面必須覆蓋一層SiN材料進(jìn)行鈍化,其目的是在芯片表面形成一層保護(hù)層,避免微小結(jié)構(gòu)受外界溫度、濕度、塵埃、電磁干擾的影響,能有效防止氧化,使得芯片的阻值更穩(wěn)定、壽命更長[13]。

已經(jīng)完成的GaAs晶圓片的厚度為500600μm,因此需要將其進(jìn)行減薄。一般晶圓片減薄后厚度范圍為80~200μm。基于 GaAs本身材料特性較脆,因此選擇200μm的厚度,既能劃片又能滿足后期裝載體不易太脆的需求。將劃片后的各個(gè)芯片固定在載體上完成整個(gè)電阻標(biāo)準(zhǔn)件的制作。

標(biāo)準(zhǔn)件的載體選擇Al2O3陶瓷[14],標(biāo)準(zhǔn)件屬于正面工藝,不需要共地,因此選擇陶瓷這種絕緣程度好的材料作為載體。在尺寸方面應(yīng)用50mm×50mm,這樣做的目的是使得真空吸附更好,樣片更加牢固,避免在測(cè)量過程中移動(dòng)所導(dǎo)致的數(shù)據(jù)不準(zhǔn)確。在厚度方面,選擇目前工藝中常使用的0.381mm。在平整度方面,使用單面拋光的陶瓷襯底,光滑的一面朝下與臺(tái)面接觸以保證足夠的吸附,磨砂的一面朝上用于粘附芯片以保證導(dǎo)電膠粘的粘性。使用導(dǎo)電膠將電阻標(biāo)準(zhǔn)件粘附在載體上,在150℃下固化3h。制作若干套標(biāo)準(zhǔn)件,其實(shí)物如圖5所示。

2 標(biāo)準(zhǔn)件定標(biāo)及考核

電阻阻值會(huì)隨溫度的變化而變化,而溫度變化對(duì)電阻阻值的影響是通過溫度系數(shù)來衡量的。溫度升高使物質(zhì)分子的熱運(yùn)動(dòng)加劇,電子在導(dǎo)體中流過時(shí),發(fā)生碰撞次數(shù)增多,使電阻增大;另一方面在溫度升高時(shí),物質(zhì)中自由電子數(shù)量增加,更容易導(dǎo)電,使電阻減小。但是在一般金屬電阻中,由于自由電子數(shù)幾乎不隨溫度升高增加,所以溫度升高時(shí)電阻增加。研制的電阻標(biāo)準(zhǔn)件所使用的材料為NiCr與金,所以其隨著溫度的升高,阻值增大,擁有一個(gè)正的溫度系數(shù)。為了達(dá)到準(zhǔn)確定標(biāo)電阻,仍需要對(duì)其在不同溫度下進(jìn)行定標(biāo)[15]。

2.1 標(biāo)準(zhǔn)件定標(biāo)

制作出的電阻標(biāo)準(zhǔn)件能否最終作為量傳專用標(biāo)準(zhǔn)件,需要對(duì)其進(jìn)行定標(biāo)及重復(fù)性、穩(wěn)定性考核。為了對(duì)電阻準(zhǔn)確定標(biāo),組建了具有溫度控制系統(tǒng)的定標(biāo)裝置[2,16]如圖6所示,主要由高精度數(shù)字多用表、溫度偏差優(yōu)于±0.5℃高低溫探針臺(tái)、探針座、連接線纜、屏蔽裝置等組成。該定標(biāo)裝置通過在片直通線直接溯源至742A四端對(duì)標(biāo)準(zhǔn)電阻,其可溯源至直流電阻參數(shù)國家最高基準(zhǔn)。

定標(biāo)時(shí)將電阻標(biāo)準(zhǔn)件通過真空吸附于探針臺(tái)卡盤上,使用探針座連接高精度數(shù)字多用表,選擇數(shù)字表4-wire電阻測(cè)量功能和對(duì)應(yīng)的電阻量程,調(diào)節(jié)臺(tái)溫控制在需要定標(biāo)的溫度;測(cè)量短路器,在標(biāo)準(zhǔn)儀器上進(jìn)行短路操作;短路完成后,對(duì)電阻標(biāo)準(zhǔn)件1~10000Ω分別進(jìn)行測(cè)量,記錄所測(cè)數(shù)據(jù)后,調(diào)節(jié)臺(tái)溫至下一個(gè)測(cè)試溫度點(diǎn),重復(fù)操作;最終測(cè)試完畢后,將探針座抬起足夠高的距離避免損傷探針和標(biāo)準(zhǔn)件。

2.2 標(biāo)準(zhǔn)件考核

利用定標(biāo)裝置對(duì)電阻標(biāo)準(zhǔn)件進(jìn)行考核,重復(fù)性的考核是短時(shí)間連續(xù)測(cè)量6次,實(shí)驗(yàn)相對(duì)標(biāo)準(zhǔn)偏差需滿足優(yōu)于0.05%;穩(wěn)定性的考核是一年內(nèi)間隔3個(gè)月考核共4次,4組數(shù)據(jù)的實(shí)驗(yàn)相對(duì)標(biāo)準(zhǔn)偏差需滿足優(yōu)于0.1%。按照此考核條件,選擇出符合要求的電阻標(biāo)準(zhǔn)件。

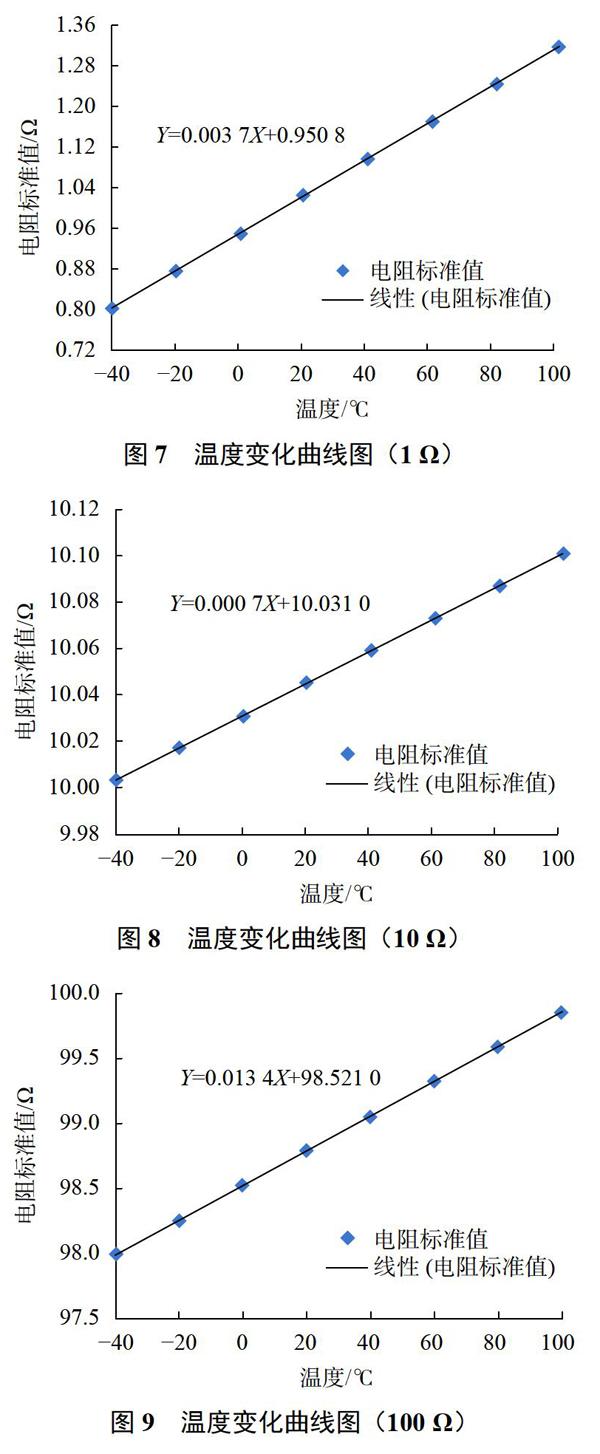

大部分通用的具有控溫系統(tǒng)的在片測(cè)試系統(tǒng)溫度范圍為-40~100℃,對(duì)電阻標(biāo)準(zhǔn)件(1Ω)在-40~100℃進(jìn)行重復(fù)性考核,數(shù)據(jù)如表2所示。

擬合成直線如圖7所示。

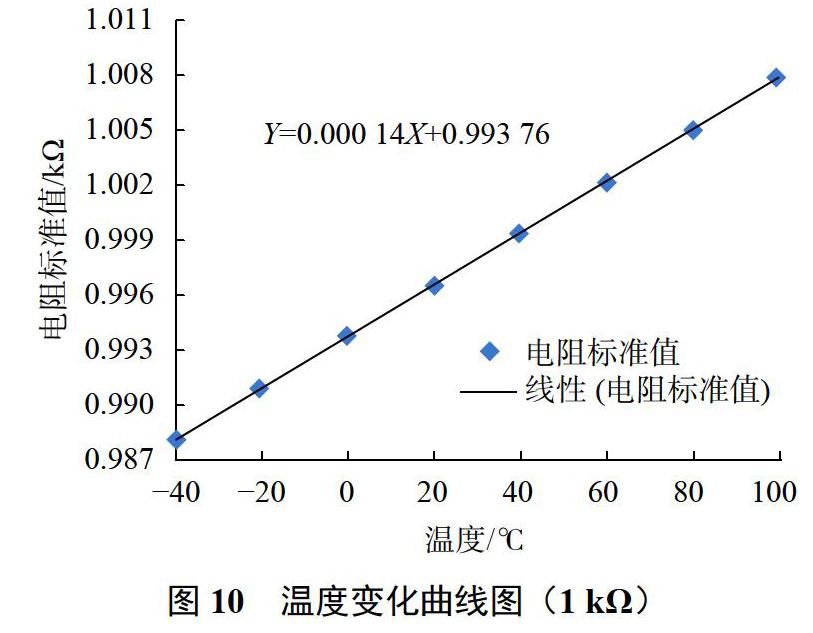

同樣的方法對(duì)電阻標(biāo)準(zhǔn)件10~1000Ω在溫度-40~100℃進(jìn)行考核,其溫度變化曲線及溫度變化規(guī)律如圖8、圖9、圖10所示。

對(duì)1~1000Ω的電阻在20℃進(jìn)行年穩(wěn)定性考核,考核數(shù)據(jù)如表3所示。

根據(jù)以上數(shù)據(jù)可知,研制的電阻標(biāo)準(zhǔn)件(1 S2)在溫度-40~100℃的短期重復(fù)性相對(duì)標(biāo)準(zhǔn)偏差均優(yōu)于0.05%,其年穩(wěn)定性相對(duì)標(biāo)準(zhǔn)偏差優(yōu)于0.1%。經(jīng)過對(duì)電阻標(biāo)準(zhǔn)件10~1000Ω進(jìn)行重復(fù)性和年穩(wěn)定性考核,研制的1~1000Ω的電阻標(biāo)準(zhǔn)樣件的短期重復(fù)性RSD均優(yōu)于0.05%,其年穩(wěn)定性RSD均優(yōu)于0.1%,滿足了作為電阻標(biāo)準(zhǔn)件的條件,可用于在片測(cè)試系統(tǒng)低值電阻參數(shù)現(xiàn)場(chǎng)整體校準(zhǔn)。

當(dāng)每次使用電阻標(biāo)準(zhǔn)件對(duì)不具有溫度控制系統(tǒng)的在片測(cè)試系統(tǒng)進(jìn)行校準(zhǔn)時(shí),電阻標(biāo)準(zhǔn)件都需要在校準(zhǔn)的環(huán)境中放置不少于2h,通過高精度溫濕度表,監(jiān)測(cè)探針臺(tái)附近的溫度,通過以上考核出來的溫度系數(shù)對(duì)校準(zhǔn)結(jié)果進(jìn)行修正,以保證校準(zhǔn)結(jié)果的準(zhǔn)確性。

3 結(jié)束語

本文利用半導(dǎo)體工藝研制的用于在片測(cè)試系統(tǒng)整體校準(zhǔn)的1~1000Ω電阻標(biāo)準(zhǔn)件,通過可溯源至直流電阻參數(shù)國家最高基準(zhǔn)的定標(biāo)裝置進(jìn)行定標(biāo)。考核出重復(fù)性RSD優(yōu)于0.05%,年穩(wěn)定性RSD優(yōu)于0.1%的電阻標(biāo)準(zhǔn)件,可對(duì)技術(shù)指標(biāo)在2%以上的在片測(cè)試系統(tǒng)的低值電阻參數(shù)、片上導(dǎo)通性能、無源器件的電阻參數(shù)開展校準(zhǔn)工作。本文研制的電阻標(biāo)準(zhǔn)件解決了在片測(cè)試系統(tǒng)中低值電阻參數(shù)的整體校準(zhǔn)問題,避免了拆分計(jì)量給在片測(cè)試系統(tǒng)的穩(wěn)定性和準(zhǔn)確度帶來的潛在風(fēng)險(xiǎn),同時(shí)排除了從標(biāo)準(zhǔn)儀器端口至探針尖回路中由線纜、探針、矩陣開關(guān)等因素引入的影響,保障了探針端面測(cè)量結(jié)果的準(zhǔn)確可靠,實(shí)現(xiàn)了在片測(cè)試系統(tǒng)電阻參數(shù)的有效溯源,可為半導(dǎo)體元器件的量產(chǎn)提供計(jì)量保障。

參考文獻(xiàn)

[1]喬玉娥,劉巖,程曉輝,等.MEMS晶圓級(jí)測(cè)試系統(tǒng)現(xiàn)狀及未來發(fā)展[J].傳感器與微系統(tǒng),2016,35(10):1-3.

[2]丁晨,喬玉娥,丁立強(qiáng),等.MEMS在片測(cè)試系統(tǒng)整體校準(zhǔn)技術(shù)探討[C].//2015國防計(jì)量與測(cè)試學(xué)術(shù)交流會(huì),2015.

[3]喬玉娥,劉巖,丁晨,等.MEMS片上絕緣性能測(cè)試高阻標(biāo)準(zhǔn)件研制[J].中國測(cè)試,2017,43(7):88-91.

[4]丁晨,喬玉娥,劉巖.MEMS在片測(cè)試系統(tǒng)電容參數(shù)校準(zhǔn)技術(shù)研究[J].中國計(jì)量,2016(12):94-96.

[5]CASCADE MICROTECH.Impedance Standard SubstrateMap[EB/OL].[20]7-10-05].https://www.formfactor.com.

[6]QUIRK M.半導(dǎo)體制造技術(shù)1M1-韓鄭生,等,譯.北京:電子工業(yè)出版社,2015:6.

[7]楊士慧,徐向前,田紅林,等.離子注入摻雜工藝研究[J].智能電網(wǎng),2017,5(8):748-751.

[8]PIERRET R F.半導(dǎo)體器件基礎(chǔ)[M].黃如,等,譯.北京:電子工業(yè)出版社,2004:11.

[9]WANG C,KIM N Y.Optimization of NiCr Thin FilmResistor on Semi-insulating-GaAs Substrate in AdvancedIntegrated Passive Device Process[J].IETE Journal ofResearch,2012,58(4):279-283.

[10]KWON Y,KIM N H,PYO G,et al.Structural and surfaceproperties of NiCr thin films prepared by DC magnetronsputtering under variation of annealing conditions[J].Microelectronic engineering,2005,3(4):314-320.

[11]張麗娟,王芳,孫承松,等.高穩(wěn)定Ni-Cr薄膜電阻的研究[J].微處理機(jī),2005,26(4):7-8.

[12]張淵.半導(dǎo)體制造工藝[M].北京:機(jī)械工業(yè)出版社,2015:8.

[13]LEE J S,VESCAN A,WIE A,et al.Characteristics ofAIGaN/GaN HEMT devices with SiN passivation[C]//International Electron Devices Meeting,2000.

[14]RAMBO C,SIEBER H.Novel Synthetic Route to BiomorphicA1203 Ceramics[J].Cheminform,2010,36(26):1088-1091.

[15]任麗英.測(cè)定金屬電阻溫度系數(shù)的方法研究[J].大學(xué)物理實(shí)驗(yàn),2010,23(5):7-9.

[16]陳巒,唐毅.電阻溫度系數(shù)測(cè)試系統(tǒng)[J].輕工科技,2008,24(1):27-29.

(編輯:莫婕)