基于FFT頻偏估計算法改進與實現*

王 菊,范雪林,樊小琴

(中國電子科技集團公司第三十研究所,四川 成都 610041)

0 引 言

數字突發通信已被大量應用于衛星時分多址(Time division multiple access,TDMA)系統和陸基移動蜂窩通信系統中,而π/4四相相對相移鍵控(Pi/4 Differential Quadrature Reference Phase Shift Keying,π/4 DQPSK)調制技術由于具有頻譜特性好、頻譜利用率高、抗多普勒頻移等顯著特點,在移動通信、衛星通信中得到了廣泛應用[1-2]。

由于突發信號特征,通常情況下,發射端會使用數據加前導碼的幀結構,利用數據之前的已知前導碼來進行信號檢測和同步[3]。在通信系統中,由于收發本振頻率之間存在頻差,而且對于部分移動通信系統還存在著較大的多普勒頻移,因此每次突發幀同步都需要進行載波頻偏估計和校正。

文獻[4]提出了一種針對π/4 DQPSK調制方式的通信系統,利用特殊前導碼,通過對前導碼做FFT來進行信號檢測和頻偏估計。該方法簡單易行,工程易實現,但在實際通信過程中,考慮突發干擾和噪聲影響,本文在此基礎上進行適當改進,將前導碼字分為多段補零,通過多次快速傅立葉變換(Fast Fourier Transformation,FFT)計算頻偏,將頻偏估計結果排序,進行差值篩選,去除偏離較大值,將余下頻偏估計結果取均值作為最終估計結果,減少突發干擾的影響。

1 信號模型

信號傳輸模型如圖1所示。

圖1 信號傳輸模型

在發射端,前導碼插入數據前面,為了FFT計算頻偏具有良好的峰值,前導碼設計為“001100110011…….”,分成IQ兩路后,數據分別為”010101….”。將用戶數據和前導碼進行拼接后,經過串并轉換,進行π/4DQPSK調制,成型濾波,得到s1(kT),然后上變頻,形成發射信號S(t)。S(t)經過信道傳輸,在接收端,通過射頻接收信號R(t),然后經過A/D變換,數字下變頻處理,得到數字基帶信號。

其中,sk=Ik+j·Qk為調制符號信息,nk為復高斯白噪聲。然后對rk進行信號檢測,在檢測到信號后,利用前導碼進行頻偏估計,頻偏估計完成后進一步進行匹配濾波,定時同步,實現最佳采樣,最后進行差分解調,恢復出原始信息[5-6]。

2 算法描述及改進

由于前導碼采用了“001100110011……”特殊設計,星座映射為相鄰星座點,經過FFT變換后,同步頭信號的特征譜線具有明顯的尖峰。以同步頭L=64個符號,8倍采樣,SNR=5 dB,采樣率為96 KHz,符號速率為12 kHz,無頻偏時對同步頭做512點FFT變換,其頻譜特性如圖2所示。

圖2 同步頭頻譜特性

文獻[4]提出了利用同步頭的FFT變換完成信號檢測和頻偏估計。如圖2中幅度較高的譜線為同步頭信號的特征譜線,其幅度表征為信號功率,其X軸則表示頻率。無頻偏時,譜線的最大峰值位于零頻位置,有頻偏時同步頭的特征譜線與無頻偏時相比,最大點的位置會發生變化,這是由信道頻偏引起的,假設特征譜線中最大點的位置相對無頻偏時偏移為k,則其對應頻率為k/N×fs(N為FFT點數,fs為采樣頻率),即為估計出的頻偏值[7-8]。

為了提高頻偏估計精度和對抗同步頭中的短時突發干擾,本文在文獻[4]的基礎上進行改進,提出基于特殊前導碼的頻偏估計算法,具體步驟如下:

(1)根據信號檢測的起始位置,對信號進行分段,例如同步頭L=64個符號,8倍采樣,共512個點,按照50個樣點滑動,即[x1,x2,x3…x256],[x51,x52,x53…x306]…[x251,x252,x253…x506]等劃分成 6段信號;

(2)將分段后信號 [xn,xn+1,xn+2…xn+256]進行補零,補零個數為N-256(N為FFT點數),然后進行FFT變換,以便提高信號分辨率;

(3)求取頻譜中的最大值位置nmax,然后估計頻偏值 Δf=(nmax-N/2)/N×fs;

(4)依次求出每段頻偏估計值Δf1,Δf2,Δf3,Δf4,Δf5和 Δf6;

(5)將所有頻偏估計值排序,兩兩進行差值比較,當差值大于設定門限,則去掉該頻偏估計值,對剩余頻偏估計值求均值作為當前信號的頻偏Δfmean。

3 仿真及結果分析

為了驗證基于特殊前導碼字FFT頻偏估計算法的有效性。對該算法進行計算機仿真,仿真條件和參數主要有:調制方式為π/4DQPSK調制,同步頭符號數L=64,8倍符號率采樣,采樣率為96 KHz,符號速率為12 kbps,SNR=5 dB。仿真在無突發干擾條件下,頻偏分別為100 Hz和1 kHz條件下,改進算法FFT點數取8192,改進前后頻偏估計結果。

圖3-6的仿真結果可以看出,改進后估計值更精準,根據頻率估計的歸一化標準均方根誤差[9-10](Normalized root mean square error,NRMSE)定義:

下面將改進前后NRMSE值進行對比分析。

圖3 頻偏100 Hz條件下,改進前頻偏估計仿真結果

圖4 頻偏100 Hz條件下,改進后頻偏估計仿真結果

圖5 頻偏1 KHz條件下,改進前頻偏估計仿真結果

圖6 頻偏1 KHz條件下,改進后頻偏估計仿真結果

圖7給出了當頻偏為1 KHz條件下,不同信噪比條件下,改進前后,頻偏估計NRMSE的比較。從圖7中可以看出,改進后頻偏估計精度優于改進前,該估計算法在低信噪比條件下,估計效果良好。

圖7 改進前后頻偏估計NRMSE與信噪比關系對比仿真結果

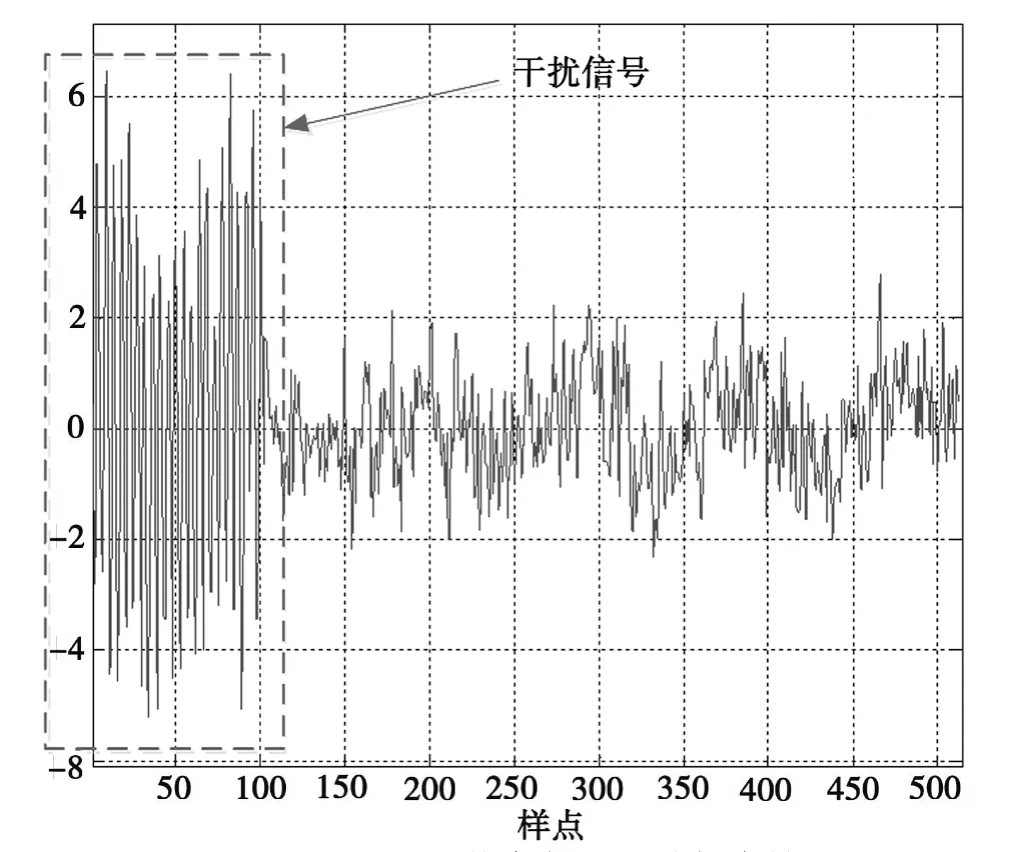

仿真在同步頭受短時突發干擾,頻偏為100 Hz條件下,改進前后頻偏估計結果。圖8和圖9給出了同步頭在受短時突發干擾的時域波形及干擾部分的頻域仿真結果。

根據仿真結果圖10可以看出通過改進后算法在受短時突發干擾時,仍能有效估計頻偏。

4 改進算法的FPGA實現

改進后基于特殊前導碼FFT頻偏估計算法的現場可編程門陣列(Field-Programmable Gate Array,FPGA)實現框圖如圖11所示。

圖8 短時突發干擾條件下時域仿真結果

圖9 短時突發干擾條件下頻域仿真結果

圖10 短時突發干擾條件下,頻偏估計NRMSE與信噪比關系對比仿真結果

圖11 改進算法FPGA實現原理圖

假設數據速率為12 kbps,采樣率為96 KHz,在FPGA實現時,根據信號檢測確定信號起始位置,通過深度為512的隨機存取存儲器(Random Access Memory,RAM)完成數據緩存,在完成256個符號緩存后,采用高倍時鐘讀出并補零,然后完成8 192個點FFT運算,計算當次頻偏值,并將頻偏值進行排序緩存,然后每多緩存50個點完成一次FFT運算,直到完成6次頻偏估計。為了在50個樣點時間內完成數據讀出,FPGA處理時鐘為4.8 MHz。完成6次頻偏估計后,將頻偏值進行比較,排除差值較大值,然后求取余下頻偏值均值,完成頻偏估計。其中modelsim仿真結果如圖12所示,FPGA為了計算方便,不直接計算頻率值,在完成偏移點估算后,再進行換算。

圖12 改進算法FPGA實現modelsim仿真結果

5 結 語

從仿真結果可以看出,改進算法,通過增加適當的同步頭長度,能夠獲得更優的頻率估計精度,抵抗短時突發干擾影響,算法實現簡單,易于工程硬件編程實現。