基于AD7732的石英撓性加速度計數(shù)據(jù)采集系統(tǒng)的設(shè)計

楊濤 虞翔 吳海林

摘 要:針對光纖慣性測量單元(IMU)中加速度器件的指標要求,介紹了石英撓性加速度計數(shù)據(jù)采集系統(tǒng)的設(shè)計,設(shè)計中采用了高精度的24位Σ-Δ型A/D轉(zhuǎn)換器AD7732和FPGA芯片 EP4CE75U19I7N來完成系統(tǒng)功能,詳細描述了硬件電路設(shè)計,并對軟件設(shè)計做了相關(guān)介紹。

關(guān)鍵詞:石英撓性加速度計;數(shù)據(jù)采集系統(tǒng);AD7732;FPGA

中圖分類號:TH824.4 文獻標識碼:A 文章編號:1671-2064(2019)14-0019-03

0 引言

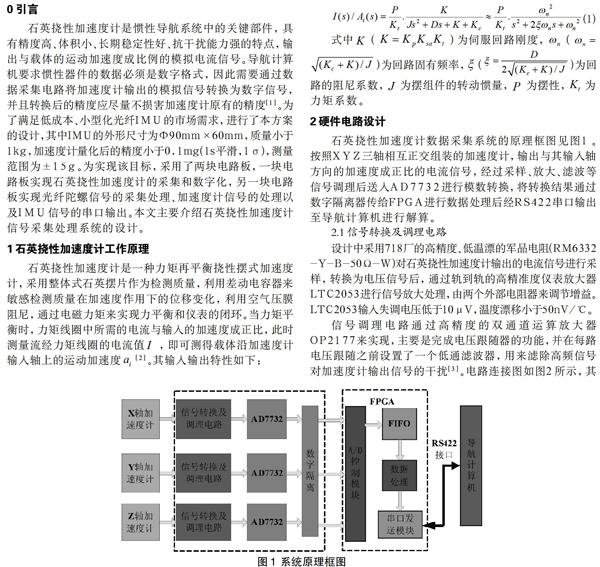

石英撓性加速度計是慣性導(dǎo)航系統(tǒng)中的關(guān)鍵部件,具有精度高、體積小、長期穩(wěn)定性好、抗干擾能力強的特點,輸出與載體的運動加速度成比例的模擬電流信號。導(dǎo)航計算機要求慣性器件的數(shù)據(jù)必須是數(shù)字格式,因此需要通過數(shù)據(jù)采集電路將加速度計輸出的模擬信號轉(zhuǎn)換為數(shù)字信號,并且轉(zhuǎn)換后的精度應(yīng)盡量不損害加速度計原有的精度[1]。為了滿足低成本、小型化光纖IMU的市場需求,進行了本方案的設(shè)計,其中IMU的外形尺寸為Φ90mm×60mm,質(zhì)量小于1kg,加速度計量化后的精度小于0.1mg(1s平滑,1σ),測量范圍為±15g。為實現(xiàn)該目標,采用了兩塊電路板,一塊電路板實現(xiàn)石英撓性加速度計的采集和數(shù)字化,另一塊電路板實現(xiàn)光纖陀螺信號的采集處理、加速度計信號的處理以及IMU信號的串口輸出。本文主要介紹石英撓性加速度計信號采集處理系統(tǒng)的設(shè)計。

1 石英撓性加速度計工作原理

石英撓性加速度計是一種力矩再平衡撓性擺式加速度計,采用整體式石英擺片作為檢測質(zhì)量,利用差動電容器來敏感檢測質(zhì)量在加速度作用下的位移變化,利用空氣壓膜阻尼,通過電磁力矩來實現(xiàn)力平衡和儀表的閉環(huán)。當力矩平衡時,力矩線圈中所需的電流與輸入的加速度成正比,此時測量流經(jīng)力矩線圈的電流值,即可測得載體沿加速度計輸入軸上的運動加速度[2]。其輸入輸出特性如下:

2 硬件電路設(shè)計

石英撓性加速度計數(shù)據(jù)采集系統(tǒng)的原理框圖見圖1。按照XYZ三軸相互正交組裝的加速度計,輸出與其輸入軸方向的加速度成正比的電流信號,經(jīng)過采樣、放大、濾波等信號調(diào)理后送入AD7732進行模數(shù)轉(zhuǎn)換,將轉(zhuǎn)換結(jié)果通過數(shù)字隔離器傳給FPGA進行數(shù)據(jù)處理后經(jīng)RS422串口輸出至導(dǎo)航計算機進行解算。

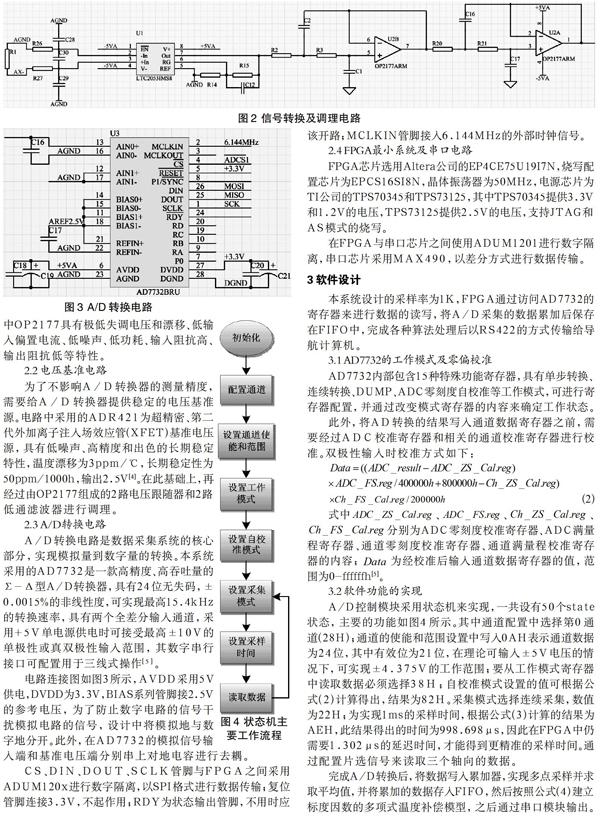

2.1 信號轉(zhuǎn)換及調(diào)理電路

設(shè)計中采用718廠的高精度、低溫漂的軍品電阻(RM6332 -Y-B-50Ω-W)對石英撓性加速度計輸出的電流信號進行采樣,轉(zhuǎn)換為電壓信號后,通過軌到軌的高精準度儀表放大器LTC2053進行信號放大處理,由兩個外部電阻器來調(diào)節(jié)增益。LTC2053輸入失調(diào)電壓低于10μV,溫度漂移小于50nV/℃。

信號調(diào)理電路通過高精度的雙通道運算放大器OP2177來實現(xiàn),主要是完成電壓跟隨器的功能,并在每路電壓跟隨之前設(shè)置了一個低通濾波器,用來濾除高頻信號對加速度計輸出信號的干擾[3]。電路連接圖如圖2所示,其中OP2177具有極低失調(diào)電壓和漂移、低輸入偏置電流、低噪聲、低功耗、輸入阻抗高、輸出阻抗低等特性。

2.2 電壓基準電路

為了不影響A/D轉(zhuǎn)換器的測量精度,需要給A/D轉(zhuǎn)換器提供穩(wěn)定的電壓基準源。電路中采用的ADR421為超精密、第二代外加離子注入場效應(yīng)管(XFET)基準電壓源,具有低噪聲、高精度和出色的長期穩(wěn)定特性,溫度漂移為3ppm/℃,長期穩(wěn)定性為50ppm/1000h,輸出2.5V[4]。在此基礎(chǔ)上,再經(jīng)過由OP2177組成的2路電壓跟隨器和2路低通濾波器進行調(diào)理。

2.3 A/D轉(zhuǎn)換電路

A/D轉(zhuǎn)換電路是數(shù)據(jù)采集系統(tǒng)的核心部分,實現(xiàn)模擬量到數(shù)字量的轉(zhuǎn)換。本系統(tǒng)采用的AD7732是一款高精度、高吞吐量的Σ-Δ型A/D轉(zhuǎn)換器,具有24位無失碼,±0.0015%的非線性度,可實現(xiàn)最高15.4kHz的轉(zhuǎn)換速率,具有兩個全差分輸入通道,采用+5V單電源供電時可接受最高±10V的單極性或真雙極性輸入范圍,其數(shù)字串行接口可配置用于三線式操作[5]。

電路連接圖如圖3所示,AVDD采用5V供電,DVDD為3.3V,BIAS系列管腳接2.5V的參考電壓,為了防止數(shù)字電路的信號干擾模擬電路的信號,設(shè)計中將模擬地與數(shù)字地分開。此外,在AD7732的模擬信號輸入端和基準電壓端分別串上對地電容進行去耦。

CS、DIN、DOUT、SCLK管腳與FPGA之間采用ADUM120x進行數(shù)字隔離,以SPI格式進行數(shù)據(jù)傳輸;復(fù)位管腳連接3.3V,不起作用;RDY為狀態(tài)輸出管腳,不用時應(yīng)該開路;MCLKIN管腳接入6.144MHz的外部時鐘信號。

2.4 FPGA最小系統(tǒng)及串口電路

FPGA芯片選用Altera公司的EP4CE75U19I7N,燒寫配置芯片為EPCS16SI8N,晶體振蕩器為50MHz,電源芯片為TI公司的TPS70345和TPS73125,其中TPS70345提供3.3V和1.2V的電壓,TPS73125提供2.5V的電壓,支持JTAG和AS模式的燒寫。

在FPGA與串口芯片之間使用ADUM1201進行數(shù)字隔離,串口芯片采用MAX490,以差分方式進行數(shù)據(jù)傳輸。

3 軟件設(shè)計

本系統(tǒng)設(shè)計的采樣率為1K,F(xiàn)PGA通過訪問AD7732的寄存器來進行數(shù)據(jù)的讀寫,將A/D采集的數(shù)據(jù)累加后保存在FIFO中,完成各種算法處理后以RS422的方式傳輸給導(dǎo)航計算機。

3.1 AD7732的工作模式及零偏校準

AD7732內(nèi)部包含15種特殊功能寄存器,具有單步轉(zhuǎn)換、連續(xù)轉(zhuǎn)換、DUMP、ADC零刻度自校準等工作模式,可進行寄存器配置,并通過改變模式寄存器的內(nèi)容來確定工作狀態(tài)。

3.2 軟件功能的實現(xiàn)

A/D控制模塊采用狀態(tài)機來實現(xiàn),一共設(shè)有50個state狀態(tài),主要的功能如圖4所示。其中通道配置中選擇第0通道(28H);通道的使能和范圍設(shè)置中寫入0AH表示通道數(shù)據(jù)為24位,其中有效位為21位,在理論可輸入±5V電壓的情況下,可實現(xiàn)±4.375V的工作范圍;要從工作模式寄存器中讀取數(shù)據(jù)必須選擇38H;自校準模式設(shè)置的值可根據(jù)公式(2)計算得出,結(jié)果為82H。采集模式選擇連續(xù)采集,數(shù)值為22H;為實現(xiàn)1ms的采樣時間,根據(jù)公式(3)計算的結(jié)果為AEH,此結(jié)果得出的時間為998.698μs,因此在FPGA中仍需要1.302μs的延遲時間,才能得到更精準的采樣時間。通過配置片選信號來讀取三個軸向的數(shù)據(jù)。

完成A/D轉(zhuǎn)換后,將數(shù)據(jù)寫入累加器,實現(xiàn)多點采樣并求取平均值,并將累加的數(shù)據(jù)存入FIFO,然后按照公式(4)建立標度因數(shù)的多項式溫度補償模型,之后通過串口模塊輸出。

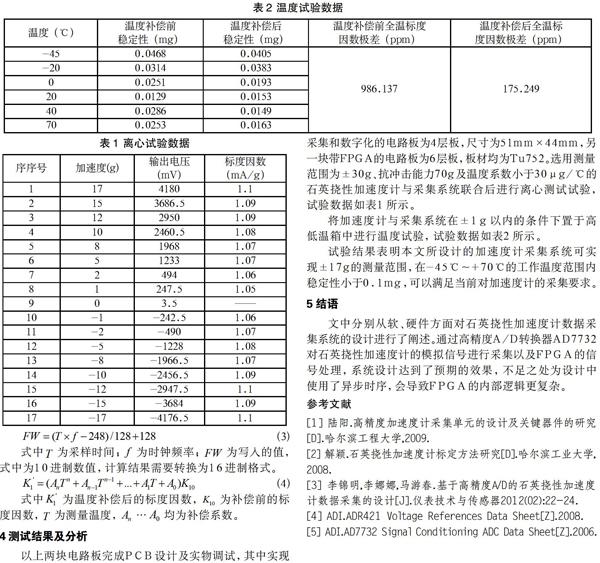

4 測試結(jié)果及分析

以上兩塊電路板完成PCB設(shè)計及實物調(diào)試,其中實現(xiàn)采集和數(shù)字化的電路板為4層板,尺寸為51mm×44mm,另一塊帶FPGA的電路板為6層板,板材均為Tu752。選用測量范圍為±30g、抗沖擊能力70g及溫度系數(shù)小于30μg/℃的石英撓性加速度計與采集系統(tǒng)聯(lián)合后進行離心測試試驗,試驗數(shù)據(jù)如表1所示。

將加速度計與采集系統(tǒng)在±1g以內(nèi)的條件下置于高低溫箱中進行溫度試驗,試驗數(shù)據(jù)如表2所示。

試驗結(jié)果表明本文所設(shè)計的加速度計采集系統(tǒng)可實現(xiàn)±17g的測量范圍,在-45℃~+70℃的工作溫度范圍內(nèi)穩(wěn)定性小于0.1mg,可以滿足當前對加速度計的采集要求。

5 結(jié)語

文中分別從軟、硬件方面對石英撓性加速度計數(shù)據(jù)采集系統(tǒng)的設(shè)計進行了闡述。通過高精度A/D轉(zhuǎn)換器AD7732對石英撓性加速度計的模擬信號進行采集以及FPGA的信號處理,系統(tǒng)設(shè)計達到了預(yù)期的效果,不足之處為設(shè)計中使用了異步時序,會導(dǎo)致FPGA的內(nèi)部邏輯更復(fù)雜。

參考文獻

[1] 陸陽.高精度加速度計采集單元的設(shè)計及關(guān)鍵器件的研究[D].哈爾濱工程大學,2009.

[2] 解穎.石英撓性加速度計標定方法研究[D].哈爾濱工業(yè)大學,2008.

[3] 李錦明,李娜娜,馬游春.基于高精度A/D的石英撓性加速度計數(shù)據(jù)采集的設(shè)計[J].儀表技術(shù)與傳感器2012(02):22-24.

[4] ADI.ADR421 Voltage References Data Sheet[Z].2008.

[5] ADI.AD7732 Signal Conditioning ADC Data Sheet[Z].2006.