基于列車實時數據協議的以太網高速通信技術

趙辰陽 王立德 簡 捷 李召召

(北京交通大學電氣工程學院, 100044, 北京//第一作者,碩士研究生)

0 引言

隨著車載智能設備和工業控制網絡應用的擴展,列車通信網絡(TCN)傳輸的數據類型和數據量在不斷增大,傳統現場總線技術已經難以滿足列車通信網絡不斷提高的帶寬需求。與此同時,列車的智能化程度越來越高,TCN的作用已經不只是簡單的數據傳輸,還需要實現更多的功能,比如數據分類傳輸、網絡故障診斷、優先級調度等。目前的現場總線技術已經成為限制TCN發展的瓶頸,隨著以太網在工業領域的普及以及不斷完善,基于以太網的TCN逐漸成為了研究的熱點。

雖然工業以太網技術作為IEC 61375標準的新成員,已逐漸成為下一代TCN的潮流,但是工業以太網尚有一個重要的問題有待解決:工業以太網通信速率不高、帶寬小,不能高速傳輸過程數據和消息數據。

已有學者嘗試解決上述問題。文獻[1]將列車實時數據協議(TRDP)應用到列車控制管理系統中,通過使用新型TRDP,來提高TCN的通信速率,解決以太網通信速率低的問題;文獻[2]通過引入時分復用機制,提出了一種新的以太網列車的通信速率改進方法;文獻[3]提出了一種新型的基于以太網的TCN系統,從控制策略入手進一步改進以太網列車速率低的問題。本文在已有研究的基礎上,首先從總線接口入手,提出了一種片間總線通信協議,將片間總線通信速率提升至百兆左右;然后通過信號完整性分析,在硬件上,從反射問題入手,大大降低高速數據傳輸下信號波形發生畸變的概率,保證高速數據傳輸的可行性;最后提升TRDP傳輸過程數據與消息數據的性能。

1 片間總線接口技術

1.1 片間總線時序邏輯

本文提出的片間總線主要用在以FPGA(現場可編程門陣列)為主導的大批量、高速率數據的傳輸應用。

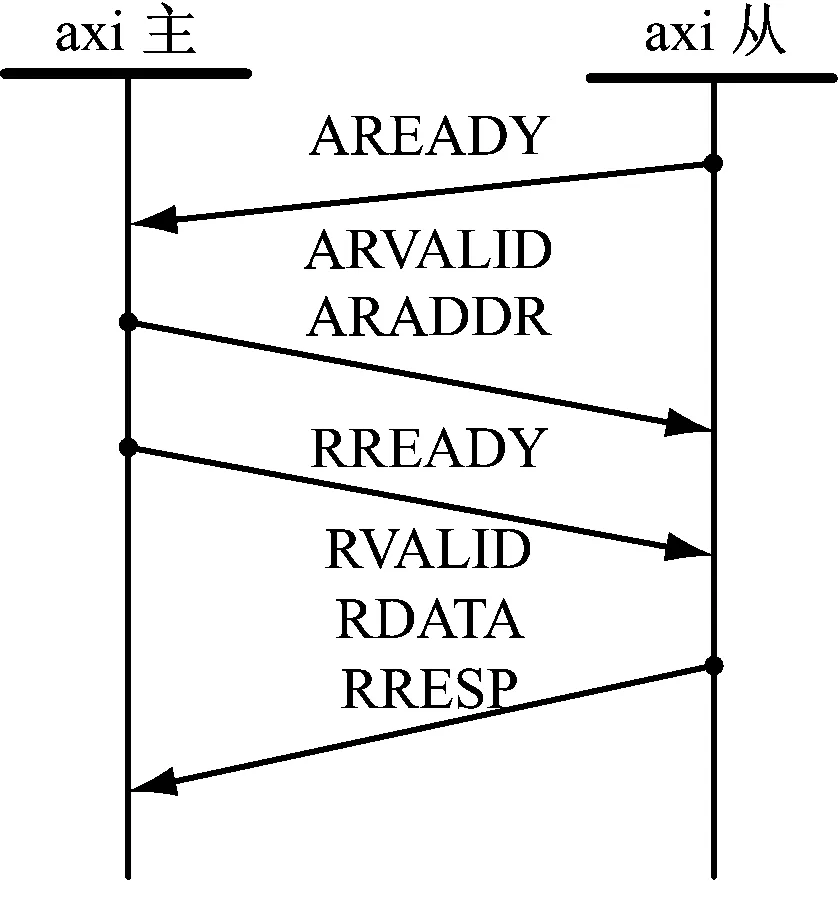

該片間總線所采用的是一種READY-V ALID握手通信機制。FPGA與ARM(高級RISC(精簡指令集計算機)微處理器)進行數據通信之前,先根據操作對各所用到的數據、地址通道進行握手。主要操作包括FPGA接收到ARM的 READY 信號后,將數據與 VALID 信號同時發送給 ARM,這是一種典型的握手機制,如圖1所示。

注:ACLK為片間總線時鐘信號

本文設計的片間總線包含4組通道:讀寫地址通道、讀寫數據通道,以及相應的寫應答通道和系統通道:

(1) 讀地址通道:主要包含 ARVALID、ARADDR、ARREADY等信號。

(2) 寫地址通道:主要包含 AWVALID、AWADDR、AWREADY信號。

(3) 讀數據通道:包含 RVALID、RDATA、RREADY、RRESP 信號。

(4) 寫數據通道:包含 WVALID、WDATA、WSTRB、WREADY 信號。

(5) 寫應答通道:包含 BVALID、BRESP、BREADY 信號。

(6) 系統通道:包含 ACLK、ARESETN 信號。

其中,ARESETN為復位信號,低電平有效;READY與VALID是對應的通道握手信號;BRESP 與 RRESP 分別為寫回應信號和讀回應信號。其讀寫操作順序如圖2所示。

讀操作順序為主節點與從節點進行讀地址通道握手并傳輸地址內容,然后在讀數據通道握手并傳輸所讀內容以及讀取操作的回應,時鐘上升沿有效;寫操作順序為主節點與從節點進行寫地址通道握手并傳輸地址內容,然后在寫數據通道握手并傳輸所讀內容,最后再寫回對應通道,并傳輸寫回應數據,時鐘上升沿有效。

本文有限狀態機(FSM)的設計采用的是一種時序電路設計常用的設計方式,尤其適合設計數字系統的控制模塊。FSM具有速度快、結構簡單、可靠性高等優點。片間總線主要通過FSM對片間總線從進行相關的數據及地址訪問。其讀寫狀態的狀態轉移圖如圖3所示。

圖3 讀寫狀態的狀態轉移圖

圖3所示的狀態轉移圖一共設置了8個狀態,分別是復位(RESET)、讀寫初始化(RD_IDLE、WR_IDLE)、讀寫地址等待(RA_WAIT、WA_WAIT)、讀寫地址就緒(RA_START、WA_START)、讀寫數據等待(RD_WAIT、WD_WAIT)、讀寫數據進行(RD_PROC、WD_PROC)、寫完成等待(WR_WAIT)及讀寫完成(RD_DONE、WR_DONE)。FSM按照此狀態轉移圖過程對片間總線從寫數據,實現FPGA到ARM端的數據傳輸。ARM到FPGA數據傳輸的過程與寫流程相似。

1.2 突發模式邏輯

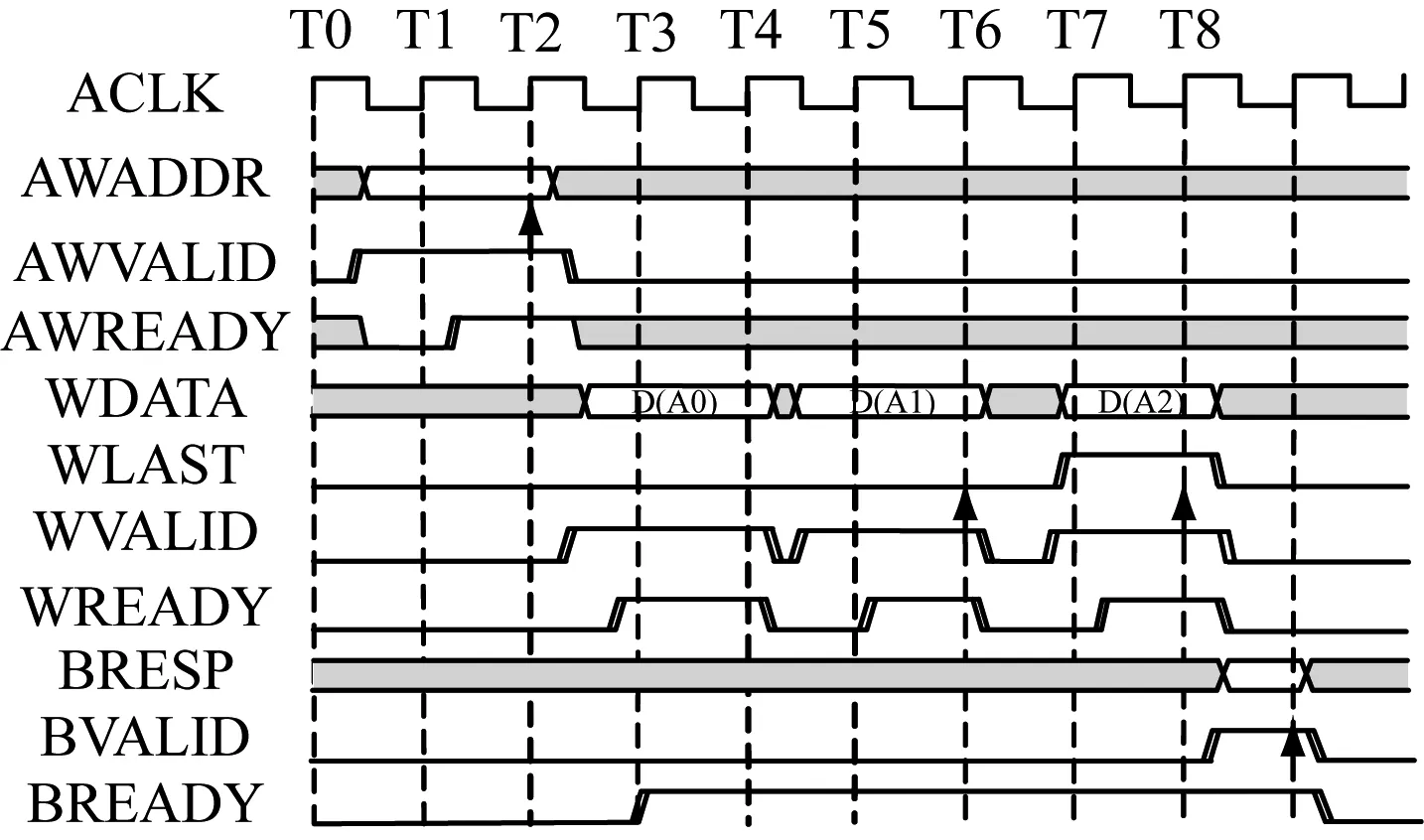

本文設計的片間總線協議基于BURST(突發)模式,主機只給出突發傳輸的第一個字節的地址。從機必須計算突發傳輸后續的地址,同時突發模式傳輸不能跨4 KB邊界。其時序圖如圖4所示。

圖4 突發模式時序圖

在相應的箭頭所指示的位置進行地址和數據的寫入。其中讀寫地址使能、讀寫數據使能均在時鐘上升沿有效,數據傳輸在WLAST(寫完成信號)使能后完成,整個突發模式過程結束。對突發模式后續地址計算的參數如表1所示。

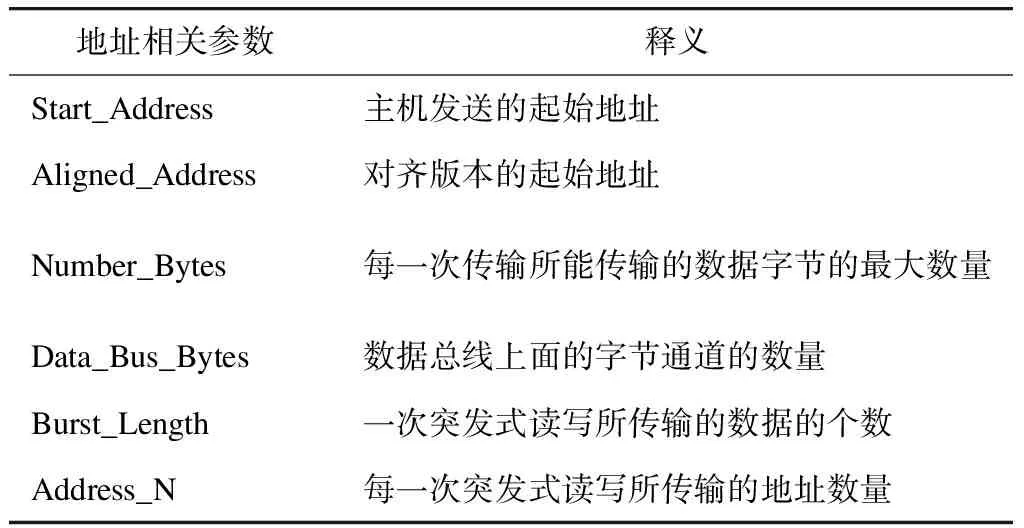

表1 突發模式計算相關參數

則有如下計算公式:

Start_Address=ADDR

Number_Bytes=2STZE

Aligned_Address=(INT(Start_Address/Number_Bytes))·Number_Bytes

Address_1=Start_Address

Address_N=Aligned_Address+(N-1)·Number_Bytes

已知ADDR = 0X0,SIZE=1,可計算出相應的Address_N =2 (N-1),以及每一次突發模式傳輸的地址偏移,并可以確認各個BURST讀寫的偏移地址從而完成整個突發模式的讀寫。

由于有突發模式邏輯以及有限狀態機的支持,每次傳輸的數據字節可以大大增多。由于每次傳輸的數據量呈指數增長,傳輸速率大大提高。

2 以太網高速通信的反射問題

網卡設計有高速DDR(雙倍速率)通路,且片間總線的通信速率在百兆左右,因此需要解決信號反射的問題,以保證片間總線高速通信的可靠性。

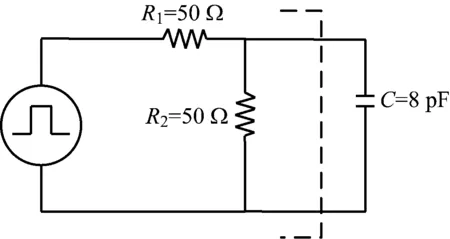

信號的反射一般以過沖以及振鈴的形式表現出來,其存在會大大影響通信的信號質量,嚴重時,可能會導致信號無法傳輸。信號的反射和互連線的阻抗密切相關,反射的本質就是互連線中的阻抗發生了變化。只要互連線中存在阻抗不連續的點,該處就會發生反射。由于任何接收器都會有一定的輸入電容,焊盤、封裝等都會引入一定量的寄生電容。輸入電容或者寄生電容就是容性阻抗不連續點,其到達接收器的時候就會產生相應的反射現象。不僅如此,容性負載還表現在類似于容性結構的負載,如芯片引腳較寬的焊盤、低速信號的過孔等都可以看做容性負載。例如本次設計的DDR電路,其采用的是樁線很短的菊花鏈拓撲結構,鏈路中的每一個接收器都相當于一個容性負載。其等效電路如圖5所示。

注:R——電阻;C——電容

該類的容性負載位于傳輸線中間,設計該網卡的傳輸線阻抗Z0都是50 Ω,因此信號到達電容時就相當于通過一個25 Ω電阻進行充電。設入射電壓最大值為U,則C兩端的電壓為:

(1)

式中:

t——信號到達電容的時間。

流過電容的電流IC為:

(2)

電容的阻抗Ze為:

(3)

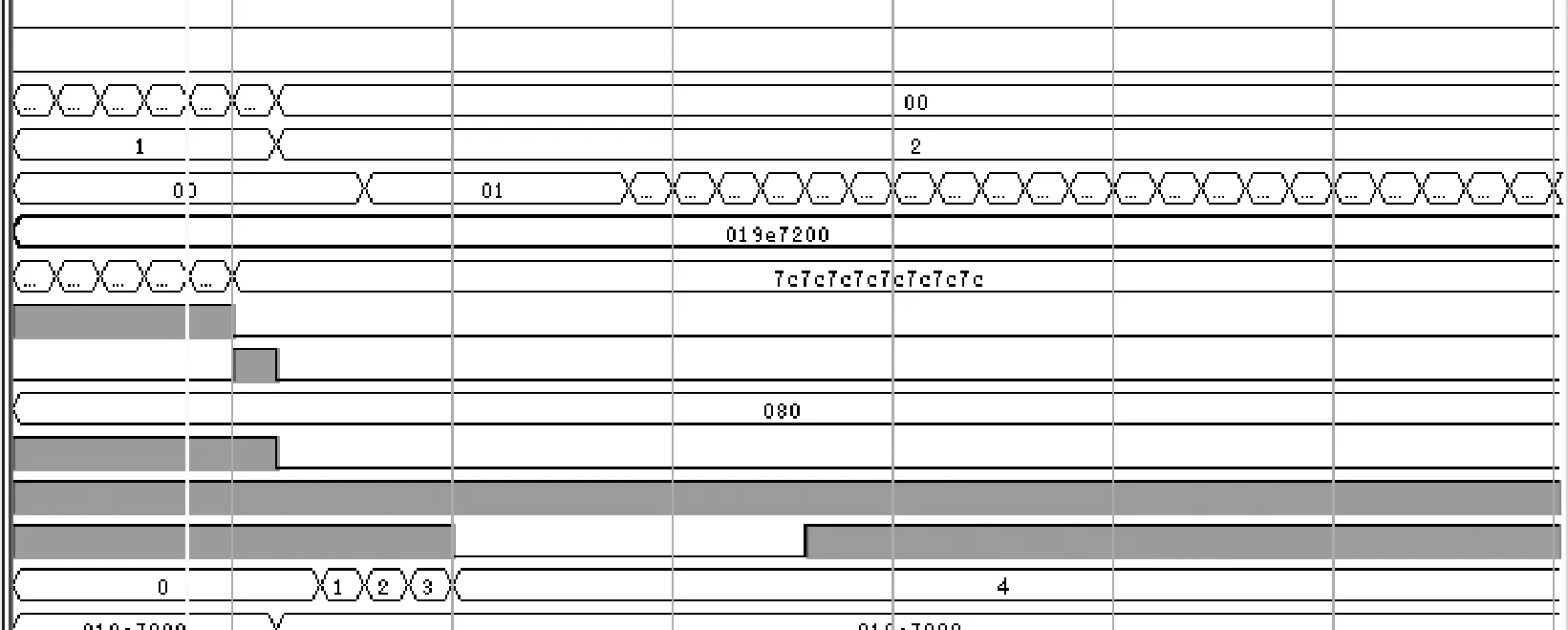

本文τ取0.2 ns。當t為1 ns時,信號到達電容并開始對電容充電。當τ為0.2 ns時,電容電壓上升到632 mV,該值是其終端電壓的63.2%。

由于信號傳播到電容時,感受到的阻抗是電容阻抗和后面一段傳輸線阻抗的并聯,并聯阻抗ZP為:

(4)

反射系數γ為:

(5)

如果設上升時間tr=0,則2 ns后容性負載的反射信號返回到發送端,反射、入射信號疊加口波形電壓下降到0;之后,信號的電壓按照指數的規律不斷增加,上升時間由τ決定。

接收端容性不連續會使得高低電平疊加一定的噪聲,信號到達接收端后由于接收端的高阻抗而發生反射,反射信號幅度與入射信號相同。反射信號到達中間電容時又會發生反射,電壓為負。信號就這樣在容性阻抗不連續點和其他阻抗不連續點之間不斷疊加,會產生很大的噪聲。

實際電路中不存在理想的傳輸線,也不可能完全匹配,因此信號反射是必然存在的。設計的關鍵在于如何把互連鏈路中的各個部件阻抗差距盡量縮小,從而減小反射信號幅度,避免多級反射對信號質量造成致命影響。實際電路中,在單端信號以及差分信號中做相應的阻抗匹配,例如單端信號按照50 Ω的阻抗匹配,差分信號按照100 Ω的阻抗匹配,從而使反射系數或者負載反射系數為0,以此來減弱或者消除信號的反射問題。同時,在實際電路中,1個驅動源驅動2個DDR芯片,且其拓撲結構采用的是菊花鏈拓撲,因此可采用串行端接的方式,在傳輸線源加33 Ω的端接電阻來抑制反射的增大。

3 TRDP的實現

3.1 TRDP

TRDP規定了TCN過程數據和消息數據在TCN中的通信流程。如圖6所示,以標準以太網協議棧為基礎,在傳輸層與應用層之間增加了TRDP層,能夠為TCN中任意兩個設備之間的過程數據和消息數據通信提供有安全性保障的端到端數據傳輸。與此同時,TRDP兼容標準以太網協議棧。

注:TCP——傳輸控制協議;UDP——用戶數據包協議

TRDP由過程數據PD接口、消息數據MD接口、精簡TRDP、虛擬操作系統VOS(軟交換)和實用程序等構成。過程數據接口處理TCN上的過程數據,消息數據接口處理TCN上的消息數據。其中高級PD/MD接口包括調度、線程,以及過程數據和消息數據的觸發等功能。實用程序部分包括數據的編組/解組、TRDP XML配置文件的讀取、IP/URI地址轉化、安全數據的傳輸,以及列車拓撲信息的訪問等功能。VOS提供了與不同操作系統的接口,上層的應用程序通過調用不同的接口實現不同操作系統下的通信功能。

3.2 過程數據通信流程

TRDP規定了過程數據和消息數據的幀格式、通信流程,并提供了相應的接口函數。本文以過程數據為例,對數據傳輸模式進行分析。

過程數據的通信包括推模式和拉模式,其中主要的通信角色包括發布者Publisher、請求者Requester和訂閱者Subscriber。

推模式是源端口按照固定的周期定時向訂閱者宿端口發送過程數據,源端口作為發送數據的發布者,宿端口作為接收數據的訂閱者,其通信方式如圖7所示。

圖7 推模式(一對多)通信方式

拉模式的工作模式為:由宿端口 sink 作為請求者并向作為廣播者的源端口發送請求消息,源端口收到來自宿端口的請求回復消息之后,立即將待發送的數據回復給宿端口,此時宿端口作為訂閱者,其通信方式如圖8所示。

圖8 拉模式(多對多)通信方式

Publisher作為數據的發送方,在推模式下循環發送過程數據PD,以及在拉模式下發送回復信息。同時在推模式下源端口按照固定周期定時向宿端口發送過程數據。Subscriber在拉模式和推模式中均為數據的訂閱者。

4 試驗測試與分析

本文設計的以太網卡硬件上使用賽靈思公司提供的ZYNQ系列芯片,型號為 XC7Z020-2CLG400I。該類型芯片采用FPGA+ARM架構,搭載雙核Cortex-A9應用處理器AMBA,互連內部存儲器、外部存儲器接口以及外設[4-5]。其中,ARM系統及外設主要有:片上只讀內存(Read-Only Memory,ROM)、256 kB片內隨機存儲內存(Random Access Memory,RAM)、2個千兆網卡以及片內ARM與FPGA之間的高帶寬連接。FPGA部分主要有:邏輯單元85 000個、查找表53 200個、觸發器106 400個以及JTAG(一種國際標準測試協議)調試接口1個。軟件采用linux 3.82操作系統,TRDP功能用C語言編程實現。

ZYNQ(可擴展處理平臺)下TRDP程序的編譯需要遵循以下步驟:

(1) 編寫測試程序,進行通信模式、通信量的配置。

(2) 編寫Makefile(文件編寫),定義編譯規則。

(3) 配置環境變量并設置編譯鏈。

本次測試是在2個嵌入式終端設備之間,進行一對一、點對點的 TRDP 過程數據通信測試。2個設備節點分別生成 28 個源端口,以及28個宿端口。本次測試中,數據幀內容包括本地IP、目的IP、數據發送周期以及數據長度,不同的端口通信周期設定為100 ms;數據長度設定為1 432 bit。

通過在TRDP以太網卡中產生相應的過程數據,將其存入DDR內存中的相應地址位置,同時在電腦終端顯示器上顯示過程數據發送的信息。利用邏輯分析儀,可以看到片間總線通過讀取DDR內存,將ARM中的過程數據傳入到FPGA,通過對比發送的過程數據,可以確認過程數據包發送的7C7C7C7C7C…在Chipscope(一款在線調試軟件)上抓取出來,如圖9所示。

圖9 過程數據波形圖

Wireshark是一個網絡封包分析軟件。Wireshark的功能是擷取網絡封包,并盡可能顯示出最為詳細的網絡封包資料。

以測試時100 ms下傳輸1 432 bit數據為例,單包數據傳輸速率設為13.98 kbit/s;通過Wireshark抓包軟件進行統計分析,可以得出在傳輸過程數據時數據包的接收速率近似為6 590個/s。這樣通過計算以太網每秒傳輸的包數乘以單包傳輸的bit數,最終就得出通信速率為94.36 Mbit/s。由于MVB(多功能車輛總線)、WTB(絞線式列車總線)、ARCNET(一種令牌總線網絡)等其他鐵路通信網絡速率均不高于10 Mbit/s,通過對比明顯看出基于TRDP下的數據通信速率遠遠高過MVB、WTB、ARCNET等鐵路通信網絡的的最高通信速率。

該測試狀態為網絡空閑時的狀態。但以太網網速受多種情況的影響[6-8],比如:①測試時使用的TCP通信協議,容易出現數據延遲、數據錯位以及數據丟失的問題;②網絡質量差會導致設備之間延遲過高,通信不穩定。所以,其網建不能完全達到100 Mbit/s,但是也基本可滿足列車通信速率的要求。

5 結語

本文結合FPGA與ARM,設計了符合鐵路通信標準的基于TRDP的以太網卡。通過提出一種片間總線技術,從軟件和硬件的角度入手,解決了以太網數據傳輸速率低的問題,有效保障了列車數據高速通信,為工業以太網應用于TCN又向前邁進一步。