高符號速率16APSK信號解調器的設計與實現

何朝玉,彭戰武

(1.中國電子科技集團公司第五十四研究所,河北 石家莊 050081;2.陸軍北京軍事代表局,北京 100012)

0 引言

隨著我國高分辨率遙感衛星的發展,遙感數傳速率需求已達3 Gbps,因此有必要進行超高速率的高速解調器研究。文獻[1]采用QPSK調制方式實現1 Gbps高速數據的傳輸,通過提高帶寬實現高速傳輸。文獻[2]采用16APSK調制方式,雙通道傳輸,實現2 Gbps高速數據的傳輸。相對于QPSK,16APSK調制方式在帶寬不變的情況下將傳輸速率提高1倍;雙通道傳輸節省了傳輸帶寬,但是需要2套接收設備。隨著V頻段等更高載波頻率的使用,很大程度上解決了傳輸系統的帶寬受限問題,高頻段功放器件的出現也解決了高階調制方式的傳輸功率問題,這都使高符號率高階調制方式的實現成為可能。

對于解調器的實現方式,一般有數字化中頻解調和模擬中頻解調。數字化中頻解調的采樣方式為中頻采樣,比模擬中頻解調節省了微波模塊,采樣后的信號正交性好,但軟件處理復雜度提高,且處理高速信號需要考慮AD采樣能力。

本文通過提高傳輸帶寬和采用16APSK高階調制方式,使傳輸速率達到3.72 Gbps,重點研究高速解調器的關鍵技術實現。

1 總體設計

遙感數傳高速解調器用于完成接收信號的解調同步和信號均衡等功能,本文接收信號的符號速率為930 MS/s,調制方式為16APSK,接收中頻為1.2 GHz。首先,在考慮工程實現的基礎上,綜合接收信號的速率、中頻、格式和幀結構等,制定合理的實現方案,實現信號的可靠接收。

1.1 信號模型

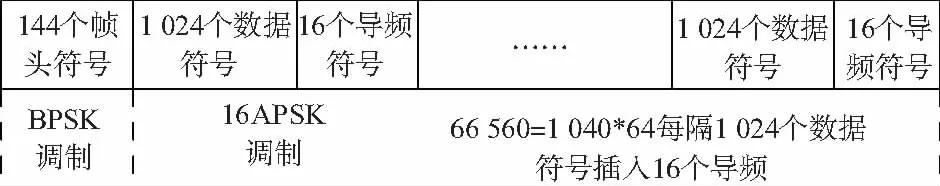

16APSK映射采用文獻[3]中的4-12APSK映射星座圖。接收數據幀由幀頭、導頻和數據符號組成,如圖1所示。幀頭符號為144個,可用于信號的頻偏估計[4],幀內分散插入64組導頻符號用于輔助同步處理,幀頭和導頻符號均為BPSK調制[5]。按以上設計的數據幀符號長度為66 704個,幀效率為98.24%。

圖1 幀結構示意

1.2 信號處理方案

目前,信號處理方案主要有2種:中頻采樣[6]和基帶采樣。2種方案對比,中頻采樣方案不需要模擬正交下變頻模塊,將中頻信號采樣后全部由FPGA處理,避免模擬器件帶來的IQ正交不平衡問題,且集成度高、靈活性高;但是在信號帶寬比較高時,為了避免采樣后信號出現混疊,要求采樣頻率很高,這對AD芯片采樣頻率指標提高了要求,此時AD芯片和FPGA的接口調試更加困難。采用基帶采樣的方案,AD采樣頻率大于等于2倍的符號速率即可[7],模擬器件帶來的IQ正交不平衡問題可以由FPGA內信號均衡模塊進行補償。

本文中接收信號中頻為1.2 GHz,符號速率為930 MS/s,采用中頻采樣時AD的采樣頻率最低為3 060 MHz,采用基帶采樣時采樣頻率為1 860 MHz即可。采用基帶采樣的方案可以降低對AD芯片的采樣頻率要求,且解調同步的算法實現簡單。

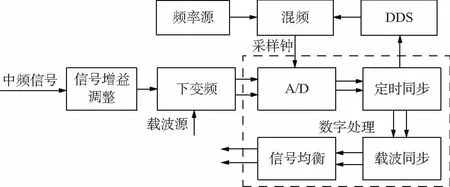

信號處理方案的框圖如圖2所示。中頻信號經過增益調整、下變頻[8]和AD采樣后送入FPGA內進行同步和信號均衡處理。

圖2 解調信號處理原理

經過下變頻后的信號,由于信道的影響,產生了嚴重的碼間串擾,采用矢量信號分析儀測試EVM[9]達到20%,接收信噪比很低,因此需要考慮在低信噪比條件下進行解調同步處理。

2 關鍵技術

2.1 時鐘同步

時鐘同步采用Gardner環[10]實現,AD芯片以2倍符號速率進行采樣,每符號采樣2次,在時鐘同步時,一次采樣在符號峰值點,另一次采樣在相鄰符號的過零點。此算法適合于數字實現,2倍采樣使運算量不會過大,且算法獨立于載波同步,定時同步可先于載波同步建立。

Gardner算法最初用于BPSK/QPSK[11]信號同步,文獻[12]證明Gardner算法與調制方式無關,因此Gardner算法適用于16APSK調制方式。Gardner算法提取出的誤差,經過環路濾波后控制DDS的頻率調整[13],DDS的輸出與固定的頻率源混頻后作為AD的采樣鐘。總的來看,由定時誤差控制AD采樣鐘的頻率調整從而實現定時同步。

2.2 載波同步

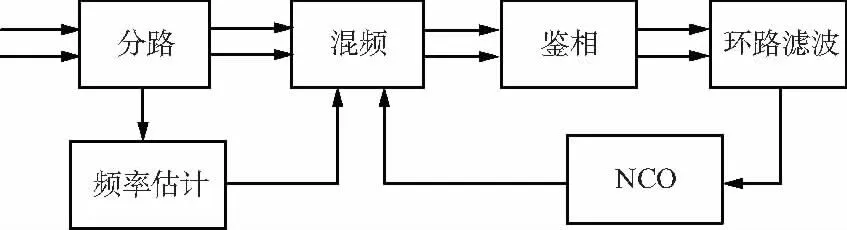

載波同步可以先利用已知的幀頭數據進行頻率估計[14]和補償,經過頻率補償后的數據仍然存在殘余的頻偏。殘余頻偏可以利用數據幀內插入的BPSK導頻,利用判決反饋環算法[15]進行跟蹤補償,實現接收信號低信噪比情況下的載波同步,實現框圖如圖3所示。

圖3 載波同步實現

假設信號經過理想定時同步,無碼間串擾,則存在頻偏和相偏的幀頭數據可以表示為:

rk=akej(2πΔfkT+θ)+nk,

(1)

(2)

(3)

估計分辨率由FFT運算的點數決定,在幀頭符號確定情況下,可以通過補0的方法提高FFT估計的分辨率[16]。

幀頭為144個符號,對其補0做8 192點的FFT變換,則其估計分辨率為1/8 192,進行頻偏補償后的歸一化殘余頻偏小于1/16 384,經過校頻之后,利用幀內插入的導頻,采用判決反饋環路對殘余的頻偏進行跟蹤補償[17]。

2.3 信號均衡

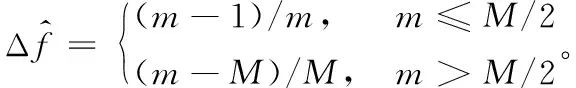

高符號速率信號在帶限信道中傳輸時,存在碼間串擾[18]現象,造成傳輸誤碼率的提高。碼間串擾主要來源于信號傳輸群時延不理想、傳輸信號幅度不平衡和下變頻模塊帶來的IQ不平衡。考慮信道的影響因素,本文采用基于最小均方誤差算法的線性均衡器,對同步后的信號進行均衡補償。為了消除IQ正交不平衡[19]的影響,在進行誤差運算時,將IQ兩路均衡后的數據同時引入誤差運算模塊與理想的星座點進行硬判決比較,實現框圖如圖4所示。

經過調試,濾波器采用33階FIR濾波器實現,濾波器的抽頭量化為16位,利用輸入信號和判決后的誤差控制濾波器的抽頭調整,實現自適應均衡。

圖4 均衡實現框圖

3 性能測試

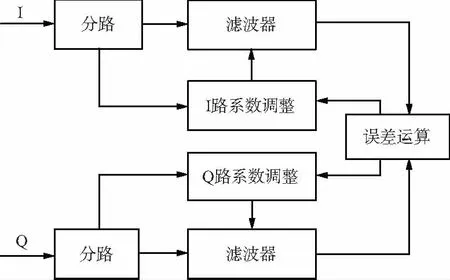

采用VHDL語言[20]對上述設計進行實現,并加載到硬件平臺。在L頻段,搭建測試環境對高速解調器進行誤碼率性能測試。設備測試框圖如圖5所示。任意波形發生器產生測試用的中頻信號,中頻1.2 GHz,符號速率930 MS/s,調制方式16APSK,通過調節寬帶噪聲源設置,施加不同強度的噪聲,經過高速解調器解調輸出后送誤碼儀測試,獲得不同信噪比下的誤碼率性能。解調性能測試結果如圖6所示。從測試性能曲線可以看出,在誤碼率為1×10-7時解調器的解調損失小于1 dB。

圖5 設備測試框圖

圖6 解調性能測試結果

4 結束語

本文在綜合分析信號模型和硬件實現難度的基礎上,設計了中頻模擬下變頻和基帶采樣的實現方案。此方案降低了對AD芯片采樣頻率的要求。由于碼間串擾造成接收信噪比降低,采用Gardner環實現時鐘同步;載波同步利用數據的幀頭和導頻,采用開環估計和閉環跟蹤實現載波同步,使解調器在接收信號惡化的情況下正常工作。采用最小均方誤差線性均衡器消除碼間串擾,提高誤碼率性能。經過測試,設計實現的高速解調器可以實現符號速率為930 MS/s的16APSK信號的解調,在誤碼率為1×10-7時解調損失小于1 dB,滿足實際工程需要。