片間高速圖像傳輸系統(tǒng)的設(shè)計與實現(xiàn)

任 強(qiáng),姚遠(yuǎn)程,秦明偉

(1.西南科技大學(xué)信息工程學(xué)院,四川 綿陽 621010;2.特殊環(huán)境機(jī)器人技術(shù)四川省重點實驗室,四川 綿陽 621010)

0 引言

隨著視覺測量技術(shù)的發(fā)展,高速工業(yè)相機(jī)以其高幀率和高分辨率,在工業(yè)生產(chǎn)中的應(yīng)用越來越廣,因此產(chǎn)生了大量的圖像數(shù)據(jù)。現(xiàn)場可編程門陣列(field programmable gate array,FPGA)作為一項越來越成熟的技術(shù),以其并行性以及靈活性,被廣泛應(yīng)用于圖像采集、傳輸以及處理[1-2]。在大型視覺測量和圖像處理系統(tǒng)中,常常需要多個FPGA協(xié)同工作,所以FPGA之間的圖像數(shù)據(jù)傳輸成為視覺測量和圖像處理系統(tǒng)發(fā)展的難點和瓶頸[3-4]。Xilinx目前提供了4種不同速率的高速串行收發(fā)器[5-7]。

針對在片間傳輸高速圖像數(shù)據(jù)和幀控制信號的問題,研發(fā)了一種高吞吐率、低錯誤率、高抗干擾能力、低I/O資源占用率的片間圖像數(shù)據(jù)傳輸解決方案。該解決方案可廣泛應(yīng)用于視覺測量系統(tǒng)和圖像處理系統(tǒng)。

1 GTH收發(fā)器

高速吉比特串行(GTH)收發(fā)器是吉比特收發(fā)器中的一種,是FPGA中高度可配置以及高度集成的可編程邏輯資源。GTH收發(fā)器具有很高的可擴(kuò)展性,可支持PCI-e、10GBASE-R、Aurora等多種協(xié)議[8]。GTH收發(fā)器支持500 Mbit/s~11.3 Gbit/s的線速率,支持8B/10B、64B/66B、64B/67B等多種線路編碼,支持時鐘矯正以及通道綁定等多種特性。Virtex-7 GTH收發(fā)器的TX發(fā)送端和RX接收端功能獨立,且均由物理媒介適配層(physical media attachment,PMA)和物理編碼子層(physical coding sublayer,PCS)組成。PMA內(nèi)部集成了高速串并轉(zhuǎn)換、預(yù)加重、接收均衡、時鐘發(fā)生器及時鐘恢復(fù)等功能電路。PCS內(nèi)部集成了8B/10B編解碼、彈性緩沖區(qū)、通道綁定和時鐘修正等專用電路模塊[5]。

2 Aurora協(xié)議

Aurora協(xié)議是由Xilinx公司提出的、開放的、免費的、輕量級的可配置數(shù)據(jù)鏈路層協(xié)議,主要用于在多個高速串行通道之間進(jìn)行點對點傳輸,具有高速數(shù)據(jù)傳輸和簡單易用的特點[9]。

Aurora協(xié)議可為私有上層協(xié)議或標(biāo)準(zhǔn)上層協(xié)議提供透明接口的串行互聯(lián)協(xié)議,允許任何數(shù)據(jù)分組通過Aurora協(xié)議封裝,并在芯片間、電路板間,甚至機(jī)箱之間傳輸。采用Aurora協(xié)議傳輸數(shù)據(jù)時,用戶數(shù)據(jù)在一個Aurora通道上傳輸,跨過通道通信的設(shè)備成為通道對。Aurora通道包含一個或多個Aurora鏈路,每個Aurora鏈路是一個全雙工或單工的串行數(shù)據(jù)連接,稱為“弄”。如果使用的是GTH收發(fā)器,這個“弄”可實現(xiàn)500 Mbit/s~11.3 Gbit/s的數(shù)據(jù)傳輸,最多可連接16個“弄”[5]。

Aurora通道具有如下特性。

①數(shù)據(jù)以幀的形式在通道中傳輸。

②幀和控制信息共享通道,控制信息包括流控信息、時鐘補(bǔ)償序列和空閑信息。

③高度可自定義的幀長度和幀格式。

④Aurora協(xié)議中的幀不必全部連續(xù),可以被流控信息和空閑信息打斷。

⑤支持8B/10B編碼和64B/66B編碼。

3 CXP圖像傳輸協(xié)議

CXP圖像傳輸協(xié)議在本文中是指128 bit數(shù)據(jù)位寬的圖像傳輸協(xié)議,其中包括了時鐘信號、128 bit的圖像數(shù)據(jù)信號、傳輸有效指示信號以及8 bit的幀控制信號。CXP協(xié)議信號定義如表1所示。

表1 CXP協(xié)議信號定義

4 片間圖像傳輸模塊設(shè)計

片間圖像傳輸模塊名稱為CXP_Transiver,模塊內(nèi)部集成了Xilinx提供的Aurora core。該模塊的特性如下。

①實現(xiàn)透明全雙工傳輸。

②支持最大吞吐率為32 Gbit/s,平均吞吐率為20 Gbit/s。

③實現(xiàn)鏈路的8B/10B編碼。

④可配置的鏈路線速率,單鏈路速率最高可達(dá)6.25 Gbit/s。

⑤用戶接口時鐘最大可支持250 MHz。

⑥可移植性強(qiáng),適用于多種收發(fā)器。

⑦可支持圖像數(shù)據(jù)位寬為32~128 bit。

4.1 模塊的架構(gòu)設(shè)計

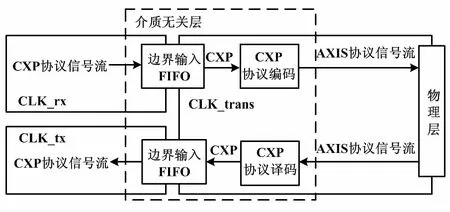

CXP_ transceiver模塊結(jié)構(gòu)如圖1所示。

圖1 CXP_ transceiver模塊結(jié)構(gòu)框圖

模塊分為兩層,分別是介質(zhì)無關(guān)層(media independent interface,MII)和物理層(physical layer,PHY)[5]。

介質(zhì)無關(guān)層將CXP協(xié)議信號轉(zhuǎn)換為AXIS協(xié)議信號。介質(zhì)無關(guān)層不考慮任何底層數(shù)據(jù)的傳輸方式問題,底層可以采用任何物理介質(zhì)進(jìn)行數(shù)據(jù)傳輸。

物理層為AXIS協(xié)議提供透明數(shù)據(jù)通路。物理層不考慮任何上層的數(shù)據(jù)內(nèi)容問題,僅采用高速串行接口為AXIS協(xié)議提供透明數(shù)據(jù)通路。

兩層組合共同完成了CXP協(xié)議的透明數(shù)據(jù)通路。兩層均采用模塊化設(shè)計,使用標(biāo)準(zhǔn)接口。

4.2 物理層設(shè)計

物理層功能由Aurora協(xié)議完成。Aurora協(xié)議由Xilinx公司提供的Aurora 8B/10B core實現(xiàn)。Aurora 8B/10B core可以自動地實例化最多16個GTH收發(fā)器通道、提供8B/10B的鏈路編碼、支持單工和全雙工的工作方式、支持16 bit和32 bit的循環(huán)冗余校驗并且可以在任意時刻暫停數(shù)據(jù)流傳輸。此外,Aurora 8B/10B core具有較低的資源消耗。

Aurora core主要參數(shù)配置如表2所示。

表2 Aurora core主要參數(shù)配置

Aurora 8B/10B core的主要功能模塊如下。

①Lane Logic。每個GTP、GTX或者GTH收發(fā)器都被Lane Logic模塊的實例化所驅(qū)動,每個收發(fā)器都會實例化一個Lane Logic模塊。該模塊處理控制字符的編碼和解碼以及錯誤校驗。

②Global Logic。Global Logic模塊完成了通道綁定和相位矯正。工作期間,該模塊將產(chǎn)生Aurora所需的隨機(jī)空閑字符,并監(jiān)控所有Lane Logic模塊的錯誤。

③RX User Interface。AXI4-Stream RX用戶端口將數(shù)據(jù)從高速收發(fā)器通道搬移到用戶接口,并實現(xiàn)流量控制。

④TX User Interface。AXI4-Stream TX用戶接口將數(shù)據(jù)從用戶接口搬移到高速收發(fā)器通道,并實現(xiàn)流量控制。此外,該模塊還控制周期性的時鐘補(bǔ)償序列的傳輸。

4.3 介質(zhì)無關(guān)層設(shè)計

介質(zhì)無關(guān)層結(jié)構(gòu)如圖2所示。

圖2 介質(zhì)無關(guān)層結(jié)構(gòu)圖

CXP協(xié)議包括了128 bit數(shù)據(jù)以及8 bit控制。為了便于物理層傳輸,介質(zhì)無關(guān)層需要將CXP協(xié)議信號封裝為128 bit的AXIS協(xié)議。在理想狀態(tài)下,CXP協(xié)議能夠滿速率運行,即128 bit數(shù)據(jù)持續(xù)有效。在這個情況下,在同樣頻率的時鐘下操作,無法將控制信號并入128 bit數(shù)據(jù)流。因此,介質(zhì)無關(guān)層內(nèi)部運行在比CLK_tx與CLK_rx更高頻率的CLK_trans上。各時鐘域間的信號傳輸以異步先進(jìn)先出(first in first out,FIFO)進(jìn)行隔離。

介質(zhì)無關(guān)層內(nèi)部的CXP協(xié)議編碼模塊(CXP_Encoding)及CXP協(xié)議譯碼模塊(CXP_Decoding)分別完成將CXP協(xié)議編碼為AXIS協(xié)議信號和將AXIS協(xié)議解碼為CXP協(xié)議。當(dāng)CXP協(xié)議中的控制信號為低電平時,輸入的CXP協(xié)議數(shù)據(jù)直接轉(zhuǎn)換為AXIS協(xié)議數(shù)據(jù)。當(dāng)CXP協(xié)議中有控制信號為高電平時,1個時鐘周期的CXP協(xié)議信號轉(zhuǎn)換為2個時鐘周期的AXIS協(xié)議數(shù)據(jù)。AXIS協(xié)議數(shù)據(jù)信號的第一個時鐘周期為控制信令,包含了CXP當(dāng)前的控制信號,與用于識別控制信號的標(biāo)記CMD_TAG,第二個時鐘周期的AXIS協(xié)議數(shù)據(jù)為CXP協(xié)議數(shù)據(jù)。

4.3.1 CXP邊界FIFO

CXP 邊界FIFO用于跨時鐘域傳輸CXP協(xié)議信號,在Xilinx IP Native FIFO上進(jìn)行了簡單的重封裝,以適應(yīng)CXP協(xié)議。CXP-FIFO模塊電路圖如圖3所示。

圖3 CXP-FIFO模塊電路圖

CXP協(xié)議的圖像數(shù)據(jù)信號和幀控制信號并行作為數(shù)據(jù)送入FIFO,讀取時從FIFO中并行取出。CXP-FIFO的Ready與Valid信號與CXP協(xié)議中的信號一致,可以直接連接至符合CXP協(xié)議的模塊。

4.3.2 CXP協(xié)議編碼電路

CXP協(xié)議編碼電路主要分為兩個部分,即DataTransform與ControlUnit。

CXP Encoding模塊電路如圖4所示。

圖4 CXP Encoding模塊電路

DataTransform主要完成將輸入數(shù)據(jù)轉(zhuǎn)換為輸出數(shù)據(jù),在內(nèi)部形成了以下三種數(shù)據(jù)。

①CXP協(xié)議中的圖像數(shù)據(jù)。

②低64位與CXP協(xié)議中的輸入數(shù)據(jù)的低64位相同,高64位為CMD_TAG-1。

③低8位為CXP的8 bit控制信號,第9位為是否轉(zhuǎn)義的指示信號,第10~64位為0,高64位為CMD_TAG。

DataTransform以Trans_meaning信號與cxp_event信號為指示,選擇其中一種數(shù)據(jù)。

Trans_meaning高電平有效,用于判斷當(dāng)前CXP輸入數(shù)據(jù)的高64位是否與預(yù)設(shè)的CMD_TAG一致。若與CMD_TAG一致,為避免接收端誤將該數(shù)據(jù)誤譯為控制信號,需要進(jìn)行轉(zhuǎn)義,將高64位減1,即CMD_TAG-1,即輸出數(shù)據(jù)類型(2)。Cxp_evnent高電平有效,指示了當(dāng)前CXP輸入是否有控制信號為高電平。當(dāng)有控制信號輸入時,Encoding模塊需要發(fā)出控制信號,即輸出數(shù)據(jù)類型(3)。在其他情況下,將會輸出數(shù)據(jù)類型(1)。

DataTransform中,Mapping的映射關(guān)系見上文提到的模塊數(shù)據(jù)結(jié)構(gòu)設(shè)計。Trans_meaning信號由Trans_Mean_Monitor模塊產(chǎn)生。該模塊是一個64 bit組合邏輯比較器。當(dāng)輸入的CXP協(xié)議信號中數(shù)據(jù)信號的高64位與CMD_TAG一致時,則輸出高電平,否則輸出低電平。

Control_Unit負(fù)責(zé)Encoding的時序控制,Control_Unit在CXP輸入控制信號中有高電平時,阻斷數(shù)據(jù)從CXP到AXIS的傳輸。當(dāng)CXP輸入控制信號都為低電平時,允許CXP與AXIS直接握手,直接將CXP數(shù)據(jù)傳輸至AXIS。

Event_Monitor是一個多輸入或門,當(dāng)sol、sop、eol和eop有信號為高時,輸出高電平,否則輸出低電平。Cmd_operation_done_n復(fù)位時為高電平,當(dāng)有控制信號為高時,Event_Monitor與Cmd_operation_done_n都為高電平,則cxp_event為1。Cxp_event取反后將rx_data_ready置0,阻斷了CXP協(xié)議信號的傳輸。當(dāng)檢測到本次控制幀傳輸完成后,Cmd_operation_done_n被置1,撤銷cxp_event。CXP協(xié)議端繼續(xù)向AXIS協(xié)議端傳輸數(shù)據(jù)。

4.3.3 CXP協(xié)議解碼電路

CXP協(xié)議解碼電路主要分為兩個部分,即DataTransform與ControlUnit。

CXP Decording模塊電路如圖5所示。

圖5 CXP Decoding模塊電路圖

CXP Decoding模塊主要分為Data Transform和Control Unit兩個部分。

DataTransform依據(jù)cxp_event信號進(jìn)行工作。當(dāng)cxp_event信號為高時,BUF讀取AXIS data的低9位信號;當(dāng)cxp_event為低時,BUF讀取0。BUF是一組受cxp_event控制的觸發(fā)器。

BUF的低8位輸出至Tx_control,最高位是轉(zhuǎn)義指示信號trans_meaning,控制MUX選擇是傳輸原數(shù)據(jù)還是將被轉(zhuǎn)義的原數(shù)據(jù)逆轉(zhuǎn)義。

Control Unit用于檢測AXIS協(xié)議端傳輸來的CMD控制信令。當(dāng)有控制信令時,cxp_event為高,控制BUF讀取控制信號,將Tx_data_valid拉低阻斷CXP信號輸出,將AXIS_data_ready信號拉高,允許讀取該控制信令。當(dāng)檢測當(dāng)前控制信令傳輸完成后,將cxp_event拉低,撤銷此次控制信令處理。

Control Unit中的Event Monitor是一個64位組合邏輯比較器,當(dāng)AXIS_data的高64位與CMD_TAG相等時,輸出高電平。

5 系統(tǒng)測試與分析

5.1 片間圖像數(shù)據(jù)傳輸系統(tǒng)架構(gòu)

在單個FPGA上仿真的片間圖像傳輸系統(tǒng)結(jié)構(gòu)如圖6所示。FPGA1和FPGA2為對稱的架構(gòu),在FPGA1和FPGA2之間是模擬的物理鏈路。FPGA1和FPGA2都有數(shù)據(jù)源CXP source、數(shù)據(jù)采集模塊CXP Endpoint以及數(shù)據(jù)對比模塊CXP Verifier。

圖6 片間圖像傳輸系統(tǒng)結(jié)構(gòu)圖

CXP Source用于產(chǎn)生符合CXP協(xié)議的信號,模擬了利用CXP Transceiver進(jìn)行傳輸?shù)腡x系統(tǒng)。為了保證仿真的科學(xué)性,CXP Source輸出的數(shù)據(jù)是由4個32 bit序列發(fā)生器生成的偽隨機(jī)數(shù)。產(chǎn)生的圖像的行場大小均為可配置參數(shù)。產(chǎn)生的valid信號有2種模式,由rand_valid信號控制。當(dāng)rand_valid信號為0時,輸出的valid信號恒為1;當(dāng)rand_valid信號為1時,輸出的valid信號為服從均勻分布的隨機(jī)數(shù)。該模塊還有一個trans_mean_valid控制信號。當(dāng)該信號為1時,CXP Source會周期性地產(chǎn)生需要被轉(zhuǎn)義的數(shù)據(jù)。該周期長度可參數(shù)化配置。

CXP Endpoint持續(xù)不斷地讀取CXP信號,模擬了利用CXP Transiver進(jìn)行傳輸?shù)腞x系統(tǒng)。CXP Endpoint簡單地將CXP_ready信號拉高,不斷讀取用戶接口端信號,并將其余信號使用“keep true”方式聲明,保證信號不在綜合時被優(yōu)化掉;此外,其未對輸入信號作任何處理。

CXP Verifier模塊用于監(jiān)聽兩個CXP信號線上的信號是否完全一致,以驗證CXP Transiver的傳輸正確性。CXP Verifier會將監(jiān)聽到的信號分別存入FIFO中。當(dāng)兩側(cè)FIFO都不為空時,將會取出數(shù)據(jù)進(jìn)行比較。傳輸異常指示信號定義如表3所示。信號反映了CXP Verifier模塊對數(shù)據(jù)傳輸情況的監(jiān)視結(jié)果。

表3 傳輸異常指示信號定義

5.2 仿真結(jié)果及分析

本次仿真測試的軟件平臺為Xilinx公司推出的ViVaDo 2016.4,仿真工具為ViVaDo自帶的仿真軟件Isim[9-11]。

FPGA1仿真結(jié)果表明,total_num一共發(fā)送了6 825個128 bit即873 600 bit數(shù)據(jù)。err_occur、overflow_occur、underflow_occur一直為低電平并且err_num、overflow_ num、underflow_ num這3個計數(shù)器一直為0,說明沒有邊界FIFO溢出和傳輸錯誤的情況出現(xiàn)。

FPGA2上的仿真結(jié)果與FPGA1相同,因為FPGA1

與FPGA2是完全對稱的結(jié)構(gòu),所以關(guān)于輸入輸出的圖像數(shù)據(jù)可參考FPGA1的仿真結(jié)果。total_num一共發(fā)送了873 600 bit數(shù)據(jù),err_occur、overflow_occur、underflow_occur一直為低電平并且err_num、overflow_ num、underflow_ num這三個計數(shù)器一直為0,說明沒有邊界FIFO溢出和傳輸錯誤的情況出現(xiàn)。

通過對兩片F(xiàn)PGA傳輸情況的仿真結(jié)果可知,該高速圖像傳輸模塊能夠正常工作,實現(xiàn)片間高速圖像數(shù)據(jù)的正確傳輸。輸入數(shù)據(jù)同步時鐘可達(dá)250 MHz,數(shù)據(jù)位寬可達(dá)128 bit,外加8 bit幀控制信號。

6 結(jié)束語

本文所設(shè)計的基于FPGA的片間高速圖像傳輸系統(tǒng),完成了片間的高速圖像數(shù)據(jù)傳輸。設(shè)計了圖像數(shù)據(jù)和幀控制信號的編解碼、跨時鐘域處理等電路,并對Aurora 8B/10B core進(jìn)行調(diào)用和封裝。系統(tǒng)實現(xiàn)了符合CXP協(xié)議的圖像數(shù)據(jù)傳輸,同步時鐘為250 MHz,圖像數(shù)據(jù)位寬為128 bit,幀控制信號為8 bit。系統(tǒng)提供了一種新的片間傳輸圖像數(shù)據(jù)的解決方案。因為底層傳輸由GTH收發(fā)器實現(xiàn),故該設(shè)計具有高抗干擾性,占用較少的I/O資源,提高了成本效益和圖像傳輸?shù)耐掏侣剩哂泻芨叩膶嵱脙r值。