一種帶有加解密功能的數(shù)據(jù)擺渡模塊設計

,,,

(南京南瑞集團公司,南京 211100)

引 言

在兩個不同安全防護等級網(wǎng)絡之間交換數(shù)據(jù)最常用的方法是使用網(wǎng)絡隔離裝置對數(shù)據(jù)以非網(wǎng)絡傳輸?shù)姆绞竭M行數(shù)據(jù)傳輸。傳統(tǒng)網(wǎng)絡隔離裝置的基本結構是兩個完全獨立的主機系統(tǒng)加一個數(shù)據(jù)擺渡模塊。為了進一步增加數(shù)據(jù)擺渡的安全性,目前新興的網(wǎng)絡隔離裝置的基本結構在傳統(tǒng)網(wǎng)絡隔離裝置的基礎上增強了加解密功能,首先對數(shù)據(jù)進行加解密處理,再對數(shù)據(jù)進行擺渡。網(wǎng)絡隔離裝置中數(shù)據(jù)加解密的性能和數(shù)據(jù)擺渡的性能直接決定了整個系統(tǒng)的性能。

現(xiàn)有的數(shù)據(jù)擺渡模塊一般有電子開關、單向FIFO、光纖和使用協(xié)處理器(FPGA等)擺渡數(shù)據(jù)4種方式,目前應用最廣泛的是使用協(xié)處理器的方式。對數(shù)據(jù)的加密功能則主要有在主機系統(tǒng)上通過軟件實現(xiàn)數(shù)據(jù)加密、分離的加解密模塊這兩種方式。

軟件實現(xiàn)的加密方式在安全性方面有隱患,且加解密性能對主機系統(tǒng)的性能有很大的依賴性。分離的加解密模塊一般做成一塊獨立的加密卡,加密卡上的核心器件主要包括協(xié)處理器和密碼芯片等,一般通過PCI/PCIe接口和主機進行數(shù)據(jù)交換,通過密碼芯片對數(shù)據(jù)進行加解密處理。

分離的加密模塊提高了系統(tǒng)的安全性,但與傳統(tǒng)的網(wǎng)絡隔離裝置相比,增加了分離加密模塊的隔離裝置,在數(shù)據(jù)擺渡之前首先要將數(shù)據(jù)通過PCI/PCIe接口寫入到加解密模塊進行加解密處理,加解密完成后的數(shù)據(jù)返回到主機系統(tǒng),主機系統(tǒng)再將加解密完成后的數(shù)據(jù)寫入到擺渡模塊進行數(shù)據(jù)擺渡,在性能上打了折扣,同時還要額外占用主機系統(tǒng)的一個PCI/PCIe接口和CPU資源,增加了硬件成本。

本文以XILINX公司的XC7A100T系列 FPGA為硬件平臺,利用FPGA的并行性[1]特點,設計了一款帶有加解密功能的高速數(shù)據(jù)擺渡模塊,在保證系統(tǒng)安全性的基礎上,提高了數(shù)據(jù)加解密和傳輸?shù)男阅埽瑫r降低了整個系統(tǒng)的硬件成本。

1 硬件方案設計

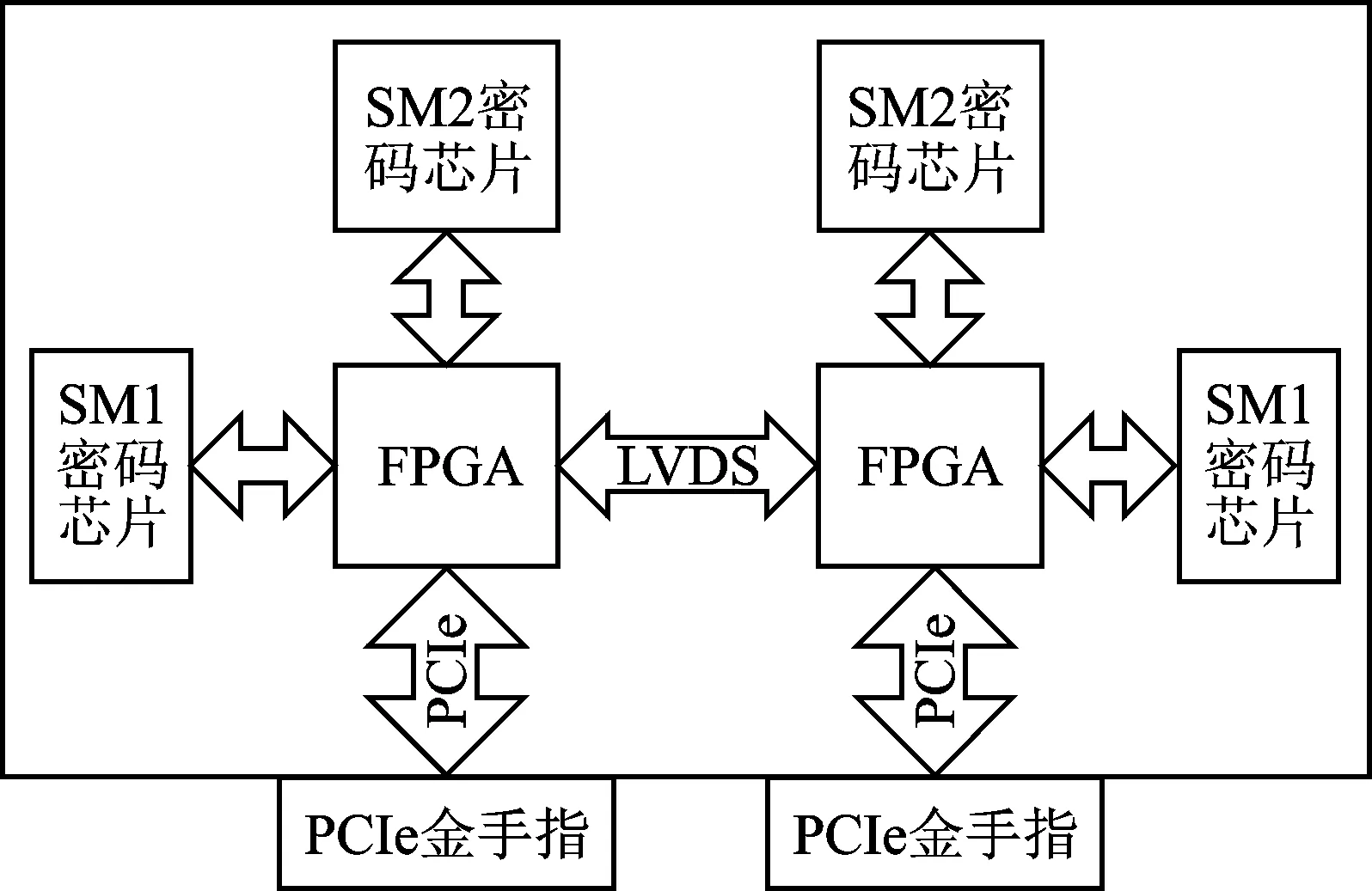

如圖1所示,本設計選用了兩片XILINX公司的XC7A100T FPGA芯片作為數(shù)據(jù)處理核心,數(shù)據(jù)擺渡模塊與主板之間采用PCIe接口通信。XC7A100T FPGA芯片該最多支持一個PCIe x4 Lane核,每個Lane線速為5 Gbps。

為了提高數(shù)據(jù)傳輸速率,降低擺渡模塊PCB硬件設計的難度,擺渡模塊的兩塊FPGA之間通過FPGA I/O口自帶的SERDES資源實現(xiàn)的高速串行接口進行數(shù)據(jù)通信,與傳統(tǒng)的并行接口相比,利用FPGA內部SERDES資源實現(xiàn)的高速串行接口具有速度快、傳輸距離遠、占用芯片引腳少的優(yōu)點。此外還利用FPGA的并行性特點,采用流水線的方式處理數(shù)據(jù)包,進一步提高了數(shù)據(jù)處理的速度。

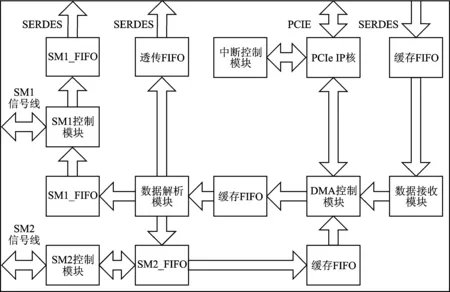

圖2 擺渡模塊FPGA邏輯架構框圖

為了滿足網(wǎng)絡隔離裝置對數(shù)據(jù)加解密性能的要求,本文設計的數(shù)據(jù)擺渡模塊選用了北京宏思電子技術有限責任公司公司的SSX30-D密碼芯片以及北京華大信安科技有限公司的IS32U320A密碼芯片作為數(shù)據(jù)加解密處理及身份認證、密鑰協(xié)商的核心模塊。

SSX30-D為高性能分組密碼算法芯片,實現(xiàn)了SM1(原名SCB2)密碼算法,性能最高為1.4 Gbps,在擺渡模塊中主要用作數(shù)據(jù)的加解密處理, IS32U320A芯片提供多種硬件協(xié)處理器及其配套安全算法庫,支持 RSA、SM2、SM3、SM4等密碼算法,在數(shù)據(jù)擺渡模塊中主要用作密鑰協(xié)商和身份認證。數(shù)據(jù)擺渡模塊硬件系統(tǒng)示意圖如圖1所示。

圖1 數(shù)據(jù)擺渡模塊硬件系統(tǒng)示意圖

在硬件電路設計上,F(xiàn)PGA芯片XC7A100T具有BGA484封裝,扇出的信號較多,此外還需要1 V、1.2 V、1.8 V、3.3 V等多種電平標準,PCIe接口的差分對走線對PCIe信號的完整性要求較高。基于以上因素,本文設計的數(shù)據(jù)擺渡模塊采用了8層PCB板設計方案,從頂層到底層依次為信號層1、地平面1、信號層2、地平面2、信號層3、電源層1、電源層2、信號層4;同時對PCIE的差分對信號以及SSX30-D的數(shù)據(jù)總線做了等長處理。

2 數(shù)據(jù)擺渡模塊程序設計

2.1 FPGA內邏輯電路設計

本設計使用XILINX公司的Vivado軟件開發(fā)擺渡模塊FPGA器件的邏輯程序,F(xiàn)PGA內邏輯程序設計主要包括:PCIe IP核的定制設計、DMA控制器的設計、數(shù)據(jù)解析模塊的設計、SSX30-D密碼芯片控制模塊的設計、IS32U320A密碼芯片控制模塊的設計、數(shù)據(jù)接收模塊的設計、中斷控制模塊的設計等,F(xiàn)PGA內邏輯架構框圖如圖2所示。

在PCIe數(shù)據(jù)通信中,有兩種數(shù)據(jù)傳輸方式: DMA(Direct Memory Access)和PIO(Programmed Input-Output)[3]。在DMA模式下,數(shù)據(jù)傳送不是由CPU負責處理,而是由一個特殊的處理器DMA控制器來完成,因此占用極少的CPU資源。在PIO模式下,數(shù)據(jù)傳送由CPU執(zhí)行I/O端口指令來按照字節(jié)或更大的數(shù)據(jù)單位來處理,占用大量的CPU資源,數(shù)據(jù)傳輸速度也大大低于DMA模式[4]。

本設計采用兩者相結合的方式,在DMA控制器中兼容了PIO控制器,通過PIO控制器將主機系統(tǒng)內存中DMA[2]讀寫的起始地址寫入PCIe BAR空間, DMA控制器根據(jù)BAR空間中的地址主機系統(tǒng)內存中的數(shù)據(jù)讀入到FPGA中的FIFO中緩存,再將FPGA處理完成的數(shù)據(jù)寫入到主機系統(tǒng)內存中。

方:您在從事分編工作數(shù)年后又改換為情報檢索服務工作,并且發(fā)表了不少相關研究成果。您能簡要介紹一下其中發(fā)生轉變的情況嗎?

數(shù)據(jù)解析模塊主要將FIFO中緩存的數(shù)據(jù)進行解析,并根據(jù)包頭字段定義的格式將數(shù)據(jù)包分別寫入到不同的下級FIFO中緩存,下級FIFO主要包括明文透傳FIFO、SM1緩存FIFO、SM2緩存FIFO三種,明文透傳FIFO中緩存的數(shù)據(jù)包直接通過FPGA內的SERDES接口傳輸?shù)搅硗庖粔KFPGA;SM1緩存FIFO中緩存的數(shù)據(jù)包在SSX30-D密碼芯片控制模塊的控制下,寫入到SSX30-D密碼芯片進行加解密處理,處理完成后的數(shù)據(jù)包再通過FPGA內的SERDES接口傳輸?shù)搅硗庖粔KFPGA;SM2緩存FIFO中的數(shù)據(jù)包在IS32U320A密碼芯片控制模塊下寫入到IS32U320A芯片內部進行處理,處理完成后的數(shù)據(jù)返回到FPGA并通過DMA控制器寫入到主機系統(tǒng)內存中。

數(shù)據(jù)接收模塊主要負責接收另外一塊FPGA傳輸過來的數(shù)據(jù),并寫入到接收FIFO中緩存,DMA控制器讀取接收FIFO中的數(shù)據(jù)并通過PCIe接口寫入到主機系統(tǒng)內存中。

中斷控制模塊主要負責發(fā)送中斷到主機系統(tǒng),通知主機系統(tǒng)讀取數(shù)據(jù),PCIe設備的中斷方式主要有傳統(tǒng)中斷、MSI中斷兩種方式[5]。傳統(tǒng)中斷為電平觸發(fā),MSI中斷為邊沿觸發(fā),一個PCIe設備最多支持4個傳統(tǒng)中斷,MSI中斷方式最多可以達到32個。本設計使用MSI中斷方式,并能根據(jù)主機系統(tǒng)的CPU核個數(shù)動態(tài)調整中斷數(shù)目,在每個CPU的核上綁定一個MSI中斷,使得CPU資源的使用更加均勻。

2.2 數(shù)據(jù)擺渡模塊驅動程序設計

網(wǎng)絡隔離裝置的系統(tǒng)一般為Linux,數(shù)據(jù)擺渡模塊的Linux驅動程序的核心是DMA部分的設計。本設計的DMA部分在借鑒了PCIe網(wǎng)卡的驅動架構基礎上設計了更適合自己的一套DMA架構。首先在驅動程序的初始化模塊(probe)中申請兩塊DMA緩存區(qū),一塊作為發(fā)送描述符緩存區(qū),一塊作為接收描述符緩存區(qū)。兩塊緩存區(qū)中分別存放了數(shù)百個DMA描述符,并分別為每個描述符申請對應的數(shù)據(jù)DMA緩存區(qū)。描述符的結構體定義如下:

struct dma_desc {

u32 sa; //數(shù)據(jù)緩存區(qū)對應的源地址

u32 da; //數(shù)據(jù)緩存區(qū)對應的目的地址

u32 length; //數(shù)據(jù)緩存區(qū)中的數(shù)據(jù)長度

u32 status; //描述符的狀態(tài)

u32 next; //下一個描述符的地址

};

DMA分為兩個過程:數(shù)據(jù)從系統(tǒng)內存搬運到FPGA和數(shù)據(jù)從FPGA搬運到系統(tǒng)內存。數(shù)據(jù)從系統(tǒng)內存搬運到FPGA過程如下:用戶首先將數(shù)據(jù)寫入到發(fā)送描述符對應的數(shù)據(jù)緩存區(qū),并將數(shù)據(jù)的長度寫入描述符的length變量中,通過PIO模式將描述符的起始地址寫入到數(shù)據(jù)擺渡模塊FPGA內的PCIe BAR空間中。FPGA內的DMA控制器根據(jù)BAR空間中描述符的起始地址啟動DMA,將描述符讀入到FPGA,再根據(jù)描述符中的內容,將描述符對應的數(shù)據(jù)緩存區(qū)中的數(shù)據(jù)讀入到FPGA,最后通過DMA更新主機系統(tǒng)中描述符中的status狀態(tài)值。用戶通過status狀態(tài)值可確定DMA過程是否結束。

數(shù)據(jù)從FPGA搬運到系統(tǒng)內存的過程與之有所區(qū)別,驅動在加載時,將接收描述符緩存區(qū)的地址通過PIO模式寫入到BAR空間,F(xiàn)PGA中有數(shù)據(jù)待傳輸?shù)街鳈C系統(tǒng)時,DMA控制器首先根據(jù)BAR空間中接收描述符的地址將描述符讀入到FPGA,并根據(jù)描述符中的內容將數(shù)據(jù)傳輸?shù)街鳈C系統(tǒng)中描述符對應的數(shù)據(jù)緩存區(qū),并更新描述符中的status狀態(tài)值。最后通過中斷通知主機,主機接收到中斷后,通過描述符中的status狀態(tài)值判別哪些描述符對應的數(shù)據(jù)緩存區(qū)有數(shù)據(jù)可讀,將數(shù)據(jù)讀走后恢復描述符中的status狀態(tài)值。

3 實驗測試

3.1 實驗環(huán)境

為了突出實驗效果,對安裝了本擺渡模塊的網(wǎng)絡隔離裝置和安裝了分離的數(shù)據(jù)加密模塊的網(wǎng)絡隔離裝置分別進行測試。安裝本設計方案的網(wǎng)絡隔離裝置實物圖如圖3所示。安裝分離的加解密模塊的網(wǎng)絡隔離裝置如圖4所示。兩臺裝置系統(tǒng)主板軟硬件相同,CPU為Cavium Octeon III系列,主頻為2.4 GHz,操作系統(tǒng)為Linux,內核版本3.10。

圖3 安裝了本方案的網(wǎng)絡隔離裝置

圖4 安裝了分離加密模塊的網(wǎng)絡隔離裝置

3.2 數(shù)據(jù)測試

本擺渡模塊支持兩種數(shù)據(jù)擺渡方式:明文透傳和密文傳輸。明文透傳模式是指數(shù)據(jù)從一側的主機系統(tǒng)傳輸?shù)綌[渡模塊上的FPGA后不進行任何處理,直接通過SERDES接口傳輸?shù)搅硗庖粔KFPGA進而傳輸?shù)搅硪粋鹊闹鳈C系統(tǒng)。密文傳輸是指首先對報文進行加解密處理,再通過擺渡模塊傳輸?shù)搅硪粋鹊闹鳈C系統(tǒng)。

明文透傳數(shù)據(jù)時,單獨安裝分離加密模塊的網(wǎng)絡隔離裝置與應用本方案的網(wǎng)絡隔離裝置在數(shù)據(jù)傳輸路徑上相同。密文傳輸模式時,單獨安裝分離加密模塊的網(wǎng)絡隔離裝置首先要將數(shù)據(jù)寫入加密模塊進行加解密處理,處理完成后返回主機系統(tǒng),再寫入到擺渡模塊進行傳輸。

應用本方案的網(wǎng)絡隔離裝置首先將數(shù)據(jù)寫入擺渡模塊,經(jīng)過加解密處理后,直接進行傳輸,省去了數(shù)據(jù)返回主機及重新寫入擺渡模塊的過程。經(jīng)過測試,兩種方案的明文透傳性能一致,為1.5 Gbps;密文傳輸時,采用本方案的網(wǎng)絡隔離裝置傳輸速度為1.2 Gbps,采用分離加密模塊的網(wǎng)絡隔離裝置傳輸速度為800 Mbps。應用本設計的網(wǎng)絡隔離裝置在密文傳輸模式時,數(shù)據(jù)傳輸速度有明顯優(yōu)勢,且能節(jié)省硬件資源,提高CPU的資源利用率。

結 語

聶云杰、王元強(碩士),朱孟江、趙華(本科):主要研究方向為電力系統(tǒng)嵌入式設計。