一種BCD碼數/模轉換器的設計

華猛 黃偉軍 劉傳洋 吳晨輝

摘 要: 提出一種8421BCD碼輸入的CMOS數/模轉換器。數/模轉換器輸入采用8421BCD碼并行數字碼輸入方式,輸出采用模擬電壓輸出的方式,內部電阻網絡根據8421BCD碼特點進行特殊設計;鎖存電路采用時鐘控制,極大地抑制毛刺干擾。電路設計是基于0.35 μm CMOS工藝,經HSpice軟件和Cadence軟件仿真表明,電路工作在3.3 V電壓下,8421BCD碼數/模轉換器的積分非線性誤差(INL)最大為-0.48 LSB和微分非線性誤差(DNL)最大為-0.39 LSB,優值(FOM)最大為3.96,電路功耗為0.97 mW。

關鍵詞: 8421BCD碼; 數/模轉換器; CMOS; 內部電阻網絡; 時鐘控制; HSpice

中圖分類號: TN366?34; TP432 文獻標識碼: A 文章編號: 1004?373X(2018)16?0026?05

Abstract: A digital?to?analog converter of 8421BCD code input is proposed. For the digital?to?analog converter,the parallel digital code 8421BCD code is used as the input mode,analog voltage output is used as the output mode,and the internal resistance network is specially designed according to the characteristics of the 8421BCD code. Clock control is adopted for the latch circuit to greatly restrain glitch impulses. The circuit design is based on the 0.35 μm CMOS process. The results of the HSpice and Cadence software simulation show that the circuit works at 3.3 V voltage,the maximum integral non?linear (INL) error and differential non?linear (DNL) error of the 8421BCD digital?to?analog converter are –0.48 LSB and –0.39 LSB,the maximum figure of merit (FOM) is 3.96,and the power consumption of the circuit is 0.97 mW.

Keywords: 8421BCD code; digital?to?analog converter; CMOS; internal resistance network; clock control; HSpice

隨著電子技術的飛速發展,數字信號的使用越來越廣泛[1?2]。然而,自然界信號都是模擬信號,機器卻只能識別和發出數字信號,所以數/模轉換器在混合電路系統中起到關鍵作用,是連接數字信號與模擬信號的橋梁。當今電子時代有多種多樣的數/模轉換器[3],根據內部結構可分為加權電阻網絡DAC(Digital?to?Analog Converter)、R?2R倒T型電阻網絡DAC[4?5]、雙極性采樣電容DAC[6?7]和單值電流型網絡DAC等。比較經典的R?2R結構DAC,具有使用電阻種類少且數量少、結構簡單、工作速度快等特點[8]。但是現有的這些數/模轉換器結構都是采用二進制輸入的方式,然而在人們已經習慣了十進制數的使用,二進制位權由低到高依次為1,2,4,8,16,32,64,128 ……,這不便開發者解讀。8421BCD(Binary Coded Decimal)碼是人與機器的一個紐帶。8421BCD碼是將每一位的十進制數都用4位二進制數表示,且這4位二進制的位權依次是8,4,2,1。BCD碼已經廣泛用于各個領域,在計算機領域的應用中,既可保存數值的精確度,又可減少電腦做浮點運算時所耗費的時間。所以將BCD碼應用到DAC中是新的方向[9],不僅靈活簡便,還保留了二進制碼 0和1低誤碼率的優點。

二進制數轉化為十進制數的方法有多種,主要分為軟件轉化和硬件電路轉化[10?11]。軟件的實現方式又分DAA(Decimal Adjust after Addition)調節指令法和算法轉換法、查表法等,但是軟件轉化效率較低,占用資源多,耗時長[12?13]。硬件轉化法不占用內存資源但是卻存在硬件響應慢、成本大等問題。針對二進制的使用不便和當前所存在的數/模轉換器的不足,設計了BCD碼數/模轉換器,既能保留十進制的簡便性又可以直接控制數/模轉換電路。

1 BCD碼數/模轉換器內部電路設計

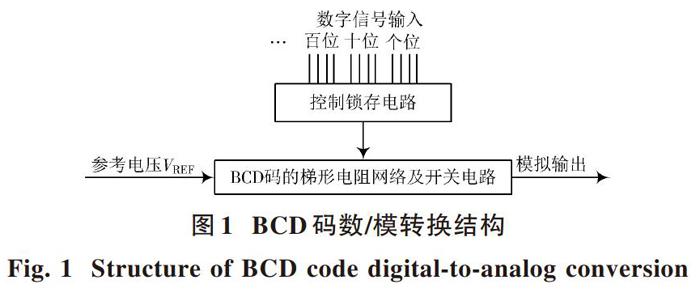

8421BCD碼的數/模轉換器是指輸入8421BCD碼,控制內部數/模混合電路,輸出對應的模擬信號,系統整體結構如圖1所示。數字信號以BCD碼的形式并行輸入,由鎖存電路進行鎖存,進而控制開關電路,形成不同阻抗的電阻網絡,最后形成對應的模擬輸出。

1.1 最小BCD碼阻抗單元

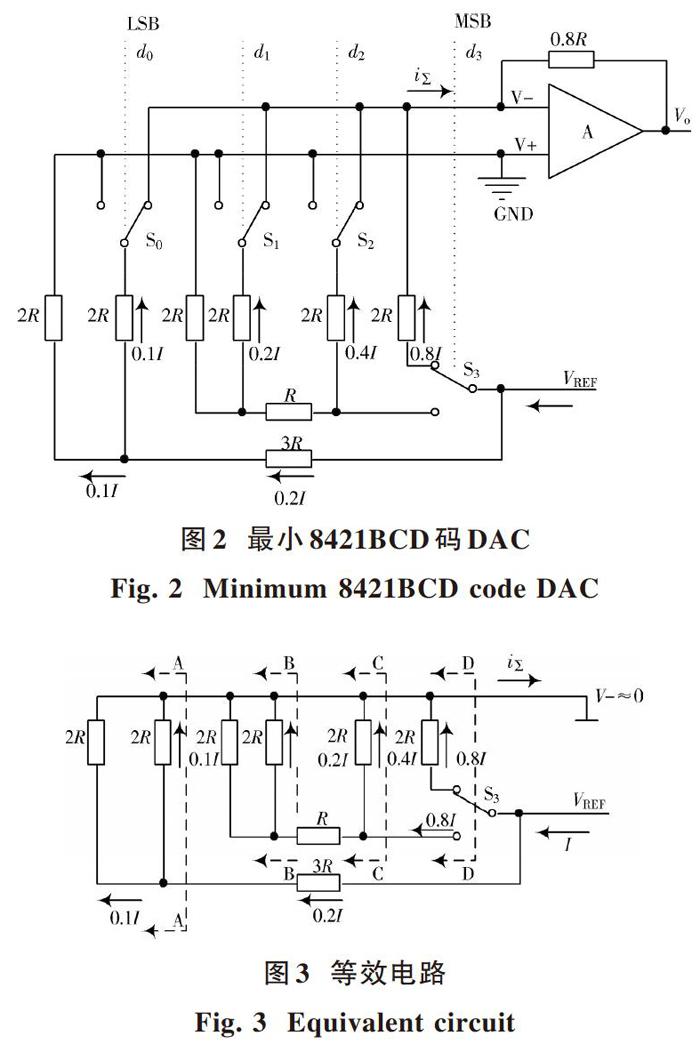

8421BCD碼是人們比較熟悉的十進制數的二進制編碼表示形式,十進制數的每一位都用四位二進制數表示,見表1,這不僅保留了十進制的簡便性還增加了對邏輯電路的靈活控制。圖2是最簡單的BCD碼數/模轉換器,也是最小的BCD碼數/模轉化單元。圖中d3,d2,d1,d0分別對應電子開關S3,S2,S1,S0。

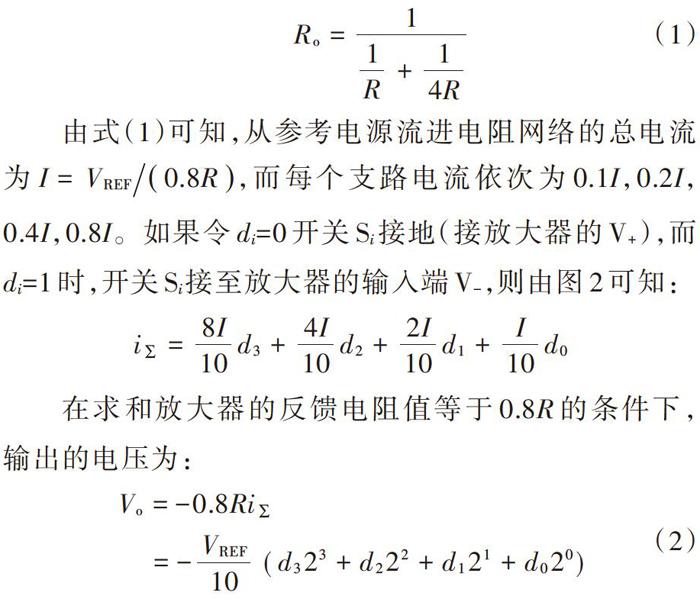

通過表1的8421BCD碼一覽表,觀察得知當最高位為邏輯正時,有且僅有最低位可以為邏輯正,所以對應圖2,當d3為1時,開關打到上面選通最大分流值,d2,d1只能為0;此時開關選通到地,電路中電流值為零。開關S3既可以控制最大分流支路,又避免輸入的不是BCD碼而導致模擬輸出過大的錯誤。根據虛短虛斷可知,求和放大器反相輸入端V-的電位始終接近于零,所以無論S2,S1,S0導通到任何一端,都相當于連接到了“地”電位上。由此可得等效電路如圖3所示。

圖3中AA端口的等效電阻為R,串聯上一個3R電阻,總電阻為4R; BB和CC端口的等效電阻都是為R;與DD端口的電阻相等。所以不論S3打到哪個支路,流進AA端口的電流與流進DD端口、CC端口的電流比為1∶4∶4。

分析圖3等效電路,可計算出VREF與地之間的阻抗為:

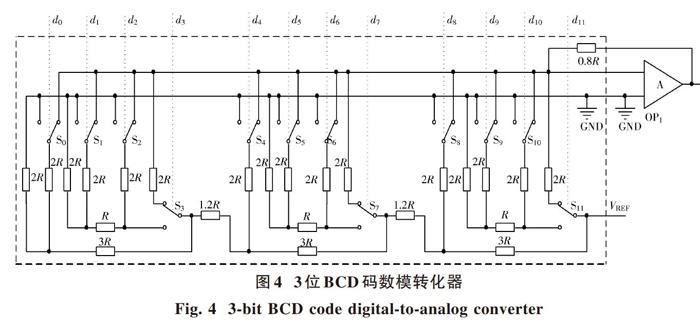

1.2 3位BCD碼數/模轉換電路

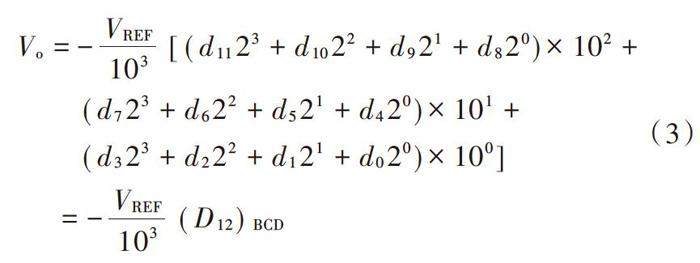

文中設計3位BCD碼數/模轉換器,電路圖如圖4所示,輸入BCD碼為(d11d10d9d8_d7d6d5d4_d3d2d1d0)BCD;每4位是一個BCD碼,用一級電路實現,當多位BCD碼時,由式(1)可知后級電阻網絡的總阻抗為0.8R,為保證多級擴展,需要在每級之間加一個1.2R匹配電阻。整個3位BCD碼數/模轉化器電路中,電阻網絡只有4種阻值的電阻,且只有26個電阻,與經典的12位R?2R倒T形電阻網絡數/模轉換器相比,電阻數量僅多兩個。因為輸入是十進制數,所以同等模擬開關數量下,精度相對經典的倒T形電阻網絡模/數轉換器稍差,但是用法簡便。在本電路設計中求和放大器的反饋電阻為0.8R,數/模轉換器輸出的模擬電壓的計算公式為:

由式(3)可得,輸出的模擬電壓與輸入的數字量成正比,滿足BCD碼輸入的要求。

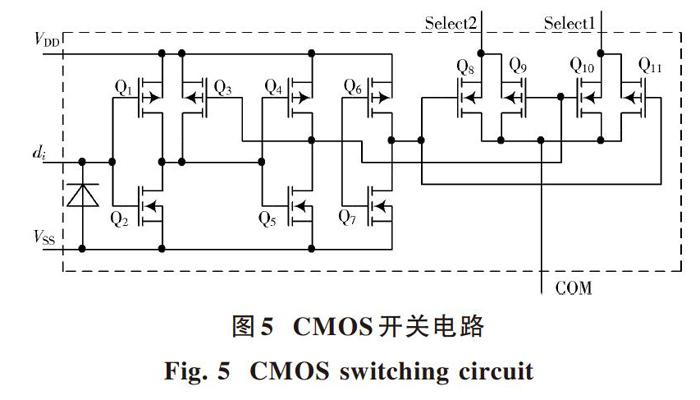

1.3 CMOS開關電路分析

開關電路采用的是CMOS開關電路。CMOS開關電路不僅制作成本低,而且占用面積小。圖5是CMOS開關電路,Q8,Q9構成一個傳輸門,Q10,Q11構成一個傳輸門。由di控制前級CMOS電路驅動兩個傳輸門,當di為高電平時選通Select1到COM,為低電平時選通Select2到COM端。

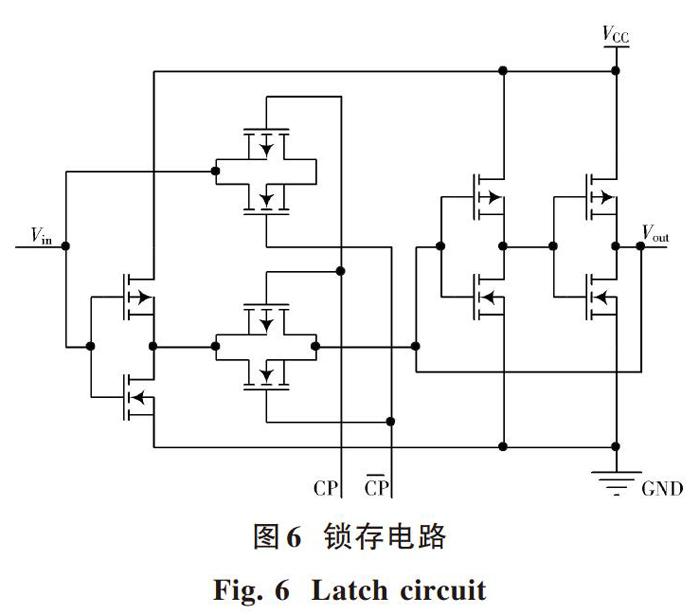

1.4 控制鎖存電路

控制鎖存電路主要是將輸入的邏輯信號存儲起來,使其BCD碼數/模轉換穩定輸出,減小毛刺干擾。控制鎖存電路主要由兩級反相器和兩個傳輸門組成,并且傳輸門由CP時鐘信號控制,實現對輸入數字信號的鎖存。如圖6所示是控制鎖存電路圖。

圖6中兩傳輸門由CP時鐘信號控制,當CP為低電平時,傳輸門導通,Vin可以傳輸到Vout,反之,CP為高電平時,傳輸門關閉,Vin無法傳輸到Vout。整個系統都由同一個時鐘控制,保證信號的同步性,極大地抑制電路由時延產生的毛刺現象。

2 仿真及結果分析

本設計采用HSpice軟件作為電路模擬仿真及結果分析的軟件工具。HSpice使電路級性能分析變得容易,具有良好的收斂性和精確的模型。HSpice不僅可以對集成電路進行交流分析、直流分析、瞬態分析,還可以對電路的性能進行多參數優化,具有多重仿真的AvanWaves 交互式波形圖分析等功能,是目前集成電路設計中比較簡便、快捷、效果顯著的一款模擬仿真軟件。

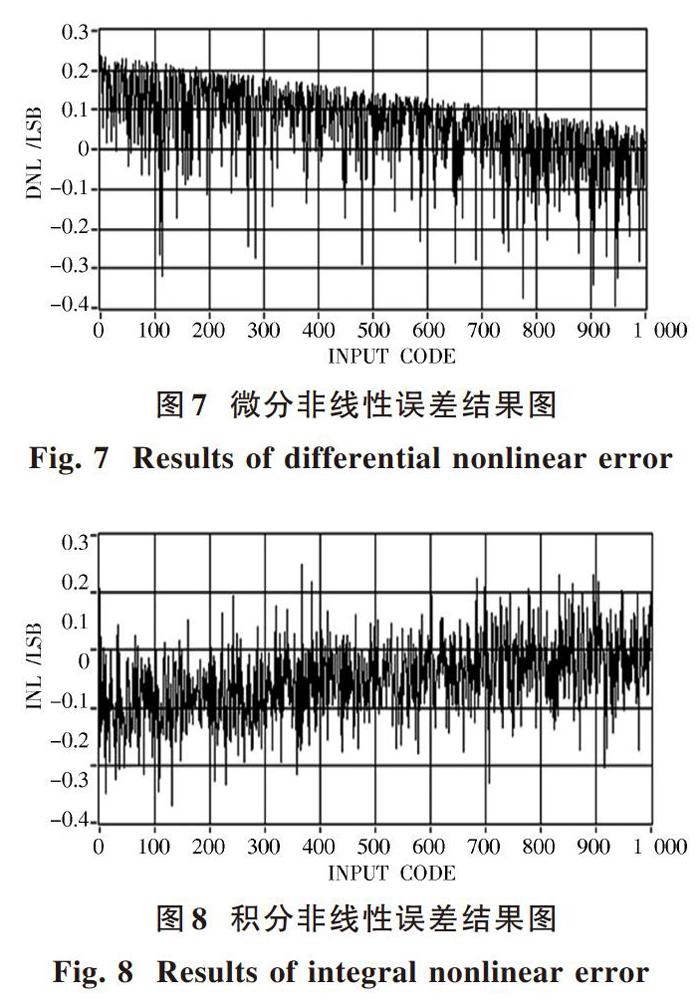

軟件仿真主要分析了數/模轉換器非常重要的性能。參數指標:微分非線性誤差DNL和積分非線性誤差INL。微分非線性誤差又稱為差分非線性誤差,是指數/模轉換器相鄰刻度之間最大差值,體現數/模轉換器的精度高低。積分非線性誤差是輸出值偏離線性理論值的最大距離,主要體現出數/模轉化器的線性度的優劣。圖7是用HSpice軟件仿真的微分非線性誤差結果圖,微分非線性誤差最大為-0.39 LSB。圖8是積分非線性誤差結果圖,積分誤差最大是-0.48 LSB。

圖9是電路采用0.35 μm CMOS工藝[14?16],根據Layout的設計規則,使用Cadence軟件做的3位BCD的DAC的版圖設計,版圖面積大約為0.093 mm2,符合版圖設計面積小的原則。

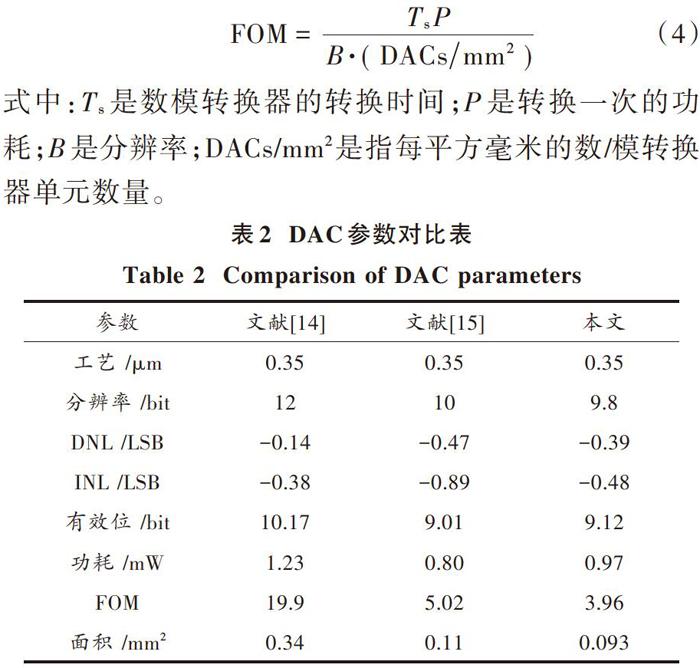

表2是本文設計的BCD碼DAC與近年所提出DAC的性能對比表,其中,優值(FOM)表示數/模轉換器在功耗、面積和分辨率之間的關系。FOM是衡量數/模轉換器優劣的重要參數,單位為J·bit-1·mm2,公式為:

由表2可得,本文設計的BCD碼數/模轉換器在縮小面積和功耗控制上具有一定優勢。

3 結 論

本文設計一種性能良好的BCD碼數/模轉換器,并采用HSpice模擬仿真電路進行仿真測試。仿真結果表明設計的BCD碼數/模轉換器正常工作的微分非線性誤差小于0.39 LSB,積分非線性誤差小于0.48 LSB,版圖面積大約0.093 mm2,供電為3.3 V時,轉換時鐘頻率為2 MSPs的情況下,功耗為0.97 mW,優值為3.96 J·bit-1·mm2。所設計的數/模轉換器內部阻抗網絡使用電阻少,電阻種類少,降低了制作難度。版圖面積較小,功耗性能好,并且編碼輸入3位8421BCD碼,充分發揮了8421BCD碼的操作簡便的優勢。總體上效果良好,設計滿足要求。

參考文獻

[1] XIE L,SU J,LIU J,et al. Energy?efficient capacitor?splitting DAC scheme with high accuracy for SAR ADCs [J]. Electronics letters,2015,51(6): 460?462.

[2] SEO D. A heterogeneous 16?bit DAC using a replica compensation [J]. IEEE transactions on circuits and systems I: regular papers,2008,55(6): 1455?1463.

[3] 蔡舟,張濤.一種不同縮放類型組合的低功耗DAC[J].微電子學,2016,46(6):726?730.

CAI Zhou, ZHANG Tao. A low power DAC with different scaling types of combination [J]. Microelectronics,2016,46(6): 726?730.

[4] MARCHE D,SAVARIA Y. Modeling R?2R segmented?ladder DACs [J]. IEEE transactions on circuits and systems I: regular papers,2010,57(1): 31?43.

[5] MARCHE D,SAVARIA Y,GAGNON Y. An improved switch compensation technique for inverted R?2R ladder DACs [J]. IEEE transactions on circuits & systems I: regular papers,2009,56(6): 1115?1124.

[6] 黃興發,趙建明,鄒錚賢.一種10 bit電流型DAC電流源晶體管的抗失配設計[J].現代電子技術,2006,29(8):110?112.

HUANG Xingfa,ZHAO Jianming,ZOU Zhengxian. A mismatching tolerant switching scheme for a 10?bit current?steering DAC [J]. Modern electronics technique, 2006, 29(8): 110?112.

[7] GADDAM R S,LEE K S,KWON C K. A 10?bit dual?plate sampling DAC with capacitor reuse on?chip reference voltage generator [J]. Microelectronics journal,2013,44(6): 511?518.

[8] 李婭,萬輝.一種新穎的R?2R電阻網絡[J].微電子學,2014,44(6):727?730.

LI Ya, WAN Hui. A new R?2R resistor network [J]. Microelectronics, 2014, 44(6): 727?730.

[9] 宋立雙.對8421BCD碼D/A轉換器的進一步認識[J].電測與儀表,1997(9):54.

SONG Lishuang. A further understanding of the 8421BCD code D/A converter [J]. Electrical measurement & instrumentation,1997(9): 54.

[10] 陳龍,樊曉椏.BCD碼和二進制碼轉換的硬件實現[J].微電子學與計算機,2005,22(4):42?44.

CHEN Long,FAN Xiaoya. Hardware converter between binary and BCD [J]. Microelectronics & computer, 2005, 22(4): 42?44.

[11] JUANG T B,CHIU Y M. Fast binary to BCD converters for decimal communications using new recoding circuits [C]// Proceedings of International Symposium on Integrated Circuits. Singapore: IEEE,2015: 188?191.

[12] BHATTACHARYA J,GUPTA A,SINGH A. A high performance binary TO BCD converter for decimal multiplication [C]// Proceedings of International Symposium on VLSI Design Automation and Test. Taiwan: IEEE,2010: 315?318.

[13] AL?KHALEEL O,AL?QUDAH Z,Al?KHALEEL M,et al. Fast and compact binary?to?BCD conversion circuits for decimal multiplication [C]// Proceedings of IEEE 29th International Conference on Computer Design. Amherst: IEEE,2011: 226?231.

[14] BAEK S Y,LEE J K,RYU S T. An 88?dB Max?SFDR 12?bit SAR ADC with speed?enhanced ADEC and dual registers [J]. IEEE transactions on circuits & systems II: express briefs,2013,60(9): 562?566.

[15] GADDAM R S,LEE K S,KWON C K. A 10?bit dual?plate sampling DAC with capacitor reuse on?chip reference voltage generator [J]. Microelectronics journal,2013,44(6): 511?518.

[16] LIOU C Y,HSIEH C C. A 2.4?to?5.2 fJ/conversion?step 10b 0.5?to?4 MS/s SAR ADC with charge?average switching DAC in 90 nm CMOS [C]// Proceedings of IEEE International Solid?State Circuits Conference Digest of Technical Papers. San Francisco: IEEE,2013: 280?281.