具有小步進和低相噪的頻率合成器的設計

蔣佳男 馬忠松

摘 要: 為了設計具有小步進和低相噪的頻率合成器,分析了直接式、鎖相式和直接數字式頻率合成器的優缺點,以及結合鎖相環與直接數字式頻率合成器的多種設計方案。在此基礎上,使用DDS激勵PLL的頻率合成技術,設計了滿足多種指標的頻率合成器。該合成器的步進是1 Hz,當頻率是10 kHz時,合成器的相位噪聲低于-90 dBc/Hz,同時其輸出帶寬較大。

關鍵詞: 頻率合成; 鎖相環; 低相噪; 小步進; 頻率合成器; 雜散

中圖分類號: TN73?34; TN74 文獻標識碼: A 文章編號: 1004?373X(2018)16?0009?04

Abstract: A frequency synthesizer with small step and low phase noise is designed by analyzing the advantages and disadvantages of direct, phase?locked and direct digital synthesizers, and combining multiple design schemes of phase?locked loop and direct digital synthesizers. On this basis, the frequency synthesis technology using DDS to stimulate PLL is adopted to design the frequency synthesizer that can satisfy various indicators. The step of the synthesizer is 1 Hz, and when the frequency is 10 kHz, the phase noise of the synthesizer is lower than -90 dBc/Hz, and the output bandwidth of the synthesizer is relatively large.

Keywords: frequency synthesis; phase?locked loop; low phase noise; small step; synthesizer; stray

0 引 言

在現代電子系統中,頻率合成器是通信、雷達和電子對抗等設備的重要組成部分,其輸出信號的穩定與準確程度直接影響通信、電子對抗等系統的整體性能[1?3]。所以,如何設計具有高穩定性和高準確度的頻率合成器始終是學術界研究的熱點內容。一般而言,頻率合成器是一種使用標準信號和多種技術手段生成大量離散頻率信號的電子設備,常用于微波掃頻中頻率參考信號的生成[4?6]。

根據頻率合成技術的實現方式,頻率合成器可分為直接式、鎖相式和直接數字式頻率合成器[7?10]。其中,直接式頻率合成器也被稱為分頻?混頻?倍頻式頻率合成器。此設備是使用晶體震蕩的信號產生目標頻率信號,該技術必須保持所有晶體的頻率穩定性和準確度,故生產成本較高。鎖相式(Phase Locked Loop,PLL)頻率合成器是通過比較晶體信號與振蕩電路信號的相位,再調整振蕩電路信號的相位,以減少兩種信號的相位差,從而盡量使振蕩電路信號的輸出頻率與晶體信號保持一致。鎖相式頻率合成技術出現于20世紀50年代,其優點是性能穩定,電路結構簡單,缺點是環路的響應時間較慢。直接數字式(Direct Digital Synthesizer,DDS)頻率合成器是直接使用抽樣和數字化等,數字計算技術產生合成頻率。該技術的優點是輸出信號相位是連續的,噪聲比較低,且設備的體積小,信號分辨率與轉換速度較高;缺點是輸出信號的雜散多,輸出頻率較窄。

基于這三種頻率合成器的研究背景,為了設計具有小步進、低相噪、低雜散和寬帶輸出的頻率合成器,本文綜合使用鎖相式(PLL)和直接數字式(DDS)頻率合成器,規避這兩種實現技術的缺點,最終設計與實現了兼具兩種優點的頻率合成器。

1 DDS+PLL頻率合成器

通過對DDS頻率合成器進行研究分析可知,其優點在于信號分辨率高,頻率轉換時間少;缺點在于信號的頻譜存在諸多雜散分量,從而導致信號的頻段難以滿足高頻輸出的要求。同樣,PLL頻率合成器的優點在于輸出頻率較高且頻譜純凈;缺點在于頻率轉換時間過長,即電路的響應僅可以達到微秒級。由頻率合成器的優缺點分析可知,DDS和PPL頻率合成器的優缺點是互補的,結合這兩種頻率合成器的設計可以得到一種混合使用的頻率合成器。該種頻率合成器兼具這兩種設備的優點,而不存在兩種頻率合成器的缺點。

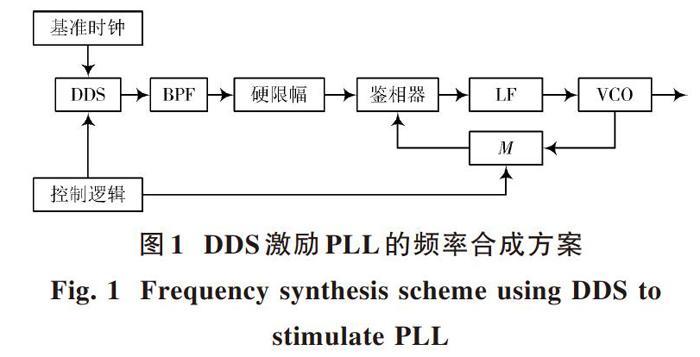

1.1 DDS激勵PLL的頻率合成技術

DDS激勵PLL的頻率合成技術是使用DDS和PLL混合方式的頻率合成器,常被用于寬帶雷達信號的生成過程。其電路結構見圖1。

由于帶通濾波器(BPF)和鑒相器之間有一個硬限幅電路,故該方案克服了DDS頻率合成器的雜散較小的缺點,其最終輸出結果是:

式中:[N]表示DDS的相位累加器位長;[K]表示DDS的頻率控制字;[fc]表示DDS參考時鐘的頻率。令[Mmin]表示PLL頻率合成器的最小分頻比,[f′]表示DDS頻率合成器的中心頻率,則該頻率合成器的帶寬為[BWDDS=f′Mmin]。

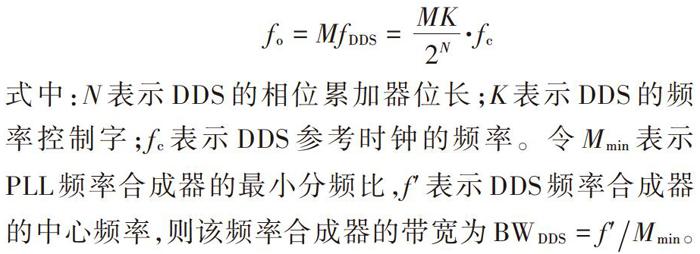

1.2 環外混頻的DDS+PLL頻率合成技術

在環外混頻的DDS+PLL頻率合成技術中,DDS和PLL頻率合成器是兩個獨立的電路結構。這兩個電路結構的信號由混頻器處理之后輸出,其電路結構如圖2所示。

該方案的頻率輸出結果是:

該方案實現了帶寬的連續覆蓋,其帶寬為[BWDDS≥fR]。

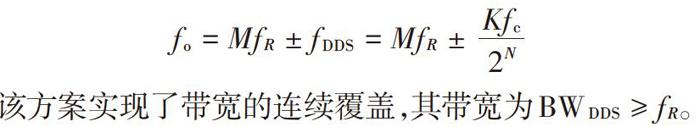

1.3 環內混頻的DDS+PLL頻率合成技術

該方案將混頻器加入了鎖相環的電路中,進一步優化了方案的頻率合成效率。其電路結構如圖3所示。

2 小步進低相噪低雜散頻率合成方案

在Ku波段的頻率合成方案設計過程中,其設計難點在于同時實現多項指標,這些指標包括輸出頻率的范圍為12.55~13.85 GHz;輸出功率的大小是12 dBm;頻率步進的大小為1 Hz;雜散小于-60 dBc;當信號頻率是10 Hz時,相位噪聲小于-70 dBc/Hz;當頻率是100 Hz時,相位噪聲小于-78 dBc/Hz;當頻率是1 kHz時,相位噪聲小于-84 dBc/Hz;當頻率是10 kHz時,相位噪聲小于-92 dBc/Hz;當頻率是100 kHz時,相位噪聲小于-100 dBc/Hz;輸入參考頻率的大小是10 MHz。為了設計達到多個參數的頻率合成器,本文使用了DDS激勵PLL的頻率合成技術。同時與PDRO進行混頻,得到了Ku波段的頻率輸出,完成了具有小步進和低相噪的頻率合成器的設計。

2.1 參考信號源的設計方案

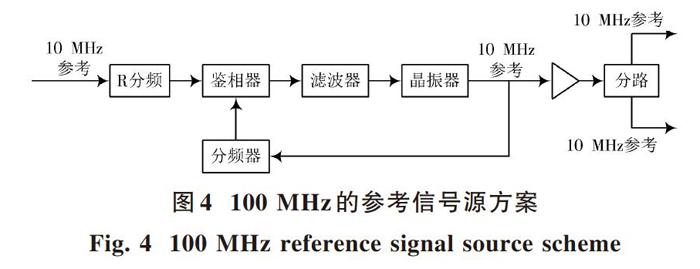

因系統的輸入參考頻率是10 MHz,且為了減小相位噪聲,本振鎖相環的參考源采用高鑒相頻率。本系統使用的鑒相頻率是100 MHz,故系統必須使用倍頻器將輸入的10 MHz放大到100 MHz,但此時相位噪聲的指標會惡化20 dB。為了降低這一指標,使用鎖相技術,由此既降低了相位噪聲,同時也提高了100 MHz晶體源的性能。

其實現框架如圖4所示。

2.2 本振的設計方案

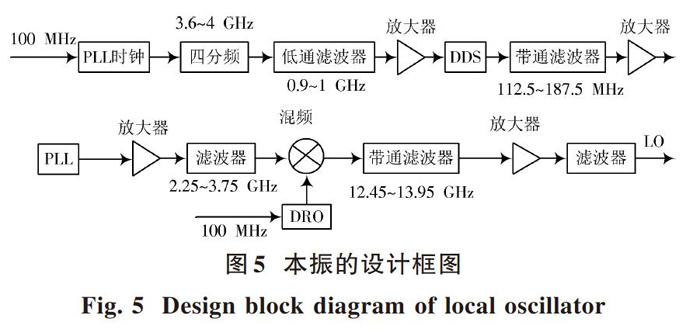

為了實現小步進的指標,該系統的本振一般會使用DDS或小數分頻鎖相環實現。因小數分頻鎖相環可以控制的最小步進單位是kHz,難以滿足本文的設計要求。所以,本系統的本振使用DDS技術實現1 Hz的頻率步進。此外,本文使用了鎖相式頻率合成技術,完成了1.5 GHz的寬帶輸出,其具體方法是利用寬帶壓控振蕩器輸出1.5 GHz的頻率。該方法的優點是電路實現相對簡單,可以將電路設備小型化;其缺點是該振蕩器的驅動只能使用有緣環路,而在該過程中會產生一些噪聲。由于本系統的模塊化和規范化的要求,文中使用了此方法進行寬帶輸出。

綜合上面分析的內容可知,系統的本振需要使用DDS+PLL的電路結構來實現。由上文的分析可知,3種實現方案均可滿足系統的步進和輸出頻點的設計要求。但由于環內與環外混頻的DDS+PLL頻率合成技術均無法輸出滿足系統要求的帶寬,故文中選用DDS激勵PLL的頻率合成技術作為本振的實現方案。需要指出的是,第1.1節介紹的頻率合成技術的輸出信號在倍頻的作用下,頻率達到Ku波段。在此過程中,信號的相位噪聲將大量增加,故本振的電路還需要加入變頻處理電路。在本文中,由于Ku波段的PDRO具有相位噪聲低的優點。所以,本振變頻選用了PDRO作為電路中的高頻段單頻點本振。在本振的設計方案中,DDS時鐘由獨立的PLL電路提供,PPL的輸出信號在四分頻的作用下輸入DDS。同時經過頻率為100 MHz分頻PLL的作用,提供了25 MHz的參考時鐘。該設計方案可以減少DDS的雜散指標,其具體實現框架如圖5所示。

3 性能分析

在完成頻率合成器的設計之后,文中還需要對該合成器的指標進行具體分析,確定該合成器是否達到設計要求。

3.1 步進分析

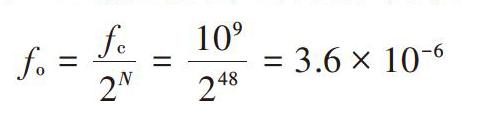

在本系統的設計中,頻率合成器的步進是1 Hz。在實際的系統中,DDS實現了這一功能。若參考時鐘的大小為1 GHz,則DDS輸出頻率的分辨率為:

這一結果意味著,即使PLL在進行40倍頻之后,該頻率分辨率仍可滿足系統的步進要求。

3.2 相位噪聲分析

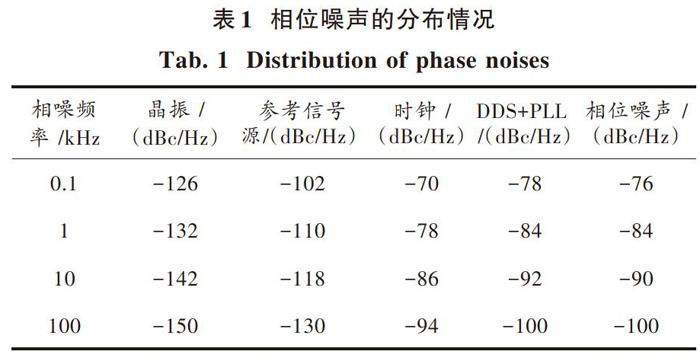

因本系統使用了DDS激勵PLL的頻率合成技術,故文中需要反推混頻器前輸入信號的相位噪聲。同時考慮倍頻所帶來的相位噪聲的惡化情況,再反推DDS輸出相位噪聲的情況。經過考慮參考時鐘、四分頻和鑒相器的多重作用之后,最終可得到系統的相位噪聲分配。鑒于文章的篇幅,其具體計算過程不再列出,計算結果見表1。

表中的最后一列就是該系統所達到的相位噪聲的計算結果,其完全滿足系統的設計要求。

4 結 語

隨著衛星通信研究的不斷深入,地面基站中Ku波段上變頻設備的設計受到廣泛的關注。本文基于Ku波段的變頻設備系統設計要求,對小步進和低相噪的頻率合成器進行深入的研究,并設計得到了滿足各種指標要求的Ku波段的頻率合成器。經過分析,該頻率合成器符合系統的設計要求,且具有較高的理論價值與實際意義。

參考文獻

[1] 周葉華,葉寶盛,程明,等.一種高頻譜純度的C頻段寬帶頻率合成器設計[J].電訊技術,2018,58(2):219?224.

ZHOU Yehua, YE Baosheng, CHENG Ming, et al. Design of a high spectral purity C?band frequency synthesizer [J]. Telecommunication engineering, 2018, 58(2): 219?224.

[2] 鄧迅,石玉,張鈺英.基于DDS的C波段寬帶小步進低相噪頻率源的設計與實現[J].磁性材料及器件,2018,49(1):43?46.

DENG Xun, SHI Yu, ZHANG Yuying. Design of C?band wide band small step and low phase noise frequency source based on DDS [J]. Journal of magnetic materials and devices, 2018, 49(1): 43?46.

[3] 張蘭,劉玉寶,吳國喬,等.基于HMC703的寬帶低相噪低雜散頻率合成器設計[J].現代電子技術,2014,37(1):93?95.

ZHANG Lan, LIU Yubao, WU Guoqiao, et al. Design of HMC703?based broadband frequency synthesizer with low phase noise and low spurious [J]. Modern electronics technique, 2014, 37(1): 93?95.

[4] 周彪,胡丹,李麗,等.S頻段小型化低相噪倍頻器設計[J].通訊世界,2017(15):13?14.

ZHOU Biao, HU Dan, LI Li, et al. Design of S?band miniature low phase noise frequency multiplier [J]. Telecom world, 2017(15): 13?14.

[5] 李海華.小步進、低相噪頻率合成器的設計與實現[D].武漢:華中科技大學,2016.

LI Haihua. Design and implementation of small step and low phase noise frequency synthesizer [D]. Wuhan: Huazhong University of Science and Technology, 2016.

[6] 錢淵源.基于AD9914的C波段頻率合成器的研究[D].南京:南京理工大學,2016.

QIAN Yuanyuan. Research on C band frequency synthesizer based on AD9914 [D]. Nanjing: Nanjing University of Science and Technology, 2016.

[7] 朱英超.基于微波介電陶瓷的X波段取樣鎖相介質振蕩器[D].成都:電子科技大學,2016.

ZHU Yingchao. X band sampling phase locked dielectric oscillator based on microwave dielectric ceramics [D]. Chengdu: University of Electronic Science and Technology of China, 2016.

[8] 郄錦輝,舒燕,王亞洲.低相噪低雜散C波段頻率合成器的設計[J].計算機與網絡,2011,37(10):48?50.

QIE Jinhui, SHU Yan, WANG Yazhou. Design on C?band frequency synthesizer with low phase noise and spur reduction [J]. Computer & network, 2011, 37(10): 48?50.

[9] 王川宇,潘碑,丁玉寧.X波段低相噪細步進頻率合成器的研制[J].固體電子學研究與進展,2014,34(1):56?59.

WANG Chuanyu, PAN Bei, DING Yuning. Development of X?band low phase noise and narrow resolution frequency synthesizer [J]. Research & progress of SSE, 2014, 34(1): 56?59.

[10] 虞洋華.寬帶低雜散S波段下變頻組件研究[D].南京:南京理工大學,2016.

YU Yanghua. Research on conversion module under broadband low spurious S band [D]. Nanjing: Nanjing University of Science and Technology, 2016.