一種應(yīng)用于CMOS圖像傳感器的流水線模數(shù)轉(zhuǎn)換器設(shè)計

陳 鳴,陳 杰,肖璟博

(1.中國科學(xué)院 微電子研究所,北京 100029;2.中國科學(xué)院大學(xué) 微電子學(xué)院,北京 100029)

0 引 言

CMOS圖像傳感器(CIS)[1,2]在消費類電子產(chǎn)品中的應(yīng)用日益廣泛,對CIS的面積和功耗要求也越來越苛刻。流水線模數(shù)轉(zhuǎn)換器(Pipeline ADC)能同時實現(xiàn)較高的速度和精度,因此在CIS中使用較多。傳統(tǒng)的流水線ADC[3]設(shè)計中,余量增益電路(MDAC)是基于閉環(huán)負反饋的開關(guān)電容電路來實現(xiàn)的,其中,跨導(dǎo)運算放大器(OTA)占了模擬域功耗的主要部分。因此,OTA的設(shè)計對整個ADC至關(guān)重要。隨著CMOS工藝的不斷發(fā)展,尤其當電源電壓降低到1 V以下時,傳統(tǒng)OTA結(jié)構(gòu)的性能已經(jīng)不能滿足低功耗的設(shè)計需求。

文獻[4-6]提出了一系列改進方案取代傳統(tǒng)OTA。其中Brooks等[4]提出的過零檢測(Zero-crossing detecting)技術(shù)應(yīng)用較多,但這種結(jié)構(gòu)對比較器的失調(diào)比較敏感,其控制電路較為復(fù)雜,難以實現(xiàn)高精度。Hershberg等[5]提出了一種全新的環(huán)形放大器(ing amplifier),然而,這種放大器對內(nèi)部失調(diào)電壓VOS比較敏感,VOS的變化可能導(dǎo)致環(huán)形放大器震蕩。Lim等[6]精簡了環(huán)形放大器的結(jié)構(gòu),采用電阻自偏置VOS,并使用高閾值器件,大大提高了環(huán)形放大器的魯棒性,但這種結(jié)構(gòu)的電源抑制特性較差,且單端工作時,系統(tǒng)的共模抑制能力以及偶次諧波失真都比全差分結(jié)構(gòu)差。為克服以上問題,本文提出了一種新型全差分環(huán)形放大器,并對所提出的結(jié)構(gòu)作了仿真,然后設(shè)計了一種10 bit 40 MS/s流水線ADC,驗證了本文的可行性。

1 環(huán)形放大器的工作原理

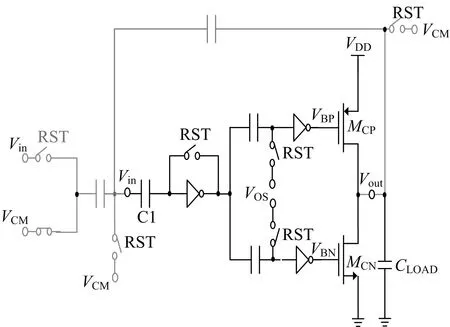

(a)傳統(tǒng)的環(huán)形放大器

(b)環(huán)形放大器的頻率響應(yīng)圖1 傳統(tǒng)環(huán)形放大器和頻率響應(yīng)Fig.1 Conventional ring amplifier and frequency response

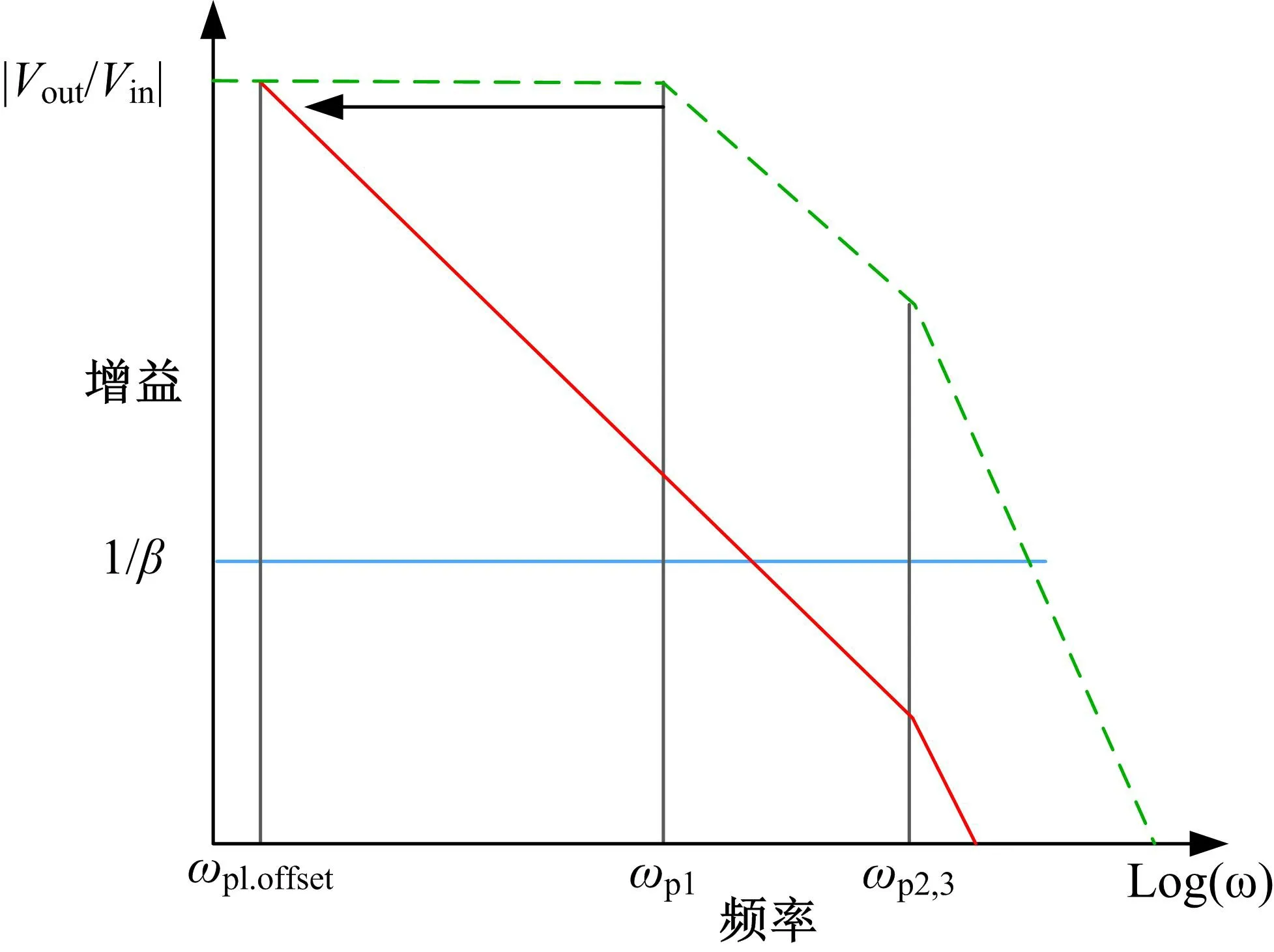

簡單的環(huán)形放大器結(jié)構(gòu)如圖1(a)所示,其頻率響應(yīng)如圖1(b)所示,當Vin接近VCM時,MCP和MCN會進入亞閾值區(qū),其輸出阻抗急劇增大而形成主極點,同時主極點和次主極點之間頻率間隔迅速增大,使系統(tǒng)的相位裕度也變大,從而系統(tǒng)趨于穩(wěn)定。由于放大器的輸出級工作在亞閾值區(qū),消耗電流極小,且輸出阻抗大,這使放大器的開環(huán)增益能達到80 dB以上,可滿足10~12位的精度要求;同時,由于充放電速度快,所以能滿足高速應(yīng)用。然而,這種放大器的工作強烈依賴于內(nèi)部失調(diào)電壓VOS,文獻[5]中VOS工作在50~100 mV。VOS過小,即VBP和VBN相差較小,MCP或MCN進入線性區(qū),輸出阻抗變小,主極點與次主極點頻率接近,放大器可能會出現(xiàn)阻尼震蕩;VOS過大,MCP或MCN可能會進入截止區(qū),則放大器的帶寬急劇降低,不能在指定的時間內(nèi)完成建立。當考慮PVT因素時,VOS可能超出正常工作范圍,放大器工作會變得異常。

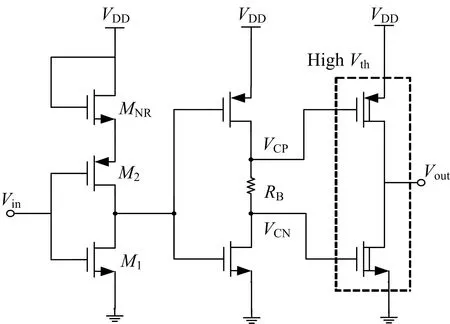

為解決圖1中的問題,同時擴大VBP和VBN的工作范圍,Lim等[6]給出了一種解決方案并簡化了放大器的結(jié)構(gòu)。如圖2所示,它在第二級反相器的輸出端引入了電阻RB,RB兩端的電壓差VOS(即VCPVCN)作為內(nèi)部失調(diào)電壓;同時,在輸出級引入了高閾值器件。由環(huán)形放大器的工作原理可知,只要VOS滿足:

VTHN+|VTHP|+VOS>VDD

(1)

則MCN和MCP工作在亞閾值區(qū),式中VTHN和VTHP分別為MCN和MCP的閾值電壓。由于采用了高閾值器件和自偏置VOS,VTHN和|VTHP|都較大,條件(1)更容易成立。因此,這種結(jié)構(gòu)能提高環(huán)形放大器的魯棒性;此外,高閾值器件的引入也提高了輸出阻抗,使環(huán)形放大器的開環(huán)增益得到進一步提升。MNR的引入是為了功耗和噪聲的折中。

圖2 文獻[5]中的環(huán)形放大器 Fig.2 Ring amplifier in literature [5]

盡管圖2中的結(jié)構(gòu)進一步優(yōu)化了環(huán)形放大器的穩(wěn)定性,但電源抑制和共模抑制能力依然較差。對于二極管接法的MNR,電源的擾動可直接作用到柵極,也會產(chǎn)生相同的擾動,因此,放大器對來自電源的擾動幾乎沒有抑制作用;其次,MNR上的壓降VGS較大,文獻[6]中采用65 nm工藝, PMOS的VGS的典型值約為0.35 V,對于1.2 V的電源電壓,輸入管的跨導(dǎo)和電流可較好的折中;但對于180 nm工藝,這個VGS的值約為0.7 V,要獲得同樣大小的跨導(dǎo),輸入管的尺寸會變得很大,而過大的尺寸會增加輸入寄生電容,進而對ADC的精度和速度造成影響,惡化放大器的性能。此外,電阻RB的引入雖然能產(chǎn)生內(nèi)部失調(diào)電壓,但集成電路中電阻的制作精度較差,其絕對誤差可以達到±20%,這會使圖2中的VOS變化較大,此時,輸出級可能會脫離亞閾值區(qū)而進入線性區(qū),環(huán)形放大器將不再正常工作。

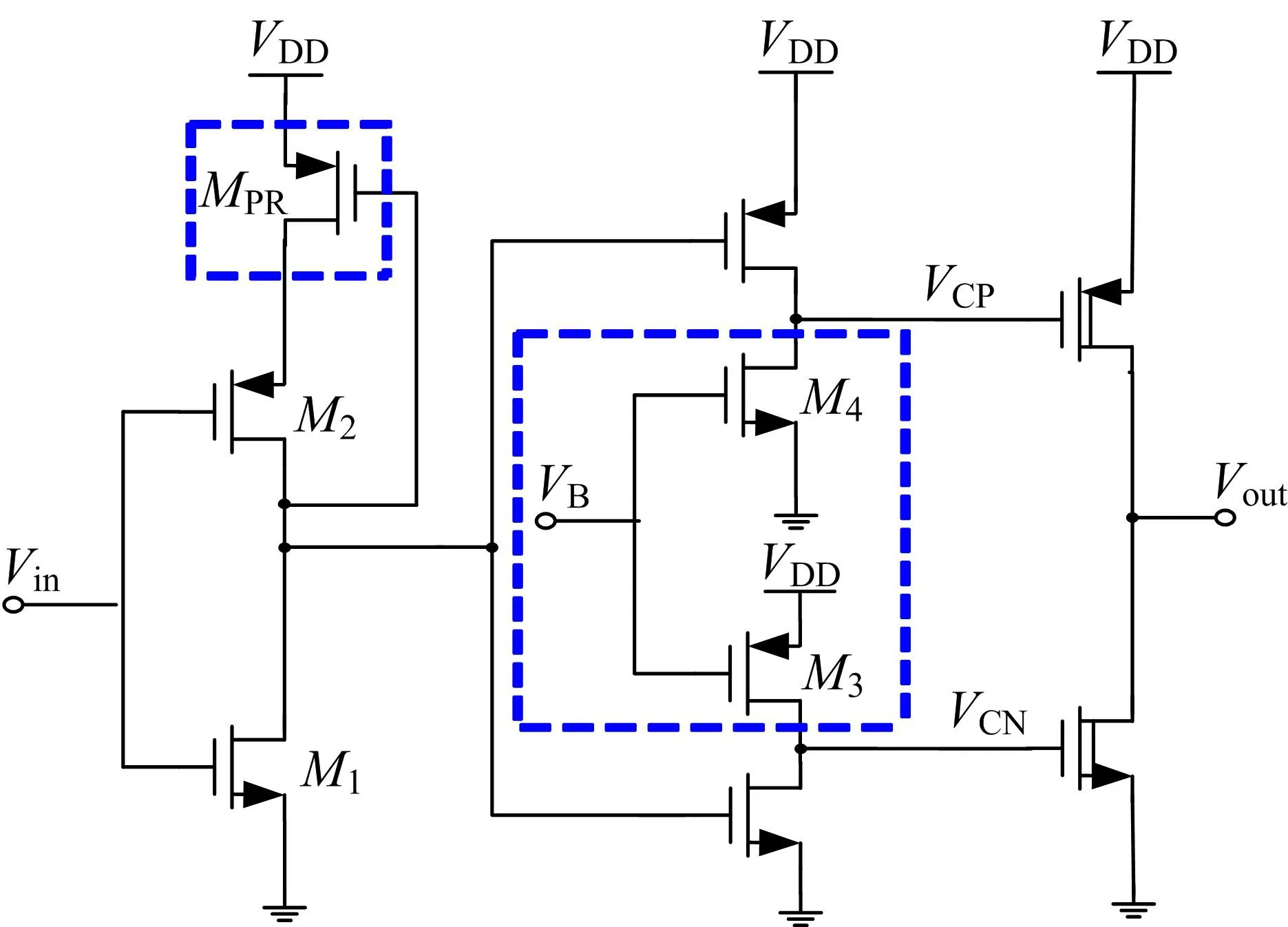

2 本文所提出的環(huán)形放大器

由圖2還可以看到,電源上的擾動不再直接作用于M2的源極,放大器對電源的擾動有一定的抑制作用,從而提高了第一級的電源抑制能力;更重要的是,由于MPR的負反饋作用,第一級反相器的輸出電壓更穩(wěn)定,提高了系統(tǒng)的共模抑制能力。MPR工作在線性區(qū),引入負反饋后,第一級反相器的等效跨導(dǎo)為:

(2)

式中:gm1、gm2分別為M1和M2的跨導(dǎo);go3為MPR的導(dǎo)納,go3的值和gm2的值近似相等。合理調(diào)節(jié)MPR的尺寸即可調(diào)節(jié)第一級反相器的電流和帶寬,從而優(yōu)化第一級反相器的速度和功耗。實際設(shè)計時,為了獲得更高的速度,M1和M2的寬長比(W/L)會盡可能大,考慮到PMOS的遷移率較大,一般取M2的尺寸為M1的3到4倍以使反相器的翻轉(zhuǎn)盡可能在中間電平。

原有的電阻RB被共源極接法的MOS管M3和M4取代,VB是它們的偏置電壓,本文直接取VB為放大器的輸出共模電壓VCM(0.5VDD)。放大器的第二級被劈裂成兩個共源放大器。這種結(jié)構(gòu)的好處是由MOS有源負載直接產(chǎn)生偏置電壓VCP和VCN,其內(nèi)部失調(diào)電壓VOS不再受集成電路中電阻制作工藝的影響。由于M3和M4單獨使用了偏置電壓VB,第一級的輸出節(jié)點并未增加額外的寄生電容,不會降低放大器的帶寬;此外,由于輸出級工作在亞閾值區(qū),VCN較小(接近于VTHN),VCP較大(接近于VDD-|VTHP|),因此,M3和M4的尺寸都較小,只有微弱的上拉和下拉能力,流過它們的電流也較小,滿足低功耗設(shè)計要求。為了降低第二級的電流,M3和M4的溝道寬度取為最小值220 nm,實際流過每個共源級的電流約30 A。第一級反相器的帶寬直接決定了放大器的速度,因此,第一級反相器消耗的電流較大;第三級的電流消耗極小,所以輸出級的尺寸也較小,實際取高壓管的最小溝道長度0.35 m,為了兼顧放大器的穩(wěn)定性,其NMOS溝道寬度僅取為1 m,PMOS的溝道寬度為3 m。

圖3 本文提出的環(huán)形放大器電路結(jié)構(gòu)Fig.3 The proposed ring amplifier schematic

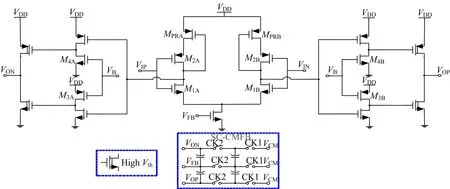

圖3所示的環(huán)形放大器由于是單端輸入單端輸出,它始終帶有單端結(jié)構(gòu)的缺點,如偶次諧波失真大、抗噪聲能力弱等。為了克服這些問題,本文進一步提出了一種全差分環(huán)形放大器,如圖4所示。相比于文獻[5,6]中用兩個單端放大器的偽差分結(jié)構(gòu),本文提出的全差分結(jié)構(gòu)對稱性更好。該放大器的第一級引入了NMOS尾電流源,使輸入對實現(xiàn)差分化,即形成差分輸入、差分輸出的環(huán)形放大器。由于線性區(qū)的MPR對第一級輸出電平具有穩(wěn)定作用,故而第一級無需額外的共模反饋,第二級增益較低,也不需使用共模反饋,第三級的輸出共模反饋采用開關(guān)電容電路(SC-CMFB)[7],反饋控制端VFB即是尾電流源的柵極。CK1和CK2為兩相不交疊時鐘,VCM為放大器的輸出共模電壓,VB的值與VCM相同,VBN由基本的電流鏡偏置產(chǎn)生。輸出級使用了3 V高閾值器件拓展VOS的范圍,在1.8 V的電源電壓下,仿真得到VOS約0.3 V。

圖4 提出的全差分環(huán)形放大器結(jié)構(gòu)及開關(guān)電容共模反饋Fig.4 The proposed fully differential ring amplifier and SC common feedback

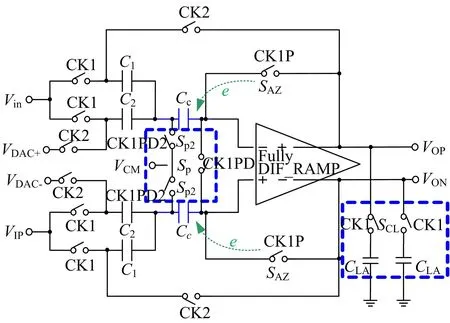

3 基于全差分環(huán)形放大器的余量增益電路設(shè)計

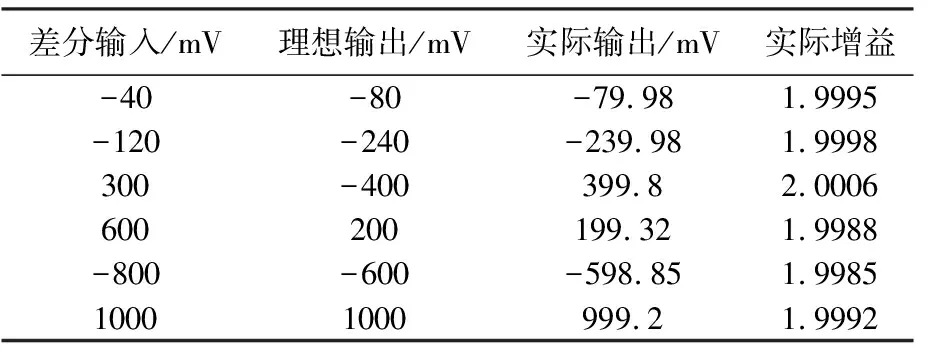

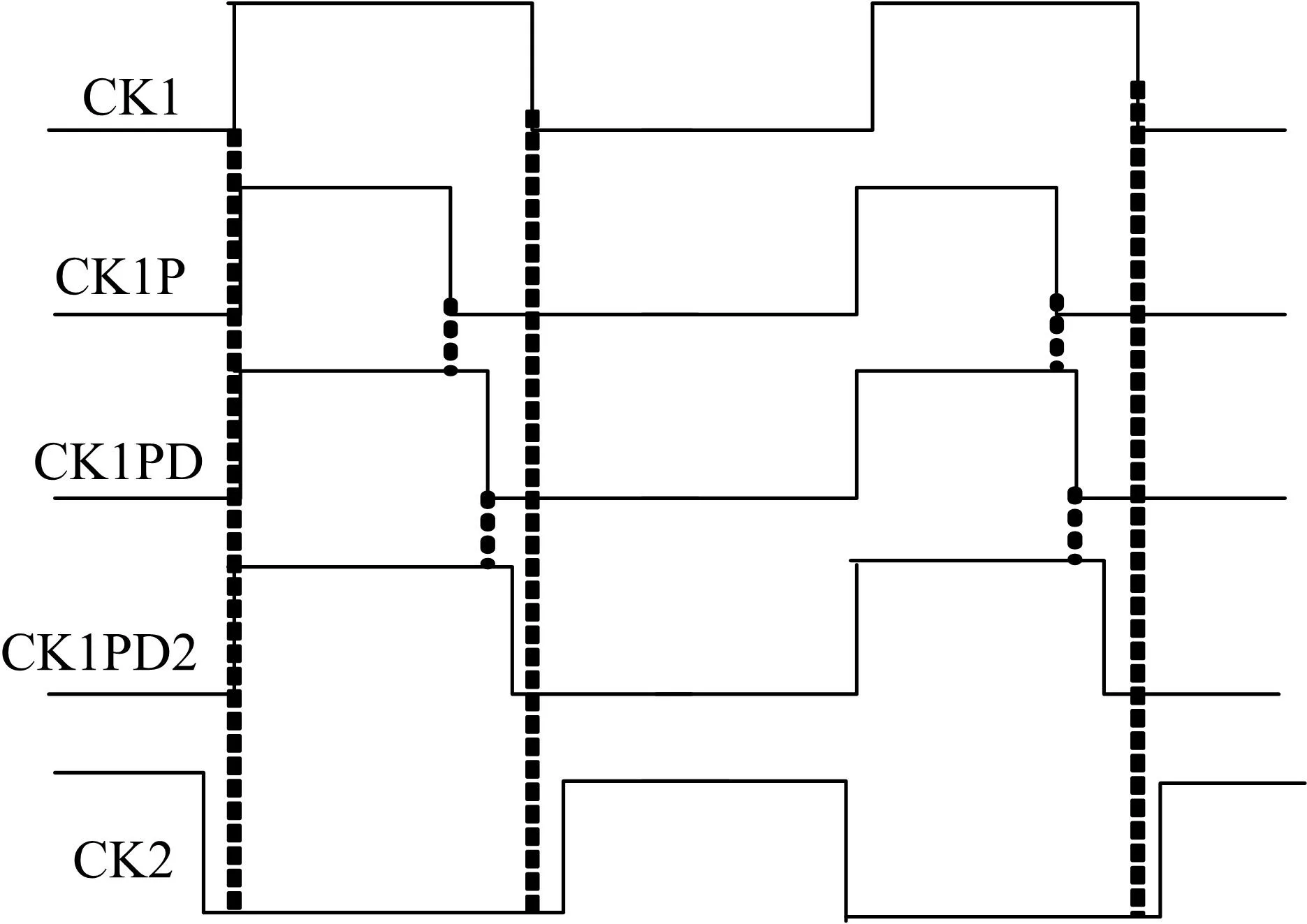

開關(guān)SAZ在斷開時會對電容CC注入電荷,這些電荷會表現(xiàn)為輸出失調(diào)。為消除這一失調(diào),本設(shè)計引入了開關(guān)Sp,它由CK1PD控制,采用適當?shù)臅r序,可以消除SAZ引入的失調(diào)。圖5給出了MDAC中各項時鐘的時序圖,采樣結(jié)束時,調(diào)零開關(guān)SAZ首先斷開,然后Sp斷開,這使環(huán)形放大器輸入端的電位始終近似相等,由開關(guān)SAZ引入的失調(diào)被消除。此后,由CK1PD2控制的開關(guān)Sp2斷開,最后CK1再斷開,由于采樣開關(guān)斷開時的注入電荷沒有泄放通路,不會對電路產(chǎn)生影響。為了觀察MDAC在不同輸入幅度時的增益變化,仿真驗證了一些直流值,仿真結(jié)果可以看出,MDAC能精確地倍乘輸入信號,其輸出誤差小于0.5 LSB(0.976 mV)。

表1 MDAC仿真結(jié)果Table 1 MDAC simulation result

圖5 1.5 bit MDAC的結(jié)構(gòu)和開關(guān)時序Fig.5 1.5 bit MDAC structure and switch timing

4 流水線ADC的設(shè)計與仿真結(jié)果

4.1 流水線ADC的結(jié)構(gòu)

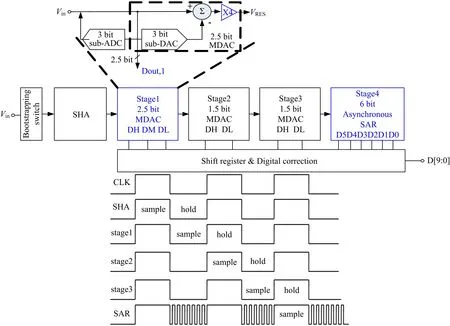

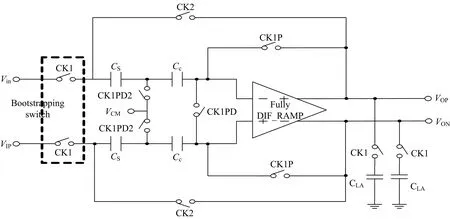

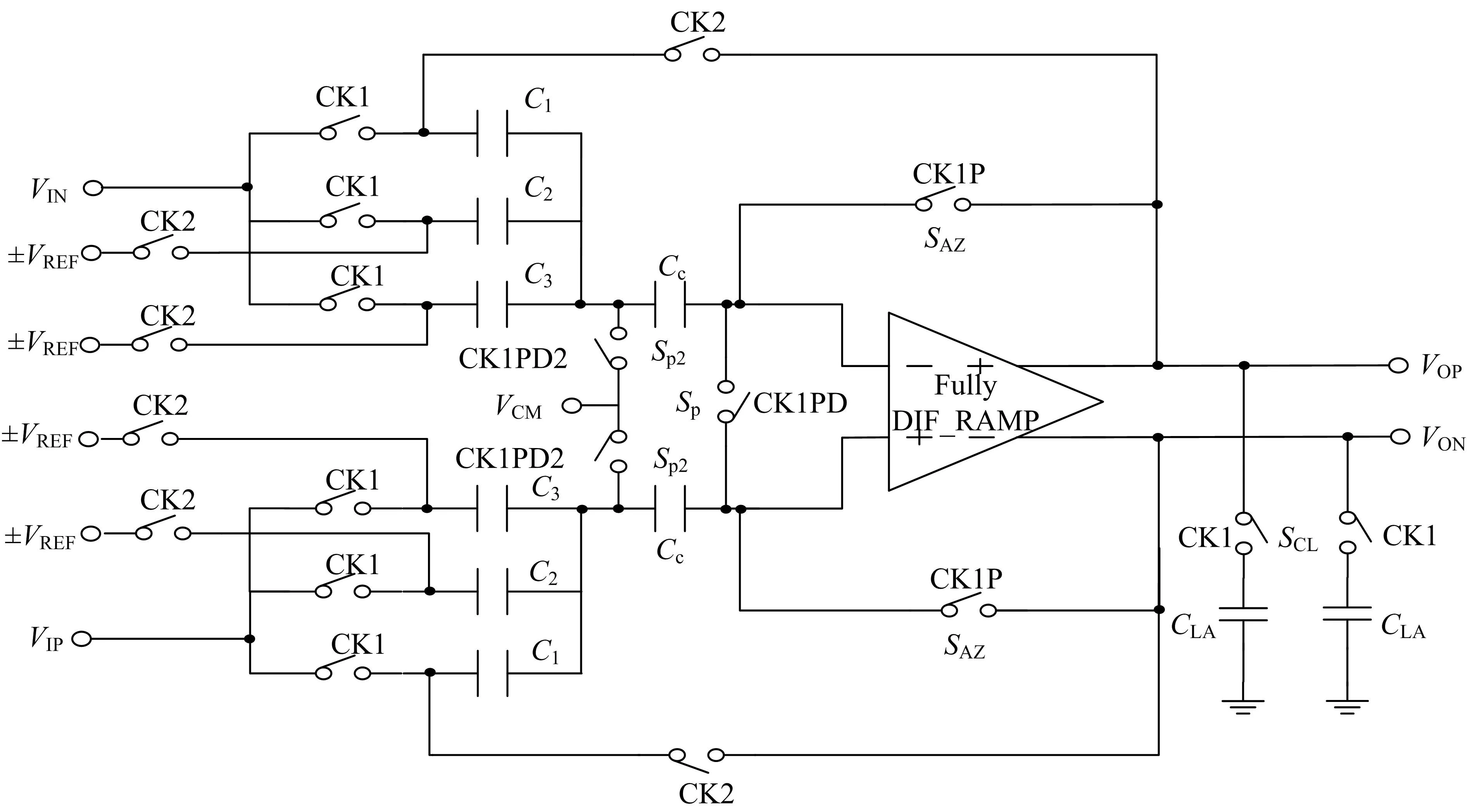

本節(jié)采用所提出的放大器結(jié)構(gòu)設(shè)計了一種10 bit 40 MSample/s 流水線ADC。圖6是流水線ADC的整體架構(gòu)。為了降低ADC的整體功耗,盡可能少地使用放大器,流水線的后6級使用了一個6 bit異步SAR ADC取代了傳統(tǒng)的1.5 bit/stage結(jié)構(gòu)。為消除孔徑誤差,本設(shè)計使用了采樣保持器(SHA)。SHA的電路結(jié)構(gòu)如圖7所示,采樣電容為400 fF,并采用電容翻轉(zhuǎn)式結(jié)構(gòu),由于反饋系數(shù)較大,該結(jié)構(gòu)比電荷重分布式更節(jié)省電流。采樣開關(guān)使用自舉開關(guān),以獲得更低的導(dǎo)通電阻和更好的線性度,采樣保持器靜態(tài)消耗電流約320 A。ADC的首級采用了2.5 bit,其結(jié)構(gòu)如圖8所示,它能提高系統(tǒng)的線性度并降低整體功耗,其采樣電容為400 fF,消耗靜態(tài)電流約440 A。由于流水線每級的容忍誤差逐級加大,分配第二級和第三級的靜態(tài)電流分別為240 A、180 A,采樣電容均為360 fF。Cc的取值不宜過大,也不宜過小,文獻[6]指出Cc+CLA> 2C1才能保證環(huán)路的穩(wěn)定性,本文取Cc為200 fF。

圖6 帶采樣保持器的流水線ADC及每級工作時序框圖Fig.6 Pipeline ADC structure with SHA and timing diagram

圖7 采樣保持器的電路結(jié)構(gòu)Fig.7 Sample and hold amplifier configuration

圖8 2.5 bit MDAC的電路結(jié)構(gòu)Fig.8 2.5 bit MDAC configuration

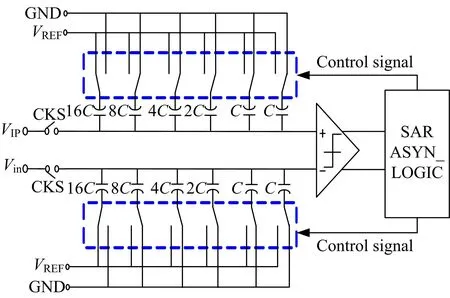

本設(shè)計中6 bit SAR ADC的結(jié)構(gòu)如圖9所示,它采用了改進的單調(diào)開關(guān)時序,能進一步降低功耗。

圖9 6 bit SAR ADC的結(jié)構(gòu)Fig.9 6 bit SAR ADC configuration

與傳統(tǒng)的單調(diào)開關(guān)[8]不同的是,當CKS為高,電容對輸入信號采樣時,上下電容陣列只有最高有效位(MSB)電容連接至VREF,其余位均連接至GND,采樣后直接進行比較并得到最高位輸出結(jié)果,其余位均采取先比較后置位的原則逐位得到輸出碼。這種工作機制使 DAC 中的電容縮減了一半,且每次的比較過程中只有一次開關(guān)動作,大大減少了動態(tài)功耗;這種接法的另一個優(yōu)點是減少了比較器輸入共模電平的變化,從而降低比較器的系統(tǒng)失調(diào)。圖中SAR ADC的總電容個數(shù)為64C,考慮到電容的面積和前級的驅(qū)動能力,單位電容C的取值不能過大,小的電容雖然能提高速度,但會影響精度,本設(shè)計采用18 fF的MIM電容作為單位電容,上下電容陣列的總電容值為1.152 pF。

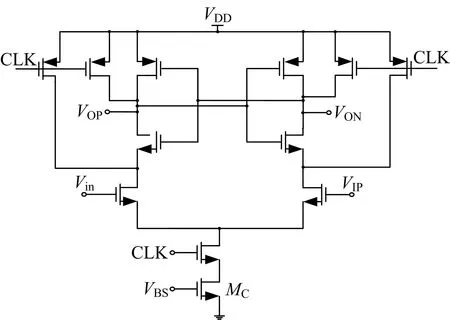

圖106bit SAR ADC使用的比較器結(jié)構(gòu)。為了降低比較器的輸入失調(diào),本設(shè)計在尾電流源中采用了共源共柵結(jié)構(gòu)。共源管MC由偏置電壓VBS控制,由于MC工作在飽和區(qū),其漏源端電壓VDS的變化對電流的影響較小,使輸入對管的過驅(qū)動電壓保持恒定,從而降低輸入失調(diào)的影響。

圖10 6 bit SAR ADC中使用的比較器Fig.10 Comparator used in 6 bit SAR ADC

4.2 流水線ADC后仿真結(jié)果

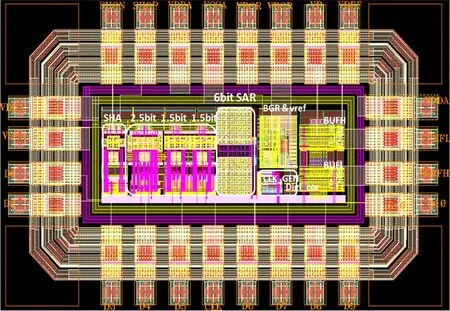

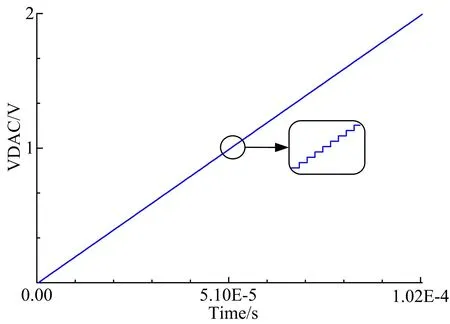

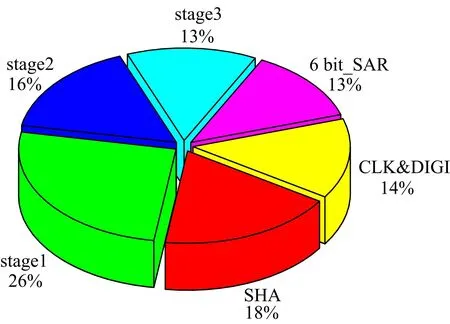

本設(shè)計基于 0.18 μm 1P5M1.8 V/3.3 V混合信號工藝構(gòu)建了一個10 bit 40 MS/s流水線ADC,圖11為ADC的整體版圖,芯片面積為0.235 mm2。本設(shè)計提取出版圖的寄生參數(shù),然后進行電路后仿真。本文首先仿真了ADC在輸入斜坡信號時輸出性能。當輸入一個滿量程(-1 V至+1 V)的斜坡信號,為使每個LSB被采樣次,上升時間設(shè)定為102.4 s(即1024×25 ns×4),再利用理想的10 bit DAC還原出ADC的量化結(jié)果。圖12給出了DAC的輸出瞬態(tài)曲線,它是0~2 V的1024級臺階,每級臺階的高度為1 LSB (1.953 mV),且每個code均勻出現(xiàn),這說明ADC的功能完全正常。圖13給出了ADC各級的(平均)功耗分布餅圖,它與之前的電流預(yù)算值基本吻合。

圖11 ADC的整體版圖Fig.11 Overall ADC layout

圖12 斜坡信號輸入時的理想DAC輸出瞬態(tài)曲線Fig.12 Transient curve of DAC output for ramp input

圖13 ADC各級功耗分布餅圖 Fig.13 A pie chart of ADC stages power consumption

圖14 ADC的靜態(tài)特性仿真結(jié)果Fig.14 ADC static characteristic simulation result

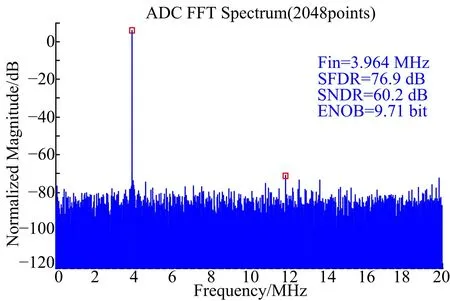

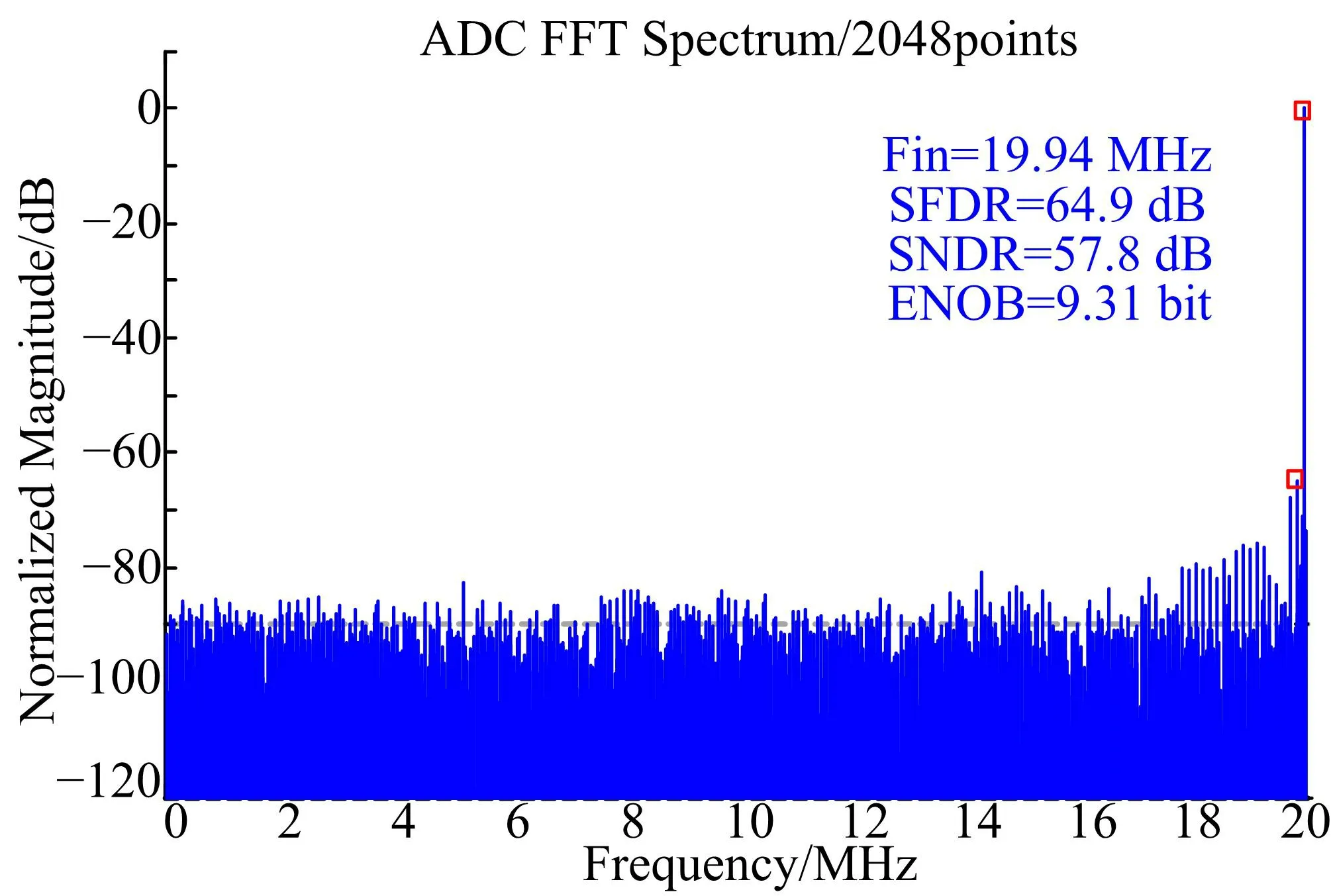

(a) 3.964 MHz

(b) 19.94 MHz圖15 輸入頻率分別為3.964 MHz和19.94 MHz的動態(tài)特性仿真結(jié)果Fig.15 ADC dynamic characteristic simulation result for 3.964 MHz and 19.94 MHz

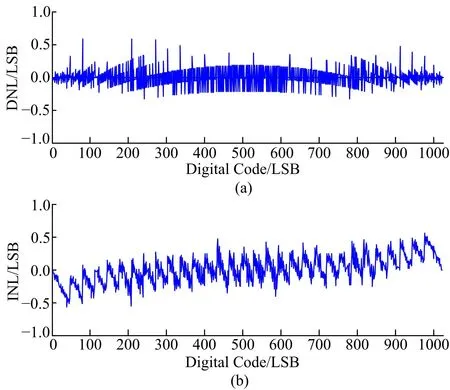

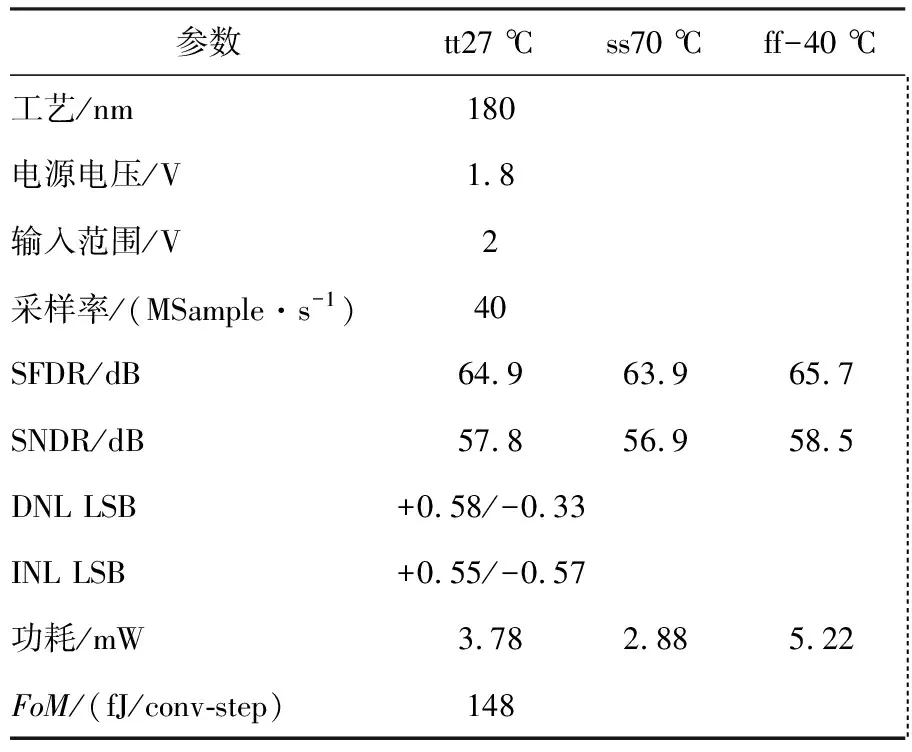

當差分輸入一個頻率為3.964 MHz,幅度為VPP=2 V的正弦波信號,采樣頻率為40 MHz,VDD=1.8 V時,采樣2048個數(shù)據(jù)點,利用Matlab分析ADC的靜態(tài)特性和動態(tài)特性。如圖14所示, DNL最大值約+0.58 LSB/-0.33 LSB,INL的最大值約+0.55 LSB/-0.57 LSB,對于圖像傳感器來說,這樣的DNL和INL特性滿足無失碼的要求。從圖15所示的ADC動態(tài)特性仿真結(jié)果可以看出,在輸入為低頻(Fin= 3.964 MHz)時,ADC的SFDR為76.9 dB, SNDR為60.2 dB,有效位數(shù)約為9.71 bit;在輸入接近奈奎斯特頻率(Fin= 19.94 MHz)時,ADC的SFDR為64.9 dB,SNDR為57.8 dB,有效位數(shù)約為9.31 bit。ADC CORE的平均動態(tài)功耗約為3.78 mW。ADC的FoM定義為:

(3)

式中:Power為功耗,fs為采樣頻率。

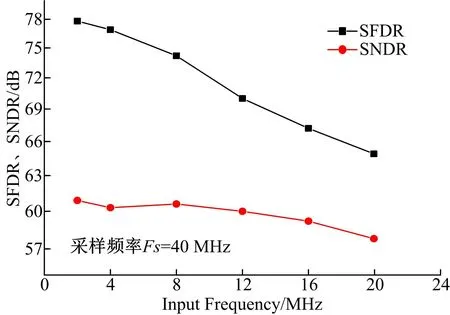

本設(shè)計的FoM值約為148 fJ/conv-step。圖16給出了ADC的SNDR、SFDR與輸入頻率之間的關(guān)系,可以看到,隨著輸入頻率的增加,SFDR也隨之下降,當輸入頻率增大至奈奎斯特頻率附近時,SFDR和SNDR的值最低;這是因為在高頻輸入時,SHA的性能下降較快,導(dǎo)致ADC的整體性能下降,盡管如此,這樣的動態(tài)性能滿足設(shè)計指標。表2對ADC的各項性能進行了總結(jié),并給出了ss corner和ff corner下的性能指標。

圖16 SNDR、SFDR與輸入頻率的關(guān)系 Fig.16 SNDR,SFDR versus the input frequency

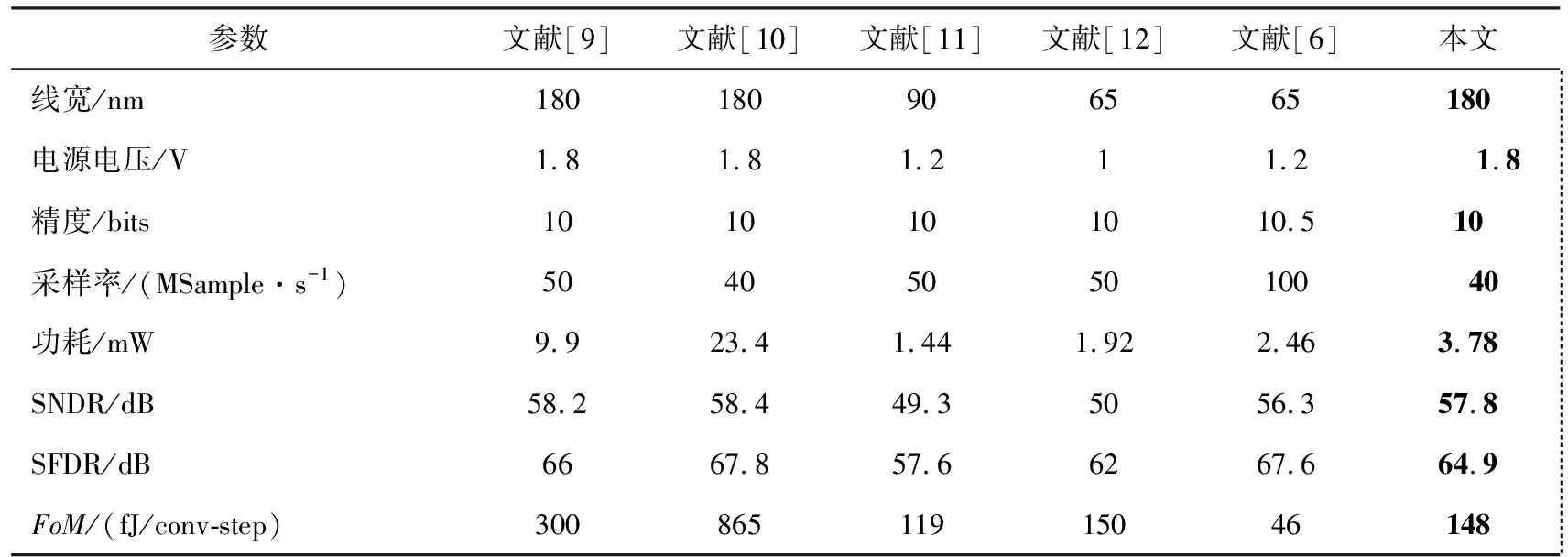

表3列出了本設(shè)計和近年來文獻中流水線ADC的性能指標。由表3可知,本文中ADC的性能雖然低于部分文獻的FoM值,但本文采用較落后的0.18 μm工藝,相同電流消耗的下,本文的FoM值會更高。

表2 ADC性能總結(jié)@19.94 MhzTable 2 ADC performance summary

表3 近年報道的ADC性能對比Table 3 Performance comparison with recent reported pipeline ADC papers

5 結(jié)束語

本文提出了一種新型全差分環(huán)形放大器,并利用提出的放大器設(shè)計了一種10 bit40 MSample/s的流水線ADC,在提取了版圖的寄生參數(shù)后進行了后仿真。仿真結(jié)果顯示本文所提出的全差分放大器功能完全正常,本設(shè)計中的流水線ADC性能滿足CMOS圖像傳感器的應(yīng)用需求,可以投片生產(chǎn)。

參考文獻:

[1] Hamami Shy,F(xiàn)leshel L, Yadid-Pecht O. CMOS APS imager employing 3.3v 12 bit 6.3 Ms/S pipelined ADC[J]. IEEE International Symposium on Circuits and Systems,2004,5:960-963.

[2] Rhee J, Joo Y. Wide dynamic range CMOS image sensor with pixel level ADC[J]. Electronics Letters, 2003, 39(4): 360-361.

[3] Abo A M, Gray P R. A 1.5 V, 10 bit, 14.3 MS/s CMOS pipeline analog-to-digital converter[J]. IEEE J. Solid-State Circuits, 1999, 34(5): 599-606.

[4] Brooks L, Lee H-S. A 12 b, 50 MS/s, fully differential zero-crossing based pipelined ADC[J]. IEEE J. Solid-State Circuits,2009,44 (12):3329-3343.

[5] Hershberg B,Weaver S, Sobue K, et al., Ring amplifiers for switched capacitor circuits[J]. IEEE J. Solid-State Circuits, 47(12): 2928-2942.

[6] Lim Y, Flynn M P. A 100 MS/s 10.5b 2.46 mW comparator-less pipeline ADC using self-biased ring amplifiers[C]∥IEEE ISSCC Dig Tech Papers, 2014: 202-203.

[7] Razavi B. Design of analog CMOS integrated circuits[D]. Boston, MA, USA: McGraw-Hill, 2001:435-436.

[8] Liu C C, Chang S J, Huang G Y, et al. A 10 bit 50 MS/s SAR ADC With a Monotonic Capacitor Switching Procedure[J]. IEEE Journal of Solid-State Circuits, 2010, 45(4):731-740.

[9] Ahmed I, Mulder J, Johns D A. A Low-Power Capacitive Charge Pump Based Pipelined ADC[J]. IEEE Journal of Solid-State Circuits, 2010, 45(5):1016-1027.

[10] Oh G G, Lee C K, Ryu S T. A 10 Bit 40 MS/s Pipelined ADC With a Wide Range Operating Temperature for WAVE Applications[J]. IEEE Transactions on Circuits & Systems II Express Briefs, 2014, 61(1):6-10.

[11] Hu J, Dolev N, Murmann B. A 9.4 bit, 50 MS/s, 1.44 mW pipelined ADC using dynamic residue amplification[C]∥2008 IEEE Symposium on VLSI Circuits,2008:216-217.

[12] Lajevardi P, Chandrakasan A , Lee HS , et al, Zero-crossing detector based reconfigurable analog system[J]. Solid State Circuits Conference , 2011 , 46 (11) :1-4.