基于分類學(xué)習(xí)的側(cè)信道硬件木馬檢測方法研究

楊達(dá)明 黃姣英 高成

摘要 目前集成電路開發(fā)周期中,存在很多安全性無法保障的環(huán)節(jié),使集成電路的開發(fā)受到硬件木馬的威脅。硬件木馬通常只在非常特殊的值或條件下才能被觸發(fā)并且發(fā)生作用,傳統(tǒng)的結(jié)構(gòu)測試和功能測試難以快速觸發(fā)并檢測。本論文針對這一問題,開展了基于側(cè)信道檢測的硬件木馬檢測方法研究,選取全局電流作為側(cè)信道測試的信號,完成檢測識別,證明了基于側(cè)信道功耗的硬件木馬檢測方法,可作為通用檢測方法對集成電路上未知類型的硬件木馬進(jìn)行檢測:在此基礎(chǔ)上,研究設(shè)計了一種基于分類學(xué)習(xí)的硬件木馬快速識別方法,通過機(jī)器分類學(xué)習(xí)建立模型,以此來分析未知數(shù)組,可達(dá)到自動化檢測識別硬件木馬的效果,識別效果達(dá)到為73.57%。該方法可快速、自動對批次電路進(jìn)行硬件木馬檢測識別。

【關(guān)鍵詞】硬件木馬 側(cè)信道分析 分類學(xué)習(xí)

1 引言

近年來,半導(dǎo)體行業(yè)迅速發(fā)展,為了縮短集成電路的設(shè)計周期,降低制造成本,集成電路的設(shè)計與制造過程趨向于分離,導(dǎo)致了集成電路在外包制造過程中存在風(fēng)險。集成電路芯片在不受控的制造過程中,就可能會被嵌入惡意電路結(jié)構(gòu),形成硬件木馬( Hardware Troj anHorse)。

硬件木馬種類繁多,不同硬件木馬實(shí)現(xiàn)的功能不同,其電路特征也有很大差異,使得硬件木馬的檢測十分困難。目前集成電路硬件木馬的檢測還未形成用戶需求,集成電路的質(zhì)量控制過程還沒有提出硬件木馬檢測保障的硬性要求,因此硬件木馬的檢測方法,大多數(shù)也是集成電路開發(fā)者針對自己的產(chǎn)品做的預(yù)防性研究,以及大型集成電路針對芯片安全進(jìn)行的健壯性設(shè)計。

最早研究的硬件木馬體積較大特征明顯,使用的檢測方法是傳統(tǒng)的物理檢測。這種傳統(tǒng)的物理檢測主要是利用成熟的集成電路逆向工程手段,對需要驗(yàn)證的芯片,首先開帽,露出芯片電路,然后研磨芯片層,反復(fù)掃描每層電路照相,提取照相圖片中的金屬線圖案,再與電路原始板圖進(jìn)行對比,從而判斷芯片中是否含有硬件木馬。但隨著電路規(guī)模越來越大,物理檢測效果已經(jīng)逐漸不能滿足硬件木馬檢測需求

根據(jù)硬件木馬激活特性,結(jié)合日益成熟和先進(jìn)的自動測試設(shè)備ATE (Automatic TestEquipment),研究人員開發(fā)了基于邏輯功能測試的檢測方法,即ATPG( Automatic TestPattem Generation)。這種方法通過生成特定的自動測試矢量,通過研究輸入與相應(yīng)的匹配與否來判定電路中是否含有硬件木馬,ATPG的原理是通過設(shè)計測試向量快速激活硬件木馬,并通過輸出來判定硬件木馬的存在與否。這種測試方法隨著硬件木馬激活條件越來越隱蔽,測試向量的生成也越來越復(fù)雜,面臨著測試效率和覆蓋率的問題。為了降低測試向量的長度,更好的觀測到硬件木馬,提高檢測效率,可以在電路中插入一些特殊的電路以增加內(nèi)部節(jié)點(diǎn)的可控性與可觀察性,從而提高硬件木馬的激活特性,使檢測更容易。或?qū)﹄娐穬?nèi)部節(jié)點(diǎn)中活性很低的邏輯進(jìn)行多重觸發(fā),以最大程度激活木馬,降低測試向量長度。

另一種新興的檢測技術(shù)是側(cè)信道分析技術(shù),它是檢測集成電路的側(cè)信道信號,分析識別芯片中是否存在硬件木馬。側(cè)信道信號包括電路的功率信號、時序信號、電磁信號及溫度等。硬件木馬一般都會降低芯片的性能,或改變芯片的功率特性。因此木馬會在不同程度上改變電路的參數(shù)特征,從而影響電路中的線和門的功率特性或延時特性。

基于側(cè)信道分析的硬件木馬檢測方法,主要有基于功率信號的檢測方法和基于時序信號的檢測分析。基于功率信號的檢測方法常用手段是IC指紋法、局部電路的功耗分析、電流積分法以及基于電源瞬態(tài)功率的檢測方法;基于時序信號的監(jiān)測分析常用的是基于路徑延遲的指紋法和基于高速延時特性檢測法。

基于現(xiàn)有的檢測方法,硬件木馬的檢測存在的問題有:

(1)集成電路工藝向納米級發(fā)展,電路版圖也越來越龐大,很難通過物理檢測和破壞性反向工程來檢測出硬件木馬,并且成本很高耗時很長。

(2)硬件木馬通常只在非常特殊的值或條件下才能被觸發(fā)并且發(fā)生作用,其它時候?qū)υ茧娐返墓δ懿o影響,傳統(tǒng)的結(jié)構(gòu)測試和功能測試難以快速觸發(fā)并檢測。

針對現(xiàn)有硬件木馬檢測存在的問題,本論文基于分類學(xué)習(xí)對側(cè)信道進(jìn)行檢測,可達(dá)到自動化檢測識別硬件木馬的效果,有助于在形成硬件木馬檢測需求時,大大提高檢測效率。2側(cè)信道硬件木馬檢測方法研究

側(cè)信道檢測技術(shù)是現(xiàn)有覆蓋性最廣、檢測效率最高的硬件木馬檢測技術(shù),對未知類型硬件木馬的檢測效果最好。這一結(jié)論的是依據(jù)無論集成電路是何種類型、何種規(guī)模,在工作狀態(tài)下都會有體現(xiàn)其特征的功率、時序、電磁和溫度等側(cè)信道信號。

基于側(cè)信道檢測的硬件木馬檢測方法相較于其它方法較好,尤其是基于功率信號的側(cè)信道分析技術(shù)較為成熟。無論硬件木馬是何種類型、大小或激活率,只要存在電路中,就會產(chǎn)生功耗。論文采用基于功耗的硬件木馬檢測方法進(jìn)行硬件木馬的檢測,有以下優(yōu)點(diǎn):

(1)非破壞性。不需要破壞電路芯片或?qū)﹄娐愤M(jìn)行硬修改,論文形成的硬件條件和現(xiàn)有設(shè)備,也只能允許非破壞性檢測;

(2)不需要觸發(fā)硬件木馬。本論文設(shè)計的時序型硬件木馬觸發(fā)時序?yàn)椤?11111”,理論上運(yùn)行27即128次才會觸發(fā),但由于時鐘頻率高還是能比較快的觸發(fā)。但是通過簡單的修改就可以大大提高硬件木馬被觸發(fā)的時間。因此在硬件木馬靜默狀態(tài)下進(jìn)行測試是理想的。

(3)可以進(jìn)行全局測試。不需要進(jìn)行節(jié)點(diǎn)采樣,在FPGA開發(fā)板上新建采樣節(jié)點(diǎn)也是比較復(fù)雜的,通過電路功耗的對比識別可以提高效率,降低測試難度。

本論文擬采用FPGA作為硬件木馬與芯片的運(yùn)載平臺進(jìn)行功耗檢測。FPGA為基于CMOS工藝的集成電路,電路的功耗包括靜態(tài)功耗和動態(tài)功耗。靜態(tài)功耗是電路未工作狀態(tài)下由晶體管泄漏電流引起的功耗,即泄露功耗。靜態(tài)功耗Pleakage計算公式如式(1)所示:

Pleakage-VDD· Ileakaee

(l)

式中VDD為晶體管的供電電壓,Ileajage為晶體管總漏電流。

動態(tài)功耗是電路在工作狀態(tài)下晶體管在導(dǎo)通和截止兩種狀態(tài)中轉(zhuǎn)換引起的功耗,而這部分的功耗又包括兩部分:狀態(tài)轉(zhuǎn)換過程中的

以上分析可見,COMS電路功耗與時鐘頻率有很大關(guān)系,在基于側(cè)信道硬件木馬識別的過程中,可以將時鐘頻率作為信號采集樣本集的一個特征值。基于論文現(xiàn)有的硬件條件,對于電路負(fù)載電容的分析測量較為困難,因此如何采集電路功耗并識別硬件木馬功耗是主要難點(diǎn)。

文獻(xiàn)[16]中提出,在集成電路中,將硬件木馬的功耗作為電路總功耗的噪聲功耗來處理。這種處理方法,是將時序型和組合型硬件木馬對電路的修改,一并看作工藝噪聲,理論上是可行的:對比原始電路和有硬件木馬的電路,作為同一批次樣本,其工藝噪聲應(yīng)該相似,若噪聲信號區(qū)別較大,則可判定為存在硬件木馬。其測試方式為測試全局電流。

3 硬件木馬功耗測試方法研究

論文依據(jù)上一章的理論,展開基于全局電流的功耗測試。同時,為了便于識別判定硬件木馬,需要測試數(shù)據(jù)集有足夠的多組特征值。理論上頻率增大,電路功率會增大,并可初步認(rèn)為硬件木馬電路與目標(biāo)電路功率的增幅對頻率變化的響應(yīng)不同,因此在改變輸入時鐘頻率信號作為激勵時,可以進(jìn)一步研究頻率的變化與硬件木馬檢測識別的聯(lián)系。

對式(6)進(jìn)行變式得到式(7)。電流測試,采用不同頻率信號輸入作為激勵,測試電流信號響應(yīng)進(jìn)行采樣。次樣本中測試偏差不大,或偏差不干擾硬件木馬功耗,那么根據(jù)電路全局電流的差異,一定程度上就可以判斷電路中是否含有硬件木馬。

頻率信號的發(fā)生,采用ISE提供的時鐘分頻IP核,該IP核能提供20MHz-100MHz的時鐘頻率。

由于提供的時鐘為連續(xù)時鐘,基于時序得到的連續(xù)采樣或多點(diǎn)采樣無法對其分析,因此,在時鐘頻率可作為樣本集特征值的情況下,進(jìn)行靜態(tài)電流采樣,即得到[F,W]的頻率.功耗樣本集。

4 基于分類學(xué)習(xí)的硬件木馬檢測研究

4.1 有無硬件木馬芯片功耗檢測結(jié)果分析

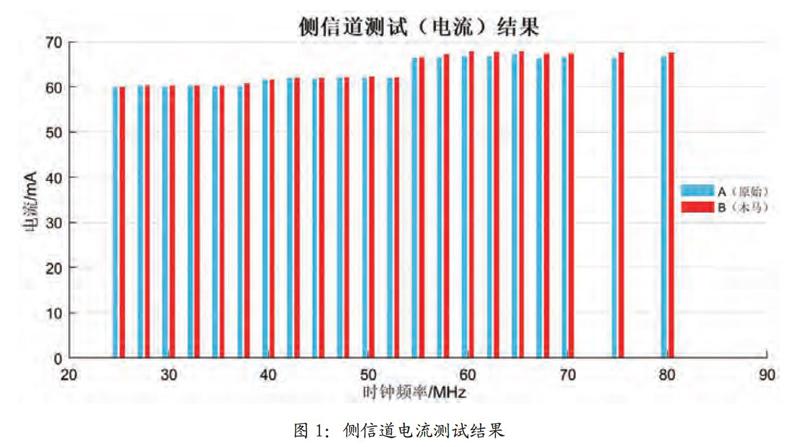

本文設(shè)計編譯的程序,包括無硬件木馬的流水燈電路A和含有時序型硬件木馬的流水燈電路B,分別下載燒寫到FPGA中固化后,脫機(jī)供電運(yùn)行。功耗的測試采樣,為不同時鐘頻率下全局電流響應(yīng),圖l為側(cè)信道電流測試結(jié)果。

測試數(shù)據(jù)顯示:含有硬件木馬的電路B全局電流測試結(jié)果大于不含硬件木馬的原始電路A,即時序型硬件木馬對側(cè)信道功耗的作用可識別。在21個采樣點(diǎn)中,原始電路A的全局電流均值為63 .429mA,含硬件木馬的電路B全局電流均值為63.917mA。

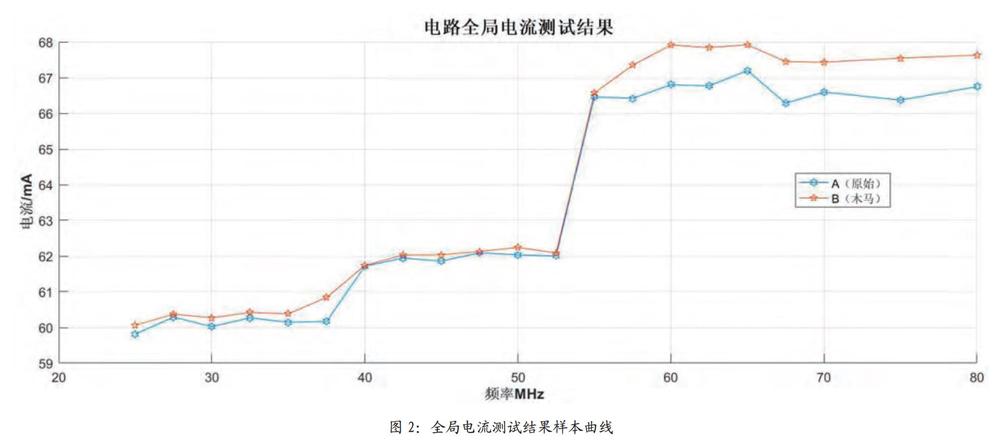

直接測試結(jié)果表明,時序型硬件木馬植入到電路中,對原始電路側(cè)信道信號造成了影響,通過圖2全局電流測試的結(jié)果.可以識別出含硬件木馬的電路,即全局電流更大的電路。

識別結(jié)果在建立在原假設(shè)的基礎(chǔ)上:假設(shè)A和B噪聲信號在測試中相等,A與B的偏差都由硬件木馬造成。數(shù)字萬用表采集全局電流,是測試采樣時間區(qū)間內(nèi)均值,可以忽略測試誤差。根據(jù)測試曲線分析,在高頻時( >60MHz)識別效果可觀,在低頻(<50MHz),A與B電流差值小,很難直接區(qū)分。根據(jù)直接測試分析結(jié)果,有以下結(jié)論:

(1)基于側(cè)信道功耗檢測的硬件木馬識別方法是可行的,在假設(shè)工藝噪聲一致的前提下,通過全局電流的檢測可以識別原始電路和含有硬件木馬的電路;

(2)對于時序型硬件木馬,頻率.功耗的特征關(guān)系是存在的,這一特征對于含有時鐘頻率的集成電路也基本適用,全局功耗隨著頻率增大而增大。在硬件木馬檢測中,初步結(jié)論顯示,頻率越高,硬件木馬識別效果越好;

(3)論文時序型硬件木馬形成的實(shí)體硬件條件,與真實(shí)的芯片環(huán)境還有差距,工藝噪聲對基于FPGA開發(fā)板的流水燈硬件木馬功耗影響微弱,但對于集成電路芯片影響可能會較大,因此直接識別是不夠的,需要研究一種信號差異較小情況下的判別方法。

4.2 基于分類學(xué)習(xí)的硬件木馬檢測結(jié)果分析

判別分析是對未知類別的樣本進(jìn)行歸類的一種方法,判別分析的研究對象是已經(jīng)確定了類別的樣本,根據(jù)抽樣的樣本建立判別公式和判別準(zhǔn)則,然后根據(jù)這些判別公式和判別準(zhǔn)則,判別未知類別的樣品所屬的類別。

論文研究中,硬件木馬識別面臨的問題是,部分樣本容易識別,部分樣本難以確定,因此在原理上可以采用這種判別分析的方法。與常規(guī)的集成電路功能測試相比,硬件木馬檢測存在一個較大的潛在問題:即使電路中含有硬件木馬,其參數(shù)也不會超過電路正常工作閾值,那么對一批芯片進(jìn)行硬件木馬檢測,就需要對每一個芯片都采取測試后分析,比較參數(shù)差異后人工判別硬件木馬的有無,這種判別無疑是低效率的,測試數(shù)量龐大時人為誤判的可能性就很高。

論文依據(jù)馬氏距離判別的原理,研究了一種基于機(jī)器分類學(xué)習(xí)的硬件木馬快速識別方法,基本原理方法是:用己知無硬件木馬的原始特征數(shù)集A和已知有硬件木馬的特征數(shù)集B,作為訓(xùn)練數(shù)組,使機(jī)器進(jìn)行擬合學(xué)習(xí),形成一種硬件木馬判定依據(jù),然后以此模型去檢驗(yàn)其它樣品數(shù)集,確定其它數(shù)集是符合A類還是B類,從而達(dá)到自動測試和快速識別的效果。

分類學(xué)習(xí)是MATLAB中開發(fā)的成熟分類學(xué)習(xí)程序,基于機(jī)器分類學(xué)習(xí)的硬件木馬快速識別方法流程如下:

4.2.1 導(dǎo)入學(xué)習(xí)數(shù)據(jù)

將已知的無硬件木馬A特征數(shù)集和有硬件木馬B特征數(shù)集進(jìn)行整理,以頻率和全局電流為輸入,輸出為A和B類別特征C,A--l表示無木馬,B-1表示有木馬。即以[C,f,I]為元素的3x42矩陣。

4.2.2 機(jī)器學(xué)習(xí)數(shù)據(jù)

圖3中row 3即全局電流特征值I,row 2為時鐘頻率特征值f,row 1為輸出特征值,硬件木馬類別C。以rOW 3和row 2作為模型學(xué)習(xí)的輸入( Predictor),以row 1為輸出響應(yīng)( Response),選取迭代學(xué)習(xí)次數(shù),進(jìn)行模型學(xué)習(xí)。迭代選取交叉驗(yàn)證的方式,迭代次數(shù)最高為樣本組數(shù)。

4.2.3 選取最佳模型

機(jī)器分類學(xué)習(xí),根據(jù)機(jī)內(nèi)設(shè)定的23中模型進(jìn)行,并最終得出最佳的匹配模型。

圖4為訓(xùn)練后得到的數(shù)組結(jié)果,其中最符合的兩種是基于Complextree和Mediumtree的模型,學(xué)習(xí)中交叉驗(yàn)證的正確率為66 7%。

4.2.4 生成分類工具

使用Exportmodel選項(xiàng)即可生成學(xué)習(xí)了硬件木馬分類的模型工具TrainedClassifier,并可在工作區(qū)調(diào)用。

4.2.5 調(diào)用分類工具進(jìn)行快速判別

調(diào)用分類工具的指令為:

yfit = trainedClassifier.predictFcn(X)

X為需要進(jìn)行判別的數(shù)組。

論文研究再次測試了一組流水燈電路(未知是否含有硬件木馬)的頻率.功耗,將其用分類學(xué)習(xí)工具進(jìn)行判定,運(yùn)行以下指令:

X= xlsread(數(shù)據(jù)4.xlsx)

yfit = TrainedClassifier.predictFcn(X)

bar(yfit)

圖5為指令運(yùn)行得到的判定結(jié)果。根據(jù)定義.1為無硬件木馬,l為有硬件木馬,識別效果達(dá)到為73.57%。顯然所測的特征值數(shù)集為植入了硬件木馬的流水燈電路。返回查看流水燈代碼,確定是含有硬件木馬的電路,判別準(zhǔn)確。

論文研究得到的基于分類學(xué)習(xí)的硬件木馬快速識別方法,可以大大提高批產(chǎn)品硬件木馬檢測的效率,以此為基礎(chǔ),可以實(shí)現(xiàn)硬件木馬檢測的自動化識別。

5 結(jié)論

本論文開展了基于側(cè)信道檢測的時序型硬件木馬檢測方法研究,選取全局電流作為側(cè)信道測試的信號,與硬件木馬類型特征無關(guān),成果完成檢測識別,證明了基于側(cè)信道功耗的硬件木馬檢測方法,可作為通用檢測方法對集成電路上未知類型的硬件木馬進(jìn)行檢測;在此基礎(chǔ)上,研究設(shè)計了一種基于分類學(xué)習(xí)的硬件木馬快速識別方法,通過機(jī)器分類學(xué)習(xí)建立模型,以此來分析未知數(shù)組,可達(dá)到自動化檢測識別硬件木馬的效果,識別效果達(dá)到為73.57%。該方法有助于在形成硬件木馬檢測需求時,大大提高檢測效率。

參考文獻(xiàn)

[1]王曉晗,李雄偉,張陽等,一種基于故障注入的硬件木馬設(shè)計[J],軍械工程學(xué)院學(xué)報,2015 (05):57-61.

[2]謝海,恩云飛,王力緯.電磁泄漏型硬件木馬設(shè)計與檢測[J].廣東工業(yè)大學(xué)學(xué)報,2013 (04):70-73.

[3]謝方方,李雄偉,張陽等,基于RS232協(xié)議時隙的硬件木馬設(shè)計[J].科學(xué)技術(shù)與工程,2013,13 (28):8284-8287.

[4]羅宏偉.集成電路芯片安全隱患檢測技術(shù)[J].半導(dǎo)體技術(shù),2007,32 (12):1094-1097.

[5]李振,李磊,馮穩(wěn)鋒等,一種低觸發(fā)率的硬件木馬設(shè)計[J].微電子學(xué)與計算機(jī),2014 (05).

[6]羅宏偉.集成電路芯片安全隱患檢測技術(shù)[J],半導(dǎo)體技術(shù),2007. 32 (12):1094- 1097.

[7] Jha S, Jha S K. RandomizationBased Probabilistic Approach toDetect Trojan Circuits [C]// IEEEHigh Assurance Systems EngineeringSymposium. IEEE Computer Society,2008: 117-124.

[8]Pomeranz I, Reddy S M. A Measure ofQuality for n-Detection Test Sets [J].IEEE Transactions on Computers,2004, 53 (11): 1497-1503.

[9]薛明富,胡愛群,王箭.基于探索式分區(qū)和測試向量生成的硬件木馬檢測方法[J].電子學(xué)報,2016. 44 (05):1132-1138.

[1O] Becker G T, Kasper M, Moradi A, etal.

Side-channel

based wa terma rksfor integrated circuits [C],/ IEEEInternat ional

Sympos ium on Hardware-Oriented Security and Trust. IEEE,2010: 30-35.

[11]Agrawal D. Baktir S, KarakoyunluD, et al. Trojan Detection using ICFingerprinting [J] . 2008: 296-310.

[12]Lamech C, Rad R M, Tehranipoor M,et al. An Experimental Analysis ofPower and Delay Signal-to-NoiseRequirements for Detecting Trojansand Methods for Achieving theRequired Detection Sensitivities [J].IEEE Transactions on InformationForensics & Security, 2011,6 (03) : 1170-1179.

[13] Rai D. Lach J. Performance of delay-based Trojan detection techniquesunder parameter variations [C]. IEEEInternational Workshop on Hardware-Oriented Security and Trust. IEEEComputer Society, 2009: 58-65.

[14] Nowroz A N. Hu K, Koushanfar F, et al.Novel Techniques for High-SensitivityHardware Trojan Detection UsingThermal and Power Maps [Jl. Computer-Aided Design of Integrated Circuitsand Systems, IEEE Transactions on,2014,

33 (12): 1792-1805.

[15lRad R M, Wang X, Tehranipoor M, etal. Power supply signal calibrationtechniques for improving detectionresolution to hardware Trojans [C].Ieee/acm International Conferenceon Computer-Aided Design. IEEE,2008: 632-639.

[16]趙志勛,倪林,李少青.硬件木馬電路功耗的檢測方法[J],北京郵電大學(xué)學(xué)報,2015, 38 (04): 128-132.