基于有限狀態機的PLC程序設計方法

范雄濤 沈 勇 和淑芬

(云南民族大學電氣信息工程學院,昆明 650500)

可編程序控制器(programmable logic controller,PLC)本質是一個微型計算機,在現代化工廠中大量采用PLC完成控制系統的邏輯控制[1]。根據是否與原來的狀態有關,可將其分為組合邏輯電路和時序邏輯電路,時序邏輯電路的輸出取決于當前的輸入和原來的狀態[2]。根據存儲電路的狀態變化時刻,可將時序電路分為同步時序電路和異步時序電路。同步時序電路的所有觸發器的狀態變化都在同一脈沖作用下發生[3]。

1 有限狀態機

時序電路是狀態依賴的,故稱為狀態機[4]。因輸入和輸出都是有限的,故稱為有限狀態機。有限狀態機理論已經形成了一整套完整的體系,根據輸出信號是否與輸入信號有關,可將狀態機分為Moore狀態機和Mealy狀態機[5]。

可將狀態機歸納為4個因素:現態、次態、動作、條件[6]。其中,次態是指條件滿足后執行動作要遷移的新狀態。“次態”是相對于“現態”而言的,“次態”一旦被激活,就轉變成新的“現態”。

作進一步歸納總結,“現態”、“次態”可以統一起來為“狀態”,“條件”、“動作”可以統一起來為“遷移條件”,并可以用函數的表示方法更加直觀地認識其中的關系。

狀態:{現態×遷移條件→次態}狀態機采用的表示方法有許多種,在此采用的是表格和圖形的表示方法[7]。

2 同步時序電路

對異步時序電路進行分析,就必須考慮每個狀態時刻觸發器與時鐘信號的關系[8],對于復雜性輸入的電路來說,其設計的工作量較大,并且各存儲單元的狀態轉換因受到時鐘信號觸發而存在時間差異從而可能造成輸出狀態短時間的不穩定,而這種不穩定有時可能是無法預計的,從而電路設計的復雜性以及調試的工作量。

時鐘同步狀態機所有觸發器的狀態更新是在同一時刻[9],其輸出狀態變化的時間不存在差異或者差異績效,在時鐘脈沖兩次作用的間隔期間,從觸發器輸入到狀態輸出的通路被切斷,也不會改變觸發器的輸出狀態,所以很少發生輸出不穩定的現象[10]。更重要的是,其電路的狀態很容易用固定周期的時鐘脈沖邊沿清楚地分離為序列步進,每一個步進都已通過輸入信號和所有觸發器的現態單獨進行分析,從而形成一套較系統、易掌握的分析和設計方法。

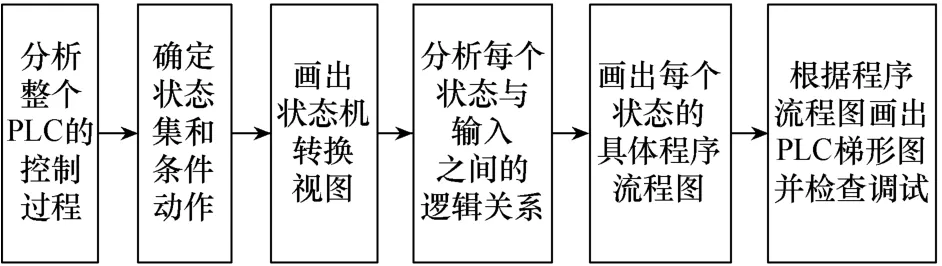

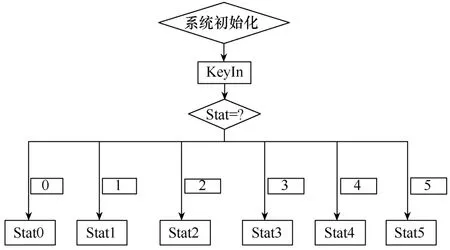

在啟動PLC的CPU后,系統將循環執行主程序OB1,并可在執行過程中調用其他邏輯功能塊,如FC、FB、DB、SFB和SFC等[9],將有限狀態機理論應用于PLC程序設計。關鍵在于分析整個系統的狀態集和遷移條件、現態遷移到次態的具體邏輯、遷移條件與系統的輸入之間的關系。狀態集包含了PLC系統的起始狀態、現態與次態,輸入對應于PLC系統的狀態轉換函數的動作過程,輸出對應于整個PLC系統的狀態與動作的響應。復雜型輸入狀態的PLC程序設計的基本思路如圖1所示。

程序狀態流程圖是程序分析中最實用的分析技術,它是進行程序流程分析過程中最基本的工具。利用程序流程圖與狀態機視圖的相結合。可以有效地描述PLC系統中狀態、輸入、狀態轉換之間的相互關系。

3 基于有限狀態機的PLC程序設計的應用

本文以一個無浮點四則運算的計算器PLC程序設計為例,分析有限狀態機理論在復雜PLC程序設計的應用。本計算器包括數字鍵0—9,操作碼 + ? */、=、清零鍵C在內的16個輸入按鍵。計算器程序的復雜性在于:①輸入操作數的程序設計;②計算時輸入按鍵順序的隨機性強,并且輸入的歷史有關。而利用有限狀態機理論分析該計算器程序的難點是如何合理劃分整個系統的所有狀態和輸入屬性,從而減少工作量。

對于輸入操作數的程序,可做一個 FC的函數塊,命名為DATA_IN,其輸入操作數程序的核心是buff=buff*10+KeyData,其中buff代表按鍵緩沖區,KeyData為數字鍵。因輸出與輸入的歷史有關,故只采用組合邏輯電路的設計方法不能解決記憶的問題,同樣因異步時序邏輯電路設計的復雜性和不穩定難調試等缺點會給本程序設計增加困難,故采用同步時序邏輯電路的設計方法指導該計算器的程序設計。PLC主程序OB1掃描是自上而下、自左而右循環掃描執行的,故要使得系統的狀態在一個掃描周期只改變一次,應在主程序OB1不應設計成一個觸點驅動兩個狀態的情況,避免程序在一個掃描的過程中因一個觸點驅動狀態寄存器改變引起后面的程序運行的混亂,從而減少程序設計的復雜性[11]。

本文利用有限狀態機理論分析整個計算過程的所有狀態集和動作輸入,能夠全面地枚舉所有的計算過程。顯然,無浮點四則運算的計算過程通常為a?b=c,其中a表示第一操作數OP1,?表示操作OP,b表示第二操作數OP2,c表示a、b進行運算的結果,為了能再進行下一步的運算,可將計算結果放在OP1中。即可得到3個輸入過程:輸入第一操作數OP1、輸入操作OP、輸入第二操作數OP2。在進行運算時,根據輸入的可能性會出現以下情況:上電初始化,輸入第一個操作數并且能繼續輸入第一個操作數,接著輸入操作,再輸入第二個操作數,按下等號鍵,計算結果放在第一操作數中,接著等待操作碼進行下一次運算,其中如果輸入的操作數或計算結果有可能因溢出而導致出錯或者按下清零鍵直接恢復初始化。根據以上分析并區分因輸入的情況而使狀態轉換可得到以下6種狀態。

Stat0:初始即上電程序初始化;

Stat1:輸入第一操作數,并且還能繼續輸入第一操作數,如輸入第一操作數“12”,并且接著按下“3”、“4”使得第一操作數為“1234”;

Stat2:有第一操作數和操作,如第一操作數“1234”和操作“+”;

Stat3:有第二操作數,如第二操作數“567”;

Stat4:有第一操作數,等待操作碼,即前面計算的結果“1801”放在第一操作數OP1中,等待下一次計算;

Stat5:出錯,如計算溢出導致出錯等。

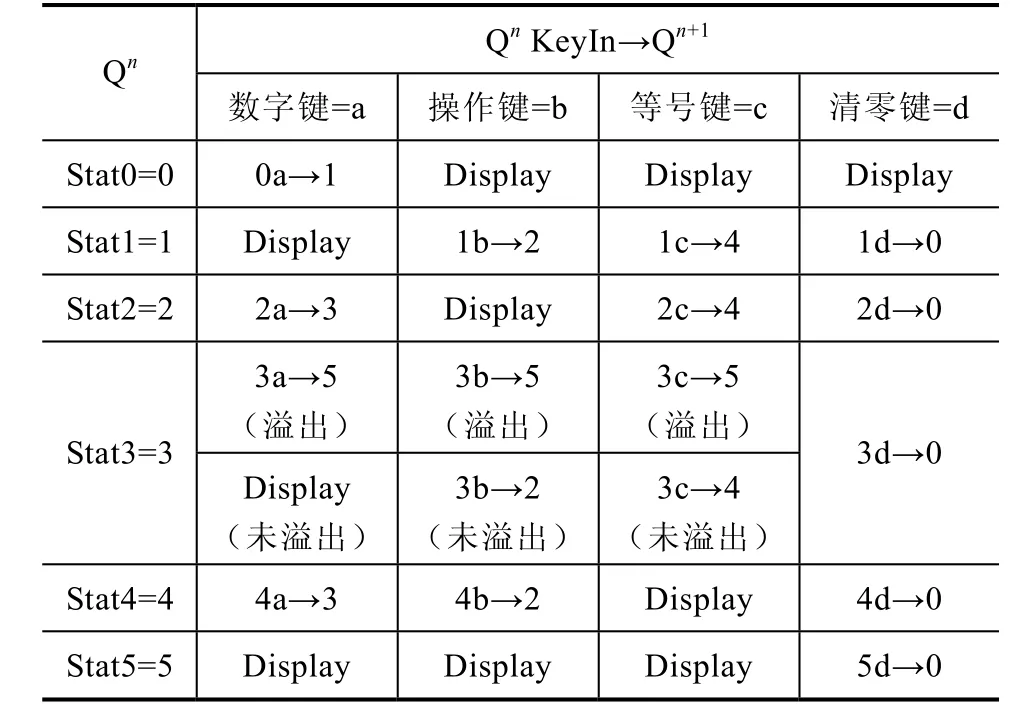

由此得出6個狀態×16個輸入按鍵=96種組合邏輯的情況,但因輸入按鍵的特性可以分為4種按鍵屬性,為了方便表示,可將PLC的I點對應賦值為 0—9數字鍵,10—13分別為+、?、*、/的操作鍵,14為=、15為清零鍵,一共4種按鍵屬性。因此,可以化簡6個狀態×4種按鍵屬性=24種組合邏輯。如表1所示Qn表示現態,Qn+1表示次態,KeyIn表示輸入鍵,Display表示結果顯示。

表1 組合邏輯表

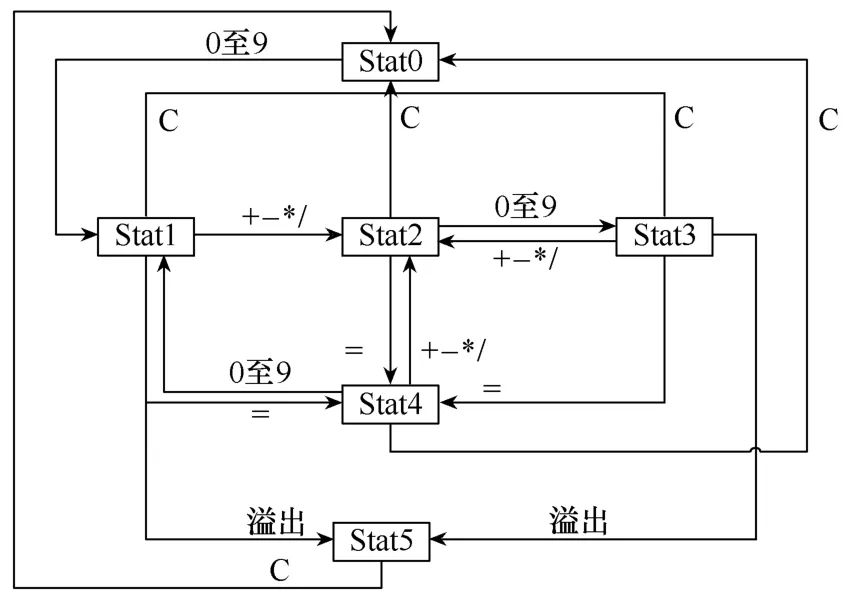

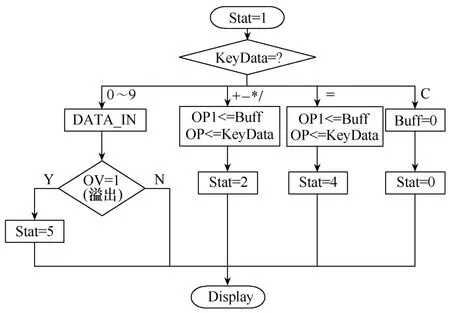

例如,上電初始化后→Stat0→數字鍵→Stat1→操作鍵→Stat2→數字鍵→Stat3→等號鍵→Stat4→計算溢出→Stat5;Stat1、Stat3→輸入溢出→Stat5;Stat1、Stat2、Stat3、Stat4、Stat5→清零鍵 C→Stat0等,其中在輸入操作數的過程中調用DATA_IN。完整的狀態轉換機如圖2所示。

圖2 完整的狀態轉換機

如圖3所示,初始化后根據按鍵KeyIn判斷整個系統的狀態 Stat;根據狀態轉換視圖來分析每個狀態轉換的具體流程圖,如圖4所示的Stat1的具體流程圖;再根據具體流程圖依次寫出PLC梯形圖,最后進行檢查仿真驗證,限于篇幅在此就不詳細列出每個狀態轉換的具體程序。其優化方法在如下方面。

1)多級順序條件控制策略

即將被控對象的控制按照條件分成多級控制,每一級之間都定義有對應的接口。如圖4所示的Stat1的具體流程圖,根據KeyData的值滿足對應的轉移條件時,繼續進行下一步的動作。當出現故障時,可以在相應的控制級別查詢,從而為系統的開發和調試帶來了極大的方便。

圖3 主程序框圖

圖4 Stat1的流程圖

2)狀態機邏輯控制方案

賦予每個狀態一個狀態字如0、1、2等,該狀態字標志著當前系統處于何種狀態。另外,對每個狀態分配專用的狀態查詢單元,當檢測到根據用戶需要或系統運行情況需要改變狀態時,便對狀態位進行操作,修改對應的狀態位,從而通過軟件實現狀態機的切換。

4 西門子S7-GRAPH編程語言結構

在西門子順序功能圖的S7-GRAPH的編程語言結構中,有步、轉換條件、選擇分支、并行分支等結構元素。根據功能將控制任務分解為若干步,其順序用圖形方式顯示出來并且可形成圖形和文本方式的文件[12]。其核心是根據系統邏輯結構分析每一步和步與步之間的轉換條件,其中會根據實際轉換條件相應嵌套選擇分支和并行分支等。

這與有限狀態機理論有異趣同工之效,其核心也是分析狀態集和現態與次態之間的遷移條件,其中也會根據其實際邏輯結構和狀態遷移條件存在多種狀態與并行。

這種基于有限狀態機程序設計的方法與常規的順序控制設計、邏輯控制設計等有一定的關聯性與相似性,但是采用有限狀態機理論的方法使得分析程序的思路更加清晰,設計邏輯更加全面而又嚴格。分析清楚每個狀態與每個輸入之間邏輯關系后,根據所畫的程序流程圖,能因避免其他狀態輸入的干擾而更加快速而完整地編寫梯形圖程序。

5 結論

本文以傳統的PLC設計方法為基礎,并在時序邏輯電路的理論的指導下結合同步時序邏輯電路的分析方法和一般的設計步驟,參考和對比西門子S7-GRAPH編程語言,根據所學知識理解提出一種基于有限狀態機理論的復雜PLC程序設計方法,能夠較為清晰地分析整個PLC系統的所有狀態,避免因為時序邏輯的復雜造成程序編程的混亂,從而有序地編寫每個狀態轉換的程序,并且能在檢查調試時更加方便,使得編程效率大幅度提高,并且能深化加強對S7-GRAPH編程語言學習和理解,達到由淺入深的效果。該方法思路能被有效地運用于到實際工藝控制系統中,有利于系統的維護和程序的擴展與修改。

[1] 鮑金艷, 蔣立軍. 分散控制系統(DCS)和可編程控制器(PLC)應用技術[C]//2010年電站熱工控制研討會暨自動化信息化技術交流年會論文集, 上海, 2010:125-130.

[2] 黃麗晶. 基于 PLC的電梯控制系統設計分析[J]. 電氣技術, 2016, 17(11): 125-132.

[3] 康光華. 電子技術基礎數電部分[M]. 5版. 北京: 高等教育出版社, 2006.

[4] 聶旭中. 狀態機設計研究[J]. 洛陽師范學院學報,2009, 28(2): 96-98.

[5] 張國慶, 霍國義. 有限狀態機設計與實現方法[J].電腦編程技巧與維護, 2001, 12(12): 42-44.

[6] 李帛洋, 趙爭鳴, 檀添, 等. 一種考慮死區與最小脈寬限制的 IPWM 算法[J]. 電工技術學報, 2014,29(12): 11-18.

[7] 黃招彬, 游林儒, 汪兆棟, 等. 后向離散狀態事件驅動電力電子仿真方法[J]. 電工技術學報, 2017,32(12): 42-49.

[8] 齊耀輝. 異步時序邏輯電路分析方法的研究[J]. 現代電子技術, 2008, 31(6): 14-18.

[9] 陳云洽. 脈沖異步時序電路分析與設計中應注意的兩個問題[J]. 電氣電子教學學報, 2001, 23(3):50-52.

[10] 方振同, 梁長飛. PLC控制的剪式液壓舉升機設計[J]. 電氣技術, 2015, 16(12): 128-130, 138.

[11] 張林, 陳洋. 基于西門子 STEP7設計平臺的程序設計[J]. 黑龍江科技信息, 2015, 19(19): 146.

[12] 廖常初. S7-300/400 PLC應用技術[M]. 3版. 北京:機械工業出版社, 2012.